西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第四章 组合逻辑电路

西安邮电学院“校级优秀课程” 3 数字电路与逻辑设计 第四章组合逻辑电路 西失郎重学院

数字电路与逻辑设计 第四章 组合逻辑电路 西安邮电学院“校级优秀课程

第四章组合逻辑电路 目的与要求: 1.掌握组合逻辑电路的定义、特点。 2.掌握组合电路的分析方法和设计方法。 3.掌握常用中规模器件及其应用。 重点与难点: 组合电路的分析和设计方法:

目的与要求: 第四章 组合逻辑电路 1.掌握组合逻辑电路的定义、特点。 2.掌握组合电路的分析方法和设计方法。 3.掌握常用中规模器件及其应用。 重点与难点: 组合电路的分析和设计方法

第四章组合逻辑电路 4.1组合逻辑电路分析 4.2常用组合逻辑电路的介绍 4.3单元级组合逻辑电路的分析方法 4.4组合逻辑电路的设计 4.5组合逻辑电路中的竞争与冒险 ⊙西邹重院

4.1组合逻辑电路分析 4.2常用组合逻辑电路的介绍 4.3单元级组合逻辑电路的分析方法 4.4组合逻辑电路的设计 4.5组合逻辑电路中的竞争与冒险 第四章 组合逻辑电路

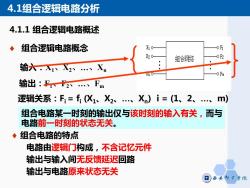

4.1组合逻辑电路分析 4.1.1组合逻辑电路概述 ·组合逻辑电路概念 0 20 组合网路 0F2 输入.X1、X2、Xm An C 输出:、2、 、Fm 逻辑关系:F,=fX1、X2、Xn)i=(1、2、m) 组合电路某一时刻的输出仅与该时刻的输入有关,而与 电路前一时刻的状态无关。 ◆组合电路的特点 电路由逻辑门构成,不含记忆元件 输出与输入间无反馈延迟回路 输出与电路原来状态无关

4.1组合逻辑电路分析 组合逻辑电路概念 输入: 逻辑关系:Fi = fi (X1、X2、.、Xn ) i = (1、2、.、m) 组合电路的特点 电路由逻辑门构成,不含记忆元件 输出与输入间无反馈延迟回路 输出与电路原来状态无关 输出: X1、X2、.、Xn F1、F2、.、Fm 4.1.1 组合逻辑电路概述 组合电路某一时刻的输出仅与该时刻的输入有关,而与 电路前一时刻的状态无关

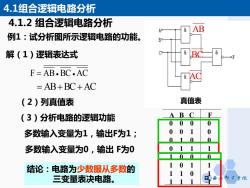

4.1组合逻辑电路分析 4.1.2组合逻辑电路分析 AB 例1:试分析图所示逻辑电路的功能。 B 解(1)逻辑表达式 F=AB.BC.AC =AB+BC+AC (2)列真值表 真值表 (3)分析电路的逻辑功能 AB C 000 0 多数输入变量为1,输出F为1: 001 0 010 0 多数输入变量为0,输出F为0 011 100夏 结论:电路为少数服从多数的 101 11 0 三变量表决电路

例1:试分析图所示逻辑电路的功能。 结论:电路为少数服从多数的 三变量表决电路。 解(1)逻辑表达式 (2)列真值表 A B C F 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 真值表 F = AB• BC • AC (3)分析电路的逻辑功能 多数输入变量为1,输出F为1; 多数输入变量为0,输出 F为0 ABBC AC = AB+BC+AC 4.1.2 组合逻辑电路分析 4.1组合逻辑电路分析

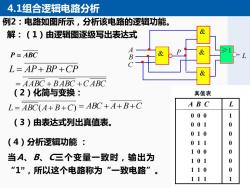

4.1组合逻辑电路分析 例2:电路如图所示,分析该电路的逻辑功能。 解:(1)由逻辑图逐级写出表达式 & P=ABC B L=AP+BP+CP AABC+BABC +CABC (2)化简与变换: 真值表 L=ABC(A+B+C)=ABC+A+B+C ABC 000 1 (3)由表达式列出真值表。 001 0 010 0 (4)分析逻辑功能: 011 0 100 0 当A、B、C三个变量一致时,输出为 101 0 “1”,所以这个电路称为“一致电路”。 110 111

例2:电路如图所示,分析该电路的逻辑功能。 解:(1)由逻辑图逐级写出表达式 (2)化简与变换: (3)由表达式列出真值表。 P = ABC L = AP+ BP +CP = AABC + BABC +CABC L = ABC(A+ B +C) (4)分析逻辑功能 : 当A、B、C三个变量一致时,输出为 “1” ,所以这个电路称为“一致电路” 。 = ABC + A+ B+C 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 A B C 1 0 0 0 0 0 0 1 L 真值表 & & & & A ≥1 B C L P 4.1组合逻辑电路分析

4.2常用组合逻辑电路的介绍 4.2.1加法器 l.半加器(Half Adder) 不考虑低位进位,将两个1位二进制数相加的逻辑运算 ·半加器的真值表 ·逻辑表达式 S=AB+AB C=AB ·逻辑电路图 ·逻辑符号图 逻辑符号图 8西安郭重学院

4.2常用组合逻辑电路的介绍 4.2.1加法器 不考虑低位进位,将两个1位二进制数相加的逻辑运算 • 半加器的真值表 • 逻辑表达式 • 逻辑电路图 1 0 0 0 C 1 1 0 0 1 1 1 0 1 0 0 0 A B S 半加器的真值表 S = AB+ AB C = AB A B =1 & C=AB S = A B 1.半加器(Half Adder) A B S C ∑ • 逻辑符号图 逻辑符号图

4.2常用组合逻辑电路的介绍 2.全加器(Full Adder) 全加器进行加数、被加数和低位来的进位信号的相加 全加器真值表 逻辑表达式 Bi S ABC-+4BC+4BC+4 Ci-1 =A⊕B,⊕C- C=AB,+BC+AC 逻辑符号图 逻辑电路图 ⊙西邹重李院

1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 1 1 0 1 0 0 0 0 0 0 Ai Bi Ci-1 Si Ci 全加器真值表 全加器进行加数、被加数和低位来的进位信号的相加 2.全加器(Full Adder) 1 1 1 1 1 − − − − − = = + + + i i i i i i i i i i i i i i i i A B C S A BC A BC A BC A BC Ci = Ai Bi + Bi Ci−1 + Ai Ci−1 A i B i C i - 1 C i S ∑ i C I C O A i B i =1 & & & C i - 1 =1 S i C i 逻辑符号图 逻辑电路图 逻辑表达式 全加器真值表 4.2常用组合逻辑电路的介绍

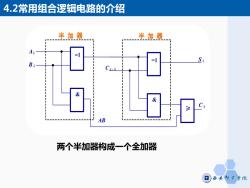

4.2常用组合逻辑电路的介绍 半加器 半加器 两个半加器构成一个全加器

A i B i =1 & AB C i - 1 =1 & ≥ 1 S i C i 半 加 器 半 加 器 两个半加器构成一个全加器 4.2常用组合逻辑电路的介绍

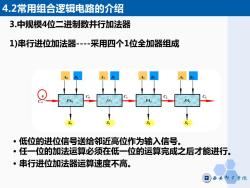

4.2常用组合逻辑电路的介绍 3.中规模4位二进制数并行加法器 1)串行进位加法器-采用四个1位全加器组成 ·低位的进位信号送给邻近高位作为输入信号。 ·任一位的加法运算必须在低一位的运算完成之后才能进行。 串行进位加法器运算速度不高

3.中规模4位二进制数并行加法器 1)串行进位加法器-采用四个1位全加器组成 A0 B0 A1 B1 A2 B2 A3 B3 S0 S1 S2 S3 C-1 0 C0 C1 C2 C3 FA0 FA1 FA2 FA3 • 低位的进位信号送给邻近高位作为输入信号。 • 任一位的加法运算必须在低一位的运算完成之后才能进行。 • 串行进位加法器运算速度不高。 4.2常用组合逻辑电路的介绍

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第三章 集成逻辑门.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第二章 逻辑函数及其简化.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第一章 绪论.ppt

- 《电路》课程教学资源(课后讲稿)第5章 含有运算放大器的电阻电路.pdf

- 《电路》课程教学资源(课后讲稿)第4章 电路定理.pdf

- 《电路》课程教学资源(课后讲稿)第3章 电阻电路的一般分析.pdf

- 《电路》课程教学资源(课后讲稿)第2章 电阻电路的等效变换.pdf

- 《电路》课程教学资源(课后讲稿)第1章 电路模型及定律.pdf

- 《电路》课程教学资源(课后讲稿)第8章 相量法.pdf

- 《电路》课程教学资源(课后讲稿)第6章 储能元件.pdf

- 《电路》课程教学资源(课后讲稿)第9章 正弦稳态电路分析.pdf

- 《电路》课程教学资源(课后讲稿)第7章 一阶电路和二阶电路的时域分析.pdf

- 《电路》课程教学资源(课后讲稿)第12章 三相电路.pdf

- 《电路》课程教学资源(课后讲稿)第11章 电路的频率响应.pdf

- 《电路》课程教学资源(课后讲稿)第10章 含有耦合电感的电路.pdf

- 《电路》课程教学资源(课后讲稿)第16章 二端口网络.pdf

- 《电路》课程教学资源(课后讲稿)第15章 电路方程的矩阵形式.pdf

- 《电路》课程教学资源(课后讲稿)第14章 线性动态电路的复频域分析.pdf

- 《电路》课程教学资源(课后讲稿)第13章 非正弦周期电流电路和信号的频谱.pdf

- 高等教育出版社:《电路》书籍教材PDF电子版(第五版)学习指导与习题分析(共十八章,主编:刘崇新、罗先觉).pdf

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第五章 触发器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(1/2,6.1-6.4).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(2/2,6.5-6.6).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第七章 半导体存储器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第九章 脉冲单元电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc