《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二)

实验四组合逻辑电路的设计(二) 一、实验目的 1.熟悉各种常用MSI组合逻辑电路的功能与使用方法: 2.掌握多片MSI组合逻辑电路的级联、功能扩展: 3.学会使用MSI逻辑器件设计组合电路: 4.进一步培养查找和排除数字电路常见故障的能力。 二、实验器件 1.74LS151八选一数据选择器 2.74LS283四位二进制全加器 三、实验原理 见实验三。 四、设计举例 例:使用全加器实现四位二进制相减。 原理:减去某个二进制数就是加上该数的补码(即反码加“1”),所以二进制 数A和B相加,先将B变为反码,然后与数A相加,并令C1=1,即可。电路如 图4-1示: 图41 例:设计一四变量输入组合逻辑电路。当四个输入中有奇数个高电平“1”时 输出高电平“1”,否则输出低电平“0”。 原理:设输入四变量为DCBA,输出为Y,其真值表入图4一2(a)所示,输 出函数Y为: 001 0111 111 (a)

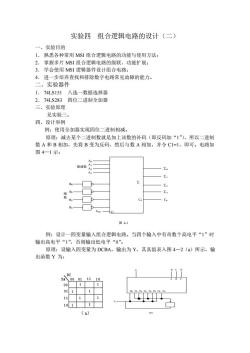

实验四 组合逻辑电路的设计(二) 一、实验目的 1. 熟悉各种常用 MSI 组合逻辑电路的功能与使用方法; 2. 掌握多片 MSI 组合逻辑电路的级联、功能扩展; 3. 学会使用 MSI 逻辑器件设计组合电路; 4. 进一步培养查找和排除数字电路常见故障的能力。 二、实验器件 1. 74LS151 八选一数据选择器 2. 74LS283 四位二进制全加器 三、实验原理 见实验三。 四、设计举例 例:使用全加器实现四位二进制相减。 原理:减去某个二进制数就是加上该数的补码(即反码加“1”),所以二进制 数 A 和 B 相加,先将 B 变为反码,然后与数 A 相加,并令 C1=1,即可。电路如 图 4—1 示: A0 A2 A3 A1 被减数 减 数 B0 B1 B2 B3 VCC C4 C1 C0 ∑ ∑1 ∑2 ∑3 ∑0 图 4-1 例:设计一四变量输入组合逻辑电路。当四个输入中有奇数个高电平“1”时 输出高电平“1”,否则输出低电平“0”。 原理:设输入四变量为 DCBA,输出为 Y,其真值表入图 4—2(a)所示,输 出函数 Y 为: Y B C D A B C D0 D1 D2 D3 D4 D5 D6 D7 • • • A • • • (b)

用八选一数据选择器实现四变量逻辑函数时,以其中3个变量做地址,另外一 个变量做数据。选DCB三变量作为地址,A为数据,画出电路图如图4一2(b): 五、实验内容 1.用八选一数据选择器74LS151设计一个8421BCD非法码检测电路,当输 入为非法码组时,输出为1,否则为零。 2.用全加器实现2位二进制数相乘 六、实验报告要求 1.画出各实验步骤的实验电路逻辑图,并分析实验结果。 2.总结MSI器件的功能及使用方法

用八选一数据选择器实现四变量逻辑函数时,以其中 3 个变量做地址,另外一 个变量做数据。选 DCB 三变量作为地址,A 为数据,画出电路图如图 4—2(b): 五、实验内容 1.用八选一数据选择器 74LS151 设计一个 8421BCD 非法码检测电路,当输 入为非法码组时,输出为 1,否则为零。 2.用全加器实现 2 位二进制数相乘。 六、实验报告要求 1.画出各实验步骤的实验电路逻辑图,并分析实验结果。 2.总结 MSI 器件的功能及使用方法

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第九章 脉冲单元电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第七章 半导体存储器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(2/2,6.5-6.6).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(1/2,6.1-6.4).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第五章 触发器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第三章 集成逻辑门.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第二章 逻辑函数及其简化.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第一章 绪论.ppt

- 《电路》课程教学资源(课后讲稿)第5章 含有运算放大器的电阻电路.pdf

- 《电路》课程教学资源(课后讲稿)第4章 电路定理.pdf

- 《电路》课程教学资源(课后讲稿)第3章 电阻电路的一般分析.pdf

- 《电路》课程教学资源(课后讲稿)第2章 电阻电路的等效变换.pdf

- 《电路》课程教学资源(课后讲稿)第1章 电路模型及定律.pdf

- 《电路》课程教学资源(课后讲稿)第8章 相量法.pdf

- 《电路》课程教学资源(课后讲稿)第6章 储能元件.pdf

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(2/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(1/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十一 电子琴电路设计.doc