西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第七章 半导体存储器

西安邮电学院“校级优秀课程” 电学 数字电路与逻辑设计 第七章半导体存储器 西失郎電学院

数字电路与逻辑设计 第七章 半导体存储器 西安邮电学院“校级优秀课程

第七章半导体存储器 目的与要求: 1、熟悉存储器的一般结构和工作原理。 2、理解各类RAM的存储原理、读写原理及时序。 3、掌握存储单元、字、位、地址、等基本概念以及 存储容量扩展的一般方法。 4、熟悉存储器设计逻辑电路的原理和方法。 重点与难点: 1、存储器的分类及容量的计算。 2、各类RAM的读写及时序分析 3、用ROM设计组合逻辑电路的方法

第七章 半导体存储器 目的与要求: 1、熟悉存储器的一般结构和工作原理。 2、理解各类RAM的存储原理、读写原理及时序。 3、掌握存储单元、字、位、地址、等基本概念以及 存储容量扩展的一般方法。 4、熟悉存储器设计逻辑电路的原理和方法。 重点与难点: 1、存储器的分类及容量的计算。 2、各类RAM的读写及时序分析 3、用ROM设计组合逻辑电路的方法

第七章半导体存储器 7.1概述 7.2随机存取存储器(RAM) 7.3只读存储器(ROM) 7.4存储器的扩展 7.5用ROM实现组合逻辑函 数 ⊙西娄邹重学院

第七章 半导体存储器 7.1 概述 7.2 随机存取存储器(RAM) 7.3 只读存储器(ROM) 7.4 存储器的扩展 7.5 用ROM实现组合逻辑函 数

7.1 概述 半导体存储器的特点与应用 存储器:用以存储二进制信息的器件。 特点:集成度高、可靠性高、外围电路简单且易于接口。 应用:存放程序、数据、资料等。 二、 半导体存储器的分类 按照存储功能划分如下: 存储器 读/写存储器(RA) 只读存储器(ROM) (易朱性) (非易失性) 静态RAM(SRAM) 动态RAM(DRAD 掩模型ROW 可编程RON 可擦可编程ROW 点可擦可编程ROW FLASH (PROM) (EPROM) (EEPROM)

7.1 概述 一、 半导体存储器的特点与应用 二、 半导体存储器的分类 存储器:用以存储二进制信息的器件。 特点:集成度高、可靠性高、外围电路简单且易于接口。 应用:存放程序、数据、资料等。 按照存储功能划分如下: 存储器 读/写存储器(RAM) (易失性) 只读存储器(ROM) (非易失性) 静态RAM(SRAM) 动态RAM(DRAM) 掩模型ROM 可编程ROM (PROM) 可擦可编程ROM (EPROM) 点可擦可编程ROM (EEPROM) FLASH

7.1概述 三、半导体存储器的主要技术指标 1.存储容量: 存储器所能存放信息的多少,存储容量越大则存储的信息 越多,系统的功能越强。 用位(bt)表示存储器容量,位数即存储器所需要的单元数。 用字节(byte)或者字节的倍数,表示存储容量。 2读写参数: 存储器的读写参数是存储器最重要的参数之一,只有按 照严格的时序对存储器进行读写,才能保证存储器的工 作正确。 写入时间:从提出写请求到最终把数据写入到存储器 之间的时间间隔; 读出时间:从提出读请求到数据在输出端上数据有效 之间的时间间隔;

7.1 概述 三、 半导体存储器的主要技术指标 1.存储容量: 存储器所能存放信息的多少,存储容量越大则存储的信息 越多,系统的功能越强。 用位(bit)表示存储器容量,位数即存储器所需要的单元数。 用字节(byte)或者字节的倍数 ,表示存储容量。 2 读写参数: 存储器的读写参数是存储器最重要的参数之一,只有按 照严格的时序对存储器进行读写,才能保证存储器的工 作正确。 写入时间:从提出写请求到最终把数据写入到存储器 之间的时间间隔; 读出时间:从提出读请求到数据在输出端上数据有效 之间的时间间隔;

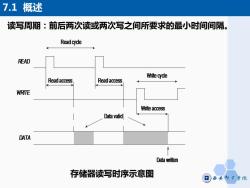

7.1概述 读写周期:前后两次读或两次写之间所要求的最小时间间隔。 Read cyde READ Write cyde Read access Read access WRTE Write access Data valid DATA Da他written 存储器读写时序示意图

7.1 概述 读写周期:前后两次读或两次写之间所要求的最小时间间隔。 存储器读写时序示意图

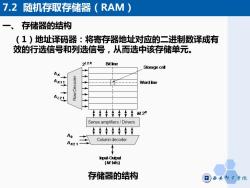

7.2 随机存取存储器(RAM) 存储器的结构 (1)地址译码器:将寄存器地址对应的二进制数译成有 效的行选信号和列选信号,从而选中该存储单元。 2L2K Bit line Storage cell AK AK11 Word iine 李↑专李卡M2* Sense amplifiers/Drivers Ao Column decoder AK21 Iinput-Oulput (M bits) 存储器的结构 ⊙西邹重孝院

7.2 随机存取存储器(RAM) 一、 存储器的结构 (1)地址译码器:将寄存器地址对应的二进制数译成有 效的行选信号和列选信号,从而选中该存储单元。 存储器的结构

7.2 随机存取存储器(RAM) (2)存储单元 存储矩阵由许多存储单元排列组成,每个存储单元存 放一位二值信息。 水平选择线可以选择一行单元,称为字线(Wod Iine,也称为数据线),而把一列单元连接到输出电 路的线称为位线(bit line)。 (3)片选与读写控制电路 数字系统中的RAM一般要由多片组成,而系统每次读 /写时,只针对其中的一片或几片,因此还应加片选信 号 读/写控制信号用于对电路工作状态进行控制。 R/币=0时,执行写操作; R/W=1时,执行读操作

7.2 随机存取存储器(RAM) (2)存储单元 数字系统中的RAM一般要由多片组成,而系统每次读 /写时,只针对其中的一片或几片,因此还应加片选信 号 。 (3)片选与读写控制电路 水平选择线可以选择一行单元,称为字线(Word line,也称为数据线),而把一列单元连接到输出电 路的线称为位线(bit line)。 存储矩阵由许多存储单元排列组成,每个存储单元存 放一位二值信息。 读/写控制信号用于对电路工作状态进行控制。 R/W = 0 时,执行写操作; R/W =1 时,执行读操作

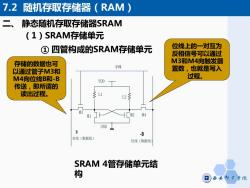

7.2 随机存取存储器(RAM) 二、静态随机存取存储器SRAM (1)SRAM存储单元 ①四管构成的SRAM存储单元 位线上的一对互为 反相信号可以通过 存储的数据也可 M3和M4向触发器 字线 以通过管子M3和 置数,也就是写入 M4向位线B和-B 过程。 VDD 传送,即所谓的 读出过程。 L23 M3 2 M4 GND -B 位线(数据线) 位线(数据线) SRAM4管存储单元结 构 ⊙西长郭重学院

7.2 随机存取存储器(RAM) 二、 静态随机存取存储器SRAM (1)SRAM存储单元 ① 四管构成的SRAM存储单元 L1 L2 VDD M3 M4 M1 M2 GND 位线(数据线) B 字线 位线(数据线) -B SRAM 4管存储单元结 构 位线上的一对互为 反相信号可以通过 M3和M4向触发器 置数,也就是写入 过程。 存储的数据也可 以通过管子M3和 M4向位线B和-B 传送,即所谓的 读出过程

7.2 随机存取存储器(RAM) ②六管构成的SRAM存储单元 解决了4T-SRAM存储单元的静态功耗问题。 CMOS结构提高了存储的可靠性和抗干扰能力。 M5 M6 两个反相器 2 (M1,M5和 M2,M6构成两只 GND 反向器)组成的反 馈环路。 B -B 6T-SRAM CMOS 电路

7.2 随机存取存储器(RAM) ② 六管构成的SRAM存储单元 6T-SRAM CMOS 电路 GND B -B WL M1 M2 M3 M4 M5 M6 a b 两个反相器 (M1,M5和 M2,M6构成两只 反向器)组成的反 馈环路。 解决了4T-SRAM存储单元的静态功耗问题。 CMOS结构提高了存储的可靠性和抗干扰能力

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(2/2,6.5-6.6).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(1/2,6.1-6.4).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第五章 触发器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第三章 集成逻辑门.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第二章 逻辑函数及其简化.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第一章 绪论.ppt

- 《电路》课程教学资源(课后讲稿)第5章 含有运算放大器的电阻电路.pdf

- 《电路》课程教学资源(课后讲稿)第4章 电路定理.pdf

- 《电路》课程教学资源(课后讲稿)第3章 电阻电路的一般分析.pdf

- 《电路》课程教学资源(课后讲稿)第2章 电阻电路的等效变换.pdf

- 《电路》课程教学资源(课后讲稿)第1章 电路模型及定律.pdf

- 《电路》课程教学资源(课后讲稿)第8章 相量法.pdf

- 《电路》课程教学资源(课后讲稿)第6章 储能元件.pdf

- 《电路》课程教学资源(课后讲稿)第9章 正弦稳态电路分析.pdf

- 《电路》课程教学资源(课后讲稿)第7章 一阶电路和二阶电路的时域分析.pdf

- 《电路》课程教学资源(课后讲稿)第12章 三相电路.pdf

- 《电路》课程教学资源(课后讲稿)第11章 电路的频率响应.pdf

- 《电路》课程教学资源(课后讲稿)第10章 含有耦合电感的电路.pdf

- 《电路》课程教学资源(课后讲稿)第16章 二端口网络.pdf

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第九章 脉冲单元电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(2/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(1/2).doc