《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用

实验六小规模SSI计数器及其应用 一、实验目的 1.熟悉触发器的逻辑功能: 2.掌握小规模时序逻辑电路的设计方法、安装及调试: 3.学会用状态转换表、状态转换图和时序图来描述时序逻辑电路的逻辑功能。 二、实哈器件 1.74LS76双JK触发器 2.74LS74双上升沿D触发器 3.74S00四2输入与非门 4.74LS04六反向器 三、实验原理 1.SSI时序逻辑电路设计原则和步骤: SSI时序逻辑电路设计原则是:当选用小规模集成电路时,所用的触发器和逻辑 门电路的数目应最少,而且触发器和逻辑门电路输入端数目也应为最少,所设计出 的逻辑电路应力求最简,并尽量采用同步系统。 设计步骤如下: (1)逻辑抽象。.分析给定的逻辑问题、确定输入变量、输出变量以及电路的状 态数:b.定义输入、输出逻辑状态的含意,并将电路状态顺序编号:c.按照题意列 出状态转换图或状态转换表。这样,就能把给定的逻辑问题抽象为一个时序逻辑函 数来描述。 (2)状态化简。状态化简的目的就在于将等价状态尽可能合并,以得出最简的状 态转换图。 (③)状态编码。时序逻辑电路的状态是用触发器状态的不同组合来表示的。因此 首先要确定触发器的数目n,因此n个触发器共有2种状态组合,所以获得M个状态 组合,必需取2<M≤2”,每组触发器的状态组合都是一组二值代码,称状态编码。 为便于记忆和识别,一般选用的状态编码都遵循一定的规律。 (④)选定触发器的类型并求出状态方程、驱动方程和输出方程。不同逻辑功能的 触发器驱动方式不同,所以用不同类型触发器设计出的电路也不同。因此,在设计 具体电路前必须根据需要选定触发器的类型。 (⑤)根据驱动方程和输出方程画出逻辑电路图。 (6)检查设计的电路能否自启动。 2.应用举例 例1:设计一个带有进为输出端的六进制计数器。 (1)逻辑抽象,得出状态图 取进位信号为输出逻辑变量C0,逻辑变量C0,同时规定有进位输出时C0=1 无进位输出时C0=0,六进制计数器应该有6个状态S~S,即可画出如图6-1 所示的电路状态转换图

实验六 小规模 SSI 计数器及其应用 一、 实验目的 1.熟悉触发器的逻辑功能; 2.掌握小规模时序逻辑电路的设计方法、安装及调试; 3.学会用状态转换表、状态转换图和时序图来描述时序逻辑电路的逻辑功能。 二、 实验器件 1.74LS76 双 JK 触发器 2.74LS74 双上升沿 D 触发器 3.74LS00 四 2 输入与非门 4.74LS04 六反向器 三、 实验原理 1. SSI 时序逻辑电路设计原则和步骤: SSI时序逻辑电路设计原则是:当选用小规模集成电路时,所用的触发器和逻辑 门电路的数目应最少,而且触发器和逻辑门电路输入端数目也应为最少,所设计出 的逻辑电路应力求最简,并尽量采用同步系统。 设计步骤如下: (1) 逻辑抽象。a.分析给定的逻辑问题、确定输入变量、输出变量以及电路的状 态数; b.定义输入、输出逻辑状态的含意,并将电路状态顺序编号; c.按照题意列 出状态转换图或状态转换表。这样,就能把给定的逻辑问题抽象为一个时序逻辑函 数来描述。 (2) 状态化简。状态化简的目的就在于将等价状态尽可能合并,以得出最简的状 态转换图。 (3) 状态编码。时序逻辑电路的状态是用触发器状态的不同组合来表示的。因此, 首先要确定触发器的数目n,因此n个触发器共有2 n种状态组合,所以获得M 个状态 组合,必需取 2 n-1<M≤2n ,每组触发器的状态组合都是一组二值代码,称状态编码。 为便于记忆和识别,一般选用的状态编码都遵循一定的规律。 (4)选定触发器的类型并求出状态方程、驱动方程和输出方程。不同逻辑功能的 触发器驱动方式不同,所以用不同类型触发器设计出的电路也不同。因此,在设计 具体电路前必须根据需要选定触发器的类型。 (5)根据驱动方程和输出方程画出逻辑电路图。 (6)检查设计的电路能否自启动。 2. 应用举例 例 1:设计一个带有进为输出端的六进制计数器。 (1) 逻辑抽象,得出状态图 取进位信号为输出逻辑变量 CO,逻辑变量 CO,同时规定有进位输出时 CO=1, 无进位输出时 CO=0,六进制计数器应该有 6 个状态 S0~S5,即可画出如图 6-1 所示的电路状态转换图

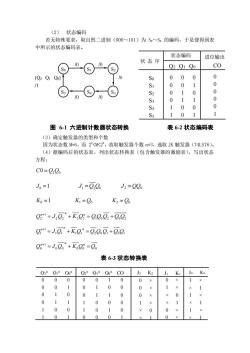

(2)状态编码 若无特殊要求,取自然二进制(000~101)为S,~S:的编码,于是便得到表 中所示的状态编码表。 状态编码 进位输出 状态序 Q2 Q1 Qo (Q2Q1Q0)1 0 0 0 0 0 0 S2 0 0 0 1 0 S4 0 0 S5 0 1 1 图6-1六进制计数器状态转换 表6-2状态编码表 (3)确定触发器的类型和个数 因为状态数M=6,而2<M<2,故取触发器个数n=3,选取JK触发器(74LS76)。 (4)据编码后的状态表,列出状态转换表(包含触发器的激励表),写出状态 方程: C0=Q2 Jo=1 J=0.00 J2=Q0 K=1 KI=C K2=Q0 Q=J,g”+K,Q=Q,0g+Qg 0=Jg”+K0,"-00g+Qg, Q1=J2”+K26=Q 表6-3状态转换表 O2O OoO2O Oo CO J2 K2 Kn 000 0 0 0 0 0 0 0 0

(2) 状态编码 若无特殊要求,取自然二进制(000~101)为 S0~S5 的编码,于是便得到表 中所示的状态编码表。 (3)确定触发器的类型和个数 因为状态数 M=6,而 2 2 <M<23,故取触发器个数 n=3,选取 JK 触发器(74LS76)。 (4)据编码后的状态表,列出状态转换表(包含触发器的激励表),写出状态 方程: C0 = Q2Q0 J 0 =1 1 Q2Q0 J = 2 QQ0 J = K0 =1 K1 = Q0 K2 = Q0 2 2 2 2 1 0 2 0 2 1 Q2 J Q K Q Q Q Q Q Q n n n = + = + + 1 1 1 1 2 0 1 0 1 1 Q1 J Q K Q Q Q Q Q Q n n n = + = + + 0 0 0 0 0 1 Q0 J Q K Q Q n n n = + = + (Q2 Q1 Q0) /1 /CO 图 6-1 六进制计数器状态转换 图 /0 /0 /0 /0 /0 S0 S1 S2 S5 S4 S3 状态序 号 状态编码 进位输出 Q 2 Q1 Q0 CO S0 S1 S2 S3 S4 S5 0 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 表 6-2 状态编码表 Q2 n Q1 n Q0 n J2 K2 J1 K1 Q2 J0 K0 n Q1 n Q0 n CO 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 0 1 0 × 0 × 0 × 1 × × 0 × 1 0 × 1 × × 0 × 1 0 × 0 × 1 × × 1 1 × × 1 1 × × 1 表 6-3 状态转换表

(5)由驱动方程和状态方程画出六进制计数器的逻辑图,如图6-4. (6)检查电路能否自启动。 将有效循环之外的2个状态110和111分别代入上式状态方程中计算,所得 次态对应为111和000,故电路能自启动。如图6-4是电路完整的路完整的状态转 换图状态转换图: 图64六进制计数器的逻辑图 (7)校核 ⊙-⊙-⊙°⊙” (Q2 Q:Qo) 11 S; 图6-5六进制计数器完整状态转换图 四、实验内容 1试用JK触发器和门电路设计一个同步带有借位输出端的1位十进制减法计数器 2.试用D触发器和门电路设计1个4位扭环形计数器,并能自启动。状态转换图如 下: @-⊙-⊙ (Qo Q:Q2 Q3) ⊙-@-@ 题6.2图

(5)由驱动方程和状态方程画出六进制计数器的逻辑图,如图 6-4. (6)检查电路能否自启动。 将有效循环之外的 2 个状态 110 和 111 分别代入上式状态方程中计算,所得 次态对应为 111 和 000,故电路能自启动。如图 6-4 是电路完整的路完整的状态转 换图状态转换图: J Q Q K SET CLR J Q Q K SET CLR J Q Q K SET CLR 0 & 0 0 0 & 0 0 0 & 0 • 0 • • • • • CP +5V Q0 Q1 Q2 • • 图6-4 六进制计数器的逻辑图 CP Q2 CO (7)校核 四、 实验内容 1.试用JK触发器和门电路设计一个同步带有借位输出端的1位十进制减法计数器。 2.试用 D 触发器和门电路设计 1 个 4 位扭环形计数器,并能自启动。状态转换图如 下: /1 /0 /0 /0 /0 S6 S7 S0 S1 S2 S5 S4 S3 图 6-5 六进制计数器完整状态转换图 /0 (Q2 Q1 Q0) /CO 题 6.2 图 0000 1000 1100 1110 1111 0001 0011 0111 1101 1010 0100 1001 0010 0101 1011 0110 (Q0 Q1 Q2 Q3)

3.试用K触发器和门电路设计带有控制变量X的计数器,当X=0时为三进制 计数器,当X=1时为四进制计数器,设置1为进位输出端C0。 五、实验报告 总结SSI同步时序电路设计思路。 六、思考题 在设计时序逻辑电路时如何处理各触发器的置“0”端子R和置“1”端子S。 2。如果设计的时序电路不能自启动应该如何处理?

3. 试用 JK 触发器和门电路设计带有控制 变量 X 的计数器,当 X=0 时为三进制 计数器,当 X=1 时为四进制计数器,设置 1 为进位输出端 CO。 五、 实验报告 总结 SSI 同步时序电路设计思路。 六、 思考题 1. 在设计时序逻辑电路时如何处理各触发器的置“0”端子 RD 和置“1”端子 SD。 2. 如果设计的时序电路不能自启动应该如何处理?

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第九章 脉冲单元电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第七章 半导体存储器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(2/2,6.5-6.6).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(1/2,6.1-6.4).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第五章 触发器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第三章 集成逻辑门.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第二章 逻辑函数及其简化.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第一章 绪论.ppt

- 《电路》课程教学资源(课后讲稿)第5章 含有运算放大器的电阻电路.pdf

- 《电路》课程教学资源(课后讲稿)第4章 电路定理.pdf

- 《电路》课程教学资源(课后讲稿)第3章 电阻电路的一般分析.pdf

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(2/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(1/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十一 电子琴电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十二 移位相加8位乘法器电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计二 数字抢答器的设计.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计四 数字电子密码锁.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计一 自动交通控制系统.doc