《数字电路与逻辑设计》课程实验指导(实验设计)设计一 自动交通控制系统

1自动交通控制系统 随着微电子技术的迅猛发展,可编程逻辑器件从20世纪70年代发展至今,其 结构、工艺、集成度、功能、速度、性能等方面都在不断改进和提高:另外,电子 设计自动化EDA技术的发展又为可编程逻辑器件的广泛应用提供了有力的工具。 目前,在数字系统设计中可以借助EDA工具通过软件编程对可编程逻辑器件的硬 一体结物和二作南式选行要鹅的这球使得硬件设计具有软件设计的灵活性和馒携性 可编程逻辑器件EPM7O32,在MAX+PusⅡ开发环境 下采用VHDL语言以及ByteBlaster在线可编程技术来实现自动交通控制系统的方 法。该设计中采用的自顶向下的设计方法同样适用于复杂数字系统的设计。 一、设计任务 在一个具有主、支干道的十字路口,设计一个交通灯自动控制装置。要求 1)主干道经常保持畅通, 支干道亮红灯 2)如果主干道无车,支干道有车,则允许支干道通行,主干道亮红灯,支干道亮绿 灯。 3)如果主干道和支干道均有车要求通行,则两者应交替通行,并要求主干道每 次通行30秒钟,支干道每次通行20秒钟」 4)每次绿灯变红灯时,黄灯应先亮5秒钟。 二、 EPM7032器件的结构和性能特点 1、EPM7032器件的结构 可编程逻辑器件EPM7032是基于Altera公司第二代多阵列矩阵(MAX)结构, 并采用先进的CMOS EEPROM技术制造的。该器件由逻辑阵列块(LAB)、可编程 车线阵列(A)和O控制块笔部分组成。其结构如图1所示。 8t: :8 8to16 8: :8 8to1 8to16 图1 EPM7032器件结构框图

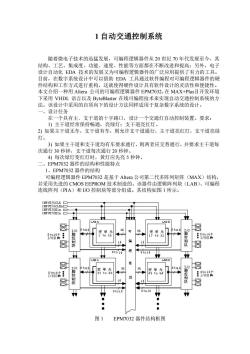

1 自动交通控制系统 随着微电子技术的迅猛发展,可编程逻辑器件从 20 世纪 70 年代发展至今,其 结构、工艺、集成度、功能、速度、性能等方面都在不断改进和提高;另外,电子 设计自动化 EDA 技术的发展又为可编程逻辑器件的广泛应用提供了有力的工具。 目前,在数字系统设计中可以借助 EDA 工具通过软件编程对可编程逻辑器件的硬 件结构和工作方式进行重构,这就使得硬件设计具有软件设计的灵活性和便捷性。 本文介绍一种用 Altera 公司的可编程逻辑器件 EPM7032,在 MAX+PlusⅡ开发环境 下采用 VHDL 语言以及 ByteBlaster 在线可编程技术来实现自动交通控制系统的方 法。该设计中采用的自顶向下的设计方法同样适用于复杂数字系统的设计。 一、设计任务 在一个具有主﹑支干道的十字路口,设计一个交通灯自动控制装置。要求: 1) 主干道经常保持畅通,亮绿灯;支干道亮红灯。 2) 如果主干道无车,支干道有车,则允许支干道通行,主干道亮红灯,支干道亮绿 灯。 3) 如果主干道和支干道均有车要求通行,则两者应交替通行,并要求主干道每 次通行 30 秒钟,支干道每次通行 20 秒钟。 4) 每次绿灯变红灯时,黄灯应先亮 5 秒钟。 二、EPM7032 器件的结构和性能特点 1、EPM7032 器件的结构 可编程逻辑器件 EPM7032 是基于 Altera 公司第二代多阵列矩阵(MAX)结构, 并采用先进的 CMOS EEPROM 技术制造的。该器件由逻辑阵列块(LAB)、可编程 连线阵列(PIA)和 I/O 控制块等部分组成。其结构如图 1 所示。 图 1 EPM7032 器件结构框图

每个逻辑阵列块由16个宏单元阵列组成,多个逻辑阵列块通过可编程连线阵列 连接在一起。PIA全局总线由所有的专用输入、IO引脚以及宏单元馈给信号。 EPM7032的宏单元可以单独地配置成时序逻辑或组合逻辑工作方式。每个宏单元又 由罗辑阵列、乘积项选择矩阵和可编程寄存器等二个功能块组成。 通过可编程连线阵列可把各个LAB相互连接构成所需的逻辑。通过在PIA上布 线,可把器件中任一信号源连接到其目的地。 I/O控制块允许每个I/O引脚单独地配置为输入、输出和双向工作方式。所有1/O 引脚都有一个三态缓冲器。它们由两个专用的低电平有效的输出使能引脚OE1和 0P)来控制 2、EPM7032器件的性能特点 可编程逻辑器件EPM7032主要有如下特点: 逻辑密度为600个可用门: ●EPM7032器件可100%模仿TTL,并可将SSI、MSI和LSI的逻辑功能高密度的 集成,它也可以集成多种可编程逻辑器件,其范围从PAL、GAL、22VI0到MACH 和PLSI器件 引脚到引脚的逻辑延迟为5.0s,计数器工作频率达178.6MHz: 可编程宏单元触发器具有专用清除、置位、时钟和时钟使能控制: ● 可编程的扩展乘积项分配,允许向每个宏单元提供多达32个乘积项: ● 电源电压为3.3v或5.0v: 遵 PCI规定 EPM7O32器件采用CMOS EEPROM单元实现逻辑功能,此种用户可编程的结 构可实现各种各样的、独立的组合逻辑和时序逻辑功能,在设计开发和调试阶 段,可快速而有效地对该器件反复编程: ● 可通过TAG接口实现在线编程,并保证可编程擦除1O0次以上: 可编程保密位,全面保护专利设计: Altera公司的MAX+PLUS IⅡ(Multiple Array Matrix and Programmable Logic User System)开发系统对该器件提供软件设计支持。 三、自动交通控制系统的设计与实现 1、自动交通控制系统的设计 本设计采用自顶向下(TOP-TO-DOWN)的设计方法。该方法是一种从抽象定义 到具体的实现, 从高层次到低 层次逐步求精的分层次、分模 块的设计方法,它是数字系统 定时器 中最常用的一种方法,也是基 于复杂可编程器件进行系统设 er c 计的主要方法。 设计者首先从 时钟电略1业 整体上规划整个 系统的功能和 拉制 性能,然后对系统进行划分, 传感器 分解为规模较小、功能较为信 单的局部模块,并确定他们之 间的相互关系,这种划分过程 可以不断地进行下去, 直到划 分得到的单元可以映射到物理 图2系统框图

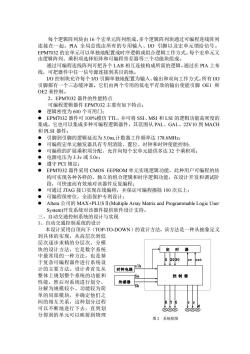

g R Y G r y clk 5 20 30 cr cnt 定 时 器 Sa Sb 控 制 器 时钟电路 传感器 图 2 系统框图 每个逻辑阵列块由 16 个宏单元阵列组成,多个逻辑阵列块通过可编程连线阵列 连接在一起。PIA 全局总线由所有的专用输入、I/O 引脚以及宏单元馈给信号。 EPM7032 的宏单元可以单独地配置成时序逻辑或组合逻辑工作方式。每个宏单元又 由逻辑阵列、乘积项选择矩阵和可编程寄存器等三个功能块组成。 通过可编程连线阵列可把各个 LAB 相互连接构成所需的逻辑。通过在 PIA 上布 线,可把器件中任一信号源连接到其目的地。 I/O 控制块允许每个 I/O 引脚单独地配置为输入、输出和双向工作方式。所有 I/O 引脚都有一个三态缓冲器。它们由两个专用的低电平有效的输出使能引脚 OE1 和 OE2 来控制。 2、EPM7032 器件的性能特点 可编程逻辑器件 EPM7032 主要有如下特点: ⚫ 逻辑密度为 600 个可用门; ⚫ EPM7032 器件可 100%模仿 TTL,并可将 SSI、MSI 和 LSI 的逻辑功能高密度的 集成,它也可以集成多种可编程逻辑器件,其范围从 PAL、GAL、22V10 到 MACH 和 PLSI 器件; ⚫ 引脚到引脚的逻辑延迟为 5.0ns,计数器工作频率达 178.6MHz; ⚫ 可编程宏单元触发器具有专用清除、置位、时钟和时钟使能控制; ⚫ 可编程的扩展乘积项分配,允许向每个宏单元提供多达 32 个乘积项; ⚫ 电源电压为 3.3v 或 5.0v; ⚫ 遵守 PCI 规定; ⚫ EPM7032 器件采用 CMOS EEPROM 单元实现逻辑功能,此种用户可编程的结 构可实现各种各样的、独立的组合逻辑和时序逻辑功能,在设计开发和调试阶 段,可快速而有效地对该器件反复编程; ⚫ 可通过 JTAG 接口实现在线编程,并保证可编程擦除 100 次以上; ⚫ 可编程保密位,全面保护专利设计; ⚫ Altera 公司的 MAX+PLUSⅡ(Multiple Array Matrix and Programmable Logic User System)开发系统对该器件提供软件设计支持。 三、自动交通控制系统的设计与实现 1、自动交通控制系统的设计 本设计采用自顶向下(TOP-TO-DOWN)的设计方法。该方法是一种从抽象定义 到具体的实现,从高层次到低 层次逐步求精的分层次、分模 块的设计方法,它是数字系统 中最常用的一种方法,也是基 于复杂可编程器件进行系统设 计的主要方法。设计者首先从 整体上规划整个系统的功能和 性能,然后对系统进行划分, 分解为规模较小、功能较为简 单的局部模块,并确定他们之 间的相互关系,这种划分过程 可以不断地进行下去,直到划 分得到的单元可以映射到物理

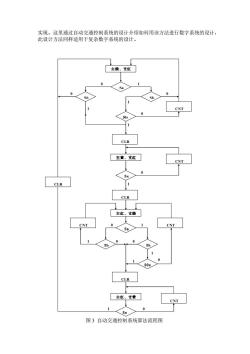

实现。这里通过自动交通控制系统的设计介绍如何用该方法进行数字系统的设计, 此设计方法同样适用于复杂数字系统的设计。 红、支 图3自动交通控制系统算法流程图

实现。这里通过自动交通控制系统的设计介绍如何用该方法进行数字系统的设计, 此设计方法同样适用于复杂数字系统的设计。 图 3 自动交通控制系统算法流程图 0 0 1 0 1 1 1 0 0 1 主红﹑支绿 主红﹑支黄 CLR CNT CNT CNT CNT CLR CLR 0 0 1 0 0 主黄﹑支红 CNT CLR 主绿﹑支红 Sa Sb 30s Sb 1 1 1 5s Sa Sb Sb 20s 0 5s 1

十字路口的交通灯指挥着行人和各种车辆安全运行。实现交通灯的自动指挥是 城市交通管理自动化的重要课题。本次设计的自动交通控制系统的工作过程是: 般情况下,如果主干道和支干道均无车辆要求通行,应该保证主干道绿灯亮,支干 支干道均有车辆要求通行,则应先保证主干道通行30秒钟后,才 允许支干道通有 在允许支干道车辆通行前,应先使主干道黄灯亮5秒钟,支干道红灯保持:5秒钟 后,才变成主干道红灯亮,支干道绿灯亮。在支干道保持畅通时,若主干道无车辆 要求通行,则支干道始终保持畅通:如果此时支干道无车辆要求通行,则应立刻准 备使主干道通车,支干道禁止通行:若此时主干道有车辆要求通行,并且支干道通 行时间己超过0秒钟,则应该准备使主干道通行。在允许主干道通行前,应先使支 道的黄灯亮5秒钟,主干道红灯保持:5秒钟后,变成主干道绿灯亮,支干道红 灯亮。 据此工作过程,可得系统框图,如图2所示。其中传感器部分的作用是:通过 在主干道和支干道上所设的传感器,可以检测到主、支干道上是否有车辆要求通过 十字路口。主支干道上的传感器发出的信号分别用Sa和Sb表示, Sa和Sh为1 表示有车辆要求通行 否则无车辆通行 要求。时钟电路为系统提供 个稳定 秒脉冲信号,以供计时和系统的同步控制。定时器电路在控制器提供的计时信号c 和清零信号c的作用下完成定时功能,并向控制器提供5秒钟、20秒钟和30秒钟 的计时信号。控制器的设计是本系统的核心,控制器的作用是:根据传感器和定时 器提供的信号,判断、调整和控制整个系统的状态,并控制定时电路工作,提供适 当的灯光控制信号 其中控制主、 黄、绿灯的信号分别用 和r、y、g表示: 其值为1'表示灯亮, 为0表示火 自动交通控制系统实际上是一个控制型的数字系统,根据其工作过程可以得出 该系统的详细算法流程图。如图3所示。 2、自动交通控制系统的实现 木设计利知用A1t ra公司的MAX+PlusⅡ软件工具。MAX+PLUSⅡ是一种集设计 输入 编译 仿真 综合、 器 牛编程等功能 体的完全集成化 易学易用 的可编程逻辑设计软件。该软件允许设计人员自由选择设计进入的方法和工具,设 计人员无需详细了解器件内部的复杂结构,只需选择自己熟悉的设计方法和 工具,就可进行设计输入。该软件提供了一种真正与结构无关的可编程逻辑设计环 境,它支持不同结构的器件,如FLEX、MAX及CLASSIC系列器件等。 根据设计要求, 很容易设计出VHDL源文件。VHDL源文件如下 LIBRARYIEEE: USE IEEE.STD_LOGIC_1164.ALL: ENTITY controller IS PORT(clk, Sa.Sh:IN STD LOGIC G, r,y,g: OUT STD _LOGIC): END controller; ARCHITECTURE xcontrol OF controller IS TYPE states IS(s0,sl,s2,s3); SIGNAL state: states SIGNAL leda STD_LOGIC_VECTOR(2DOWNTOO): SIGNAL ledb:STD_LOGIC_VECTOR(2DOWNTO0); BEGIN

十字路口的交通灯指挥着行人和各种车辆安全运行。实现交通灯的自动指挥是 城市交通管理自动化的重要课题。本次设计的自动交通控制系统的工作过程是:一 般情况下,如果主干道和支干道均无车辆要求通行,应该保证主干道绿灯亮,支干 道红灯亮。此时,若支干道有车辆要求通行,则应允许支干道车辆通行;若主干道 ﹑支干道均有车辆要求通行,则应先保证主干道通行 30 秒钟后,才允许支干道通行。 在允许支干道车辆通行前,应先使主干道黄灯亮 5 秒钟,支干道红灯保持;5 秒钟 后,才变成主干道红灯亮,支干道绿灯亮。在支干道保持畅通时,若主干道无车辆 要求通行,则支干道始终保持畅通;如果此时支干道无车辆要求通行,则应立刻准 备使主干道通车,支干道禁止通行;若此时主干道有车辆要求通行,并且支干道通 行时间已超过 20 秒钟,则应该准备使主干道通行。在允许主干道通行前,应先使支 干道的黄灯亮 5 秒钟,主干道红灯保持;5 秒钟后,变成主干道绿灯亮,支干道红 灯亮。 据此工作过程,可得系统框图,如图 2 所示。其中传感器部分的作用是:通过 在主干道和支干道上所设的传感器,可以检测到主﹑支干道上是否有车辆要求通过 十字路口。主支干道上的传感器发出的信号分别用 Sa 和 Sb 表示,Sa 和 Sb 为‘1’, 表示有车辆要求通行;否则无车辆通行要求。时钟电路为系统提供一个稳定的 clk 秒脉冲信号,以供计时和系统的同步控制。定时器电路在控制器提供的计时信号 cnt 和清零信号 cr 的作用下完成定时功能,并向控制器提供 5 秒钟﹑20 秒钟和 30 秒钟 的计时信号。控制器的设计是本系统的核心,控制器的作用是:根据传感器和定时 器提供的信号,判断﹑调整和控制整个系统的状态,并控制定时电路工作,提供适 当的灯光控制信号。其中控制主﹑只干道上红﹑黄﹑绿灯的信号分别用 R﹑Y﹑G 和 r﹑y﹑g 表示;其值为‘1’表示灯亮,为‘0’表示灯灭。 自动交通控制系统实际上是一个控制型的数字系统,根据其工作过程可以得出 该系统的详细算法流程图。如图 3 所示。 2、自动交通控制系统的实现 本设计利用 Altera 公司的 MAX+PlusⅡ软件工具。MAX+PLUSⅡ是一种集设计 输入﹑编译、仿真、综合、器件编程等功能于一体的完全集成化﹑易学易用 的可编程逻辑设计软件。该软件允许设计人员自由选择设计进入的方法和工具,设 计人员无需详细了解器件内部的复杂结构,只需选择自己熟悉的设计方法和 工具,就可进行设计输入。该软件提供了一种真正与结构无关的可编程逻辑设计环 境,它支持不同结构的器件,如 FLEX﹑MAX 及 CLASSIC 系列器件等。 根据设计要求,很容易设计出 VHDL 源文件。VHDL 源文件如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY controller IS PORT (clk, Sa, Sb: IN STD_LOGIC; R, Y, G, r, y, g: OUT STD_LOGIC); END controller; ARCHITECTURE xcontrol OF controller IS TYPE states IS (s0, s1, s2,s3); SIGNAL state: states; SIGNAL leda: STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL ledb: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN

leda <=R&Y&G; ledb <=r&y &g PROCESS (clk) counter BEGIN IF(cIk'ENENTAND clk=1)THEN IF cr='0'THEN counter =0. ELSIF ent='0 THEN counter :=counter; ELSE counter counter+l: END IF: leda<="001" ledh="100": IF (Sa AND Sb)='1'THEN "sl: cr:=0'; cnt:=0'; ELSE state <s0: cr:=1 :=1 END IF; ELSIF (Sb AND (NOT Sa))='1'THEN state <=sl: cr:=0' ent :=0 ELSE state <s0: cr:=1'; cnt:='1': ENDIF WHEN sI leda<="010" ledb<="100": IF counter=4 THEN state <=s3; cr=0' cnt =0' ELSE state <=s1;

leda leda leda <= ″010″; ledb <= ″100″; IF counter = 4 THEN state <= s3; cr := ′0′; cnt := ′0′; ELSE state <= s1;

cr:='I'; cnt:='1': END IF: WHEN s2=> IF (Sa AND Sb)='1'THEN IF counter=19 THEN state leda <="100" 1db<←="010"g IF counter=4 THEN state <s0: cr:=0'; cnt ='0' ELSE state<=s3; cr ='1'; ent ='1'; END IF; End CASE END IF: END PROCESS; END xcontrol; 将VHDL源文件输入到MAX+PlusII软件中,进行调试、仿真,其仿真结果如 图4所示

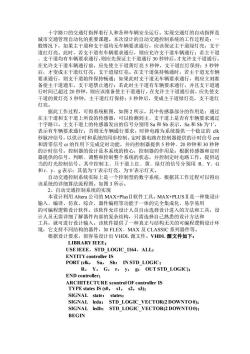

cr := ′1′; cnt := ′1′; END IF; WHEN s2 => leda leda <= ″100″; ledb <= ″010″; IF counter = 4 THEN state <= s0; cr := ′0′; cnt := ′0′; ELSE state <= s3; cr := ′1′; cnt := ′1′; END IF; END CASE; END IF; END PROCESS; END xcontrol; 将 VHDL 源文件输入到 MAX+PlusII 软件中,进行调试、仿真,其仿真结果如 图 4 所示

600 ▣Tme352u Interval:3.46us 20us 4.0u5 6 Dus 8.0us 100us ITmm 图4自动交通控制系统仿真波形图 通过仿真波形和时序分析等功能,可以验证设计的正确性,并能迅速地在不改 变硬件电路的情况下修改设计,这样做可大大地缩短设计周期,提高效率。当确认 设计无误后,将生成的可配置文件通过Altera公司编程电缆ByteBlaster装入可编程 逻辑器件EPM7032,通过调试,完成了整个设计

图 4 自动交通控制系统仿真波形图 通过仿真波形和时序分析等功能,可以验证设计的正确性,并能迅速地在不改 变硬件电路的情况下修改设计,这样做可大大地缩短设计周期,提高效率。当确认 设计无误后,将生成的可配置文件通过 Altera 公司编程电缆 ByteBlaster 装入可编程 逻辑器件 EPM7032,通过调试,完成了整个设计

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计四 数字电子密码锁.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计二 数字抢答器的设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十二 移位相加8位乘法器电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十一 电子琴电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(1/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(2/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计三 数字频率计的设计.doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第一章 绪论(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第二章 逻辑函数及其简化(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第三章 集成逻辑门(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第四章 组合逻辑电路(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第七章 半导体存储器(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第八章 可编程逻辑器件及其应用(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第六章 时序逻辑电路(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第五章 集成触发器(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第十章 模数转换器和数模转换器(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第九章 脉冲单元电路(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)学生常见问题答疑(含解答).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电A卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电B卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电A卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电B卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电B卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电B卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电A卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电C卷(试题).doc