《数字电路与逻辑设计》课程教学资源(试卷习题)第五章 集成触发器(含解答)

第五章集成触发器 一、选择题 1.N个触发器可以构成能寄存」 位二进制数码的寄存器 A.N-1 B.N C.N+1 D.2N 2.在下列触发器中,有约束条件的是 A.主从JKFF B.主从DFFC.同步RSFF D.边沿DFF 3。一个触发器可记录一位二进制代码,它有个稳态。 A.0 B.1 C.2 D.3 E.4 4.存储8位二进制信息要个触发器。 A.2 B.3 C.4 D.8 5.对于T触发器,若原态Q=0,欲使新态Q1=1,应使输入T=一。 A.0 B.1 C.Q D.0 6.对于T触发器,若原态Q=1,欲使新态Q+1=1,应使输入T= A.0 B.1 C.Q D.6 7.对于D触发器,欲使Q+1=Q,应使输入D= A.0 B.1 C.Q D.Q 8。对于JK触发器,若J=K,则可完成触发器的逻辑功能。 A.RS B.D C.T D.T' 9.欲使JK触发器按Q+1=Q工作,可使JK触发器的输端 A.J=K=0 B.J=Q,K=Q C.J=0,K=Q D.J=Q,K=0 E.J=0,K=Q 10.欲使JK触发器按Q1=Q”工作,可使JR触发器的输端 A.J=K=1 B.J=Q,K=Q C.J=Q,K=Q D.J=Q,K=1 E.J=1,K=Q 11.欲使JK触发器按Qm+1=0工作,可使JK触发器的输入端 A.J=K=1 B.J=Q,K=Q C.J=Q,K=1 D.J=0,K=1 E.J=K=1 12.欲使JK触发器按Q+1=1工作,可使JK触发器的输入端。 A.J=K=1 B.J=1,K=0 C.J=K=Q D.J=K=0 E.J=0,K=0 13.欲使D触发器按Q+1=0n工作,应使输入D=_

第五章集成触发器 一、选择题 1 . N 个触发器可以构成能寄存 位二进制数码的寄存器。 A . N - 1 B . N C . N + 1 D . 2 N 2.在下列触发器中,有约束条件的是 。 A .主 从 JKF F B .主 从 D F F C .同 步 RSF F D .边 沿 D F F 3.一个触发器可记录一位二进制代码,它有 个稳态。 A . 0 B . 1 C . 2 D . 3 E.4 4.存储 8 位二进制信息要 个触发器 。 A . 2 B . 3 C . 4 D . 8 5.对 于 T 触 发 器 ,若 原 态 Q n = 0,欲 使 新 态 Q n + 1 = 1,应 使 输 入 T = 。 A . 0 B . 1 C . Q D . Q 6.对 于 T 触 发 器 ,若 原 态 Q n = 1,欲 使 新 态 Q n + 1 = 1,应 使 输 入 T = 。 A . 0 B . 1 C . Q D . Q 7.对于 D 触发器,欲使 Q n + 1 = Q n ,应使输入 D = 。 A . 0 B . 1 C . Q D . Q 8.对于 J K 触发器,若 J=K,则可完成 触发器的逻辑功能。 A . R S B . D C . T D . Tˊ 9.欲 使 J K 触发器按 Q n + 1 = Q n 工 作 ,可 使 JK 触发器的输 端 。 A.J=K= 0 B.J=Q,K= Q C.J= Q ,K= Q D.J=Q,K=0 E.J=0,K= Q 1 0.欲 使 J K 触 发 器 按 Q n + 1 = Q n 工 作 ,可 使 JK 触发器的输 端 。 A.J=K=1 B.J=Q,K= Q C.J= Q ,K= Q D.J=Q,K=1 E.J=1,K=Q 1 1.欲 使 J K 触发器按 Q n + 1 = 0 工 作 ,可 使 J K 触 发 器 的 输 入 端 。 A.J=K=1 B.J=Q,K=Q C.J=Q,K=1 D.J=0,K=1 E.J=K=1 1 2.欲 使 J K 触发器按 Q n + 1 = 1 工 作 ,可 使 J K 触 发 器 的 输 入 端 。 A.J=K=1 B.J=1,K=0 C.J=K= Q D.J=K=0 E.J= Q ,K=0 1 3.欲使 D 触发器按 Q n + 1 = Q n 工作,应使输入 D =

A.0 B.1 C.Q D.G 14.下列触发器中,克服了空翻现象的有」 A.边沿D触发器B.主从RS触发器C.同步RS触发器 D.主从JK触发器 15.下列触发器中,没有约束条件的是 A.基本RS触发器B.主从RS触发器C.同步RS触发器 D.边沿D触发器 16,描述触发器的逻辑功能的方法有, A.状态转换真值表B.特性方程C.状态转换图 D.状态转换卡诺图 17.为实现将JK触发器转换为D触发器,应使 A.J=D,K=D B.K=D,J=D C.J=K=D D.J=K=D 18.边沿式D触发器是一种稳态电路。 A.无 B.单 C.双 D.多 二、判断题(正确打√,错误的打×) 1.D触发器的特性方程为Q*1=D,与Q无关,所以它没有记忆功能.( 2.RS触发器的约束条件RS=0表示不允许出现R=S=1的输入( 3.同步触发器存在空翻现象,而边沿触发器和主从触发器克服了 空翻。() 4.主从JK触发器、边沿JK触发器和同步JK触发器的逻辑功能完 全相同。() 5若要实现一个可暂停的一位二进制计数器,控制信号A=0计数 A=1保持,可选用T触发器,且令T=A。() 6,由两个TTL或非门构成的基本RS触发器,当R=S=0时,触发器 的状态为不定。 7.对边沿JK触发器,在CP为高电平期间,当J=K=1时,状态会 翻转一次。() 三、填空题 1.触发器有个稳态,存储8位二进制信息要_ 个触发器。 2. 一个基本RS触发器在正常工作时,它的约束条件是R+S=1

A . 0 B . 1 C . Q D . Q 1 4.下列触发器中,克服了空翻现象的有 。 A .边 沿 D 触发器 B .主 从 R S 触发器 C .同 步 R S 触发器 D .主 从 J K 触发器 1 5.下列触发器中,没有约束条件的是 。 A .基 本 R S 触发器 B .主 从 R S 触发器 C .同 步 R S 触发器 D .边 沿 D 触发器 1 6.描述触发器的逻辑功能的方法有 。 A .状态转换真值表 B .特性方程 C .状态转换图 D .状态转换卡诺图 1 7.为实现将 J K 触发器转换为 D 触发器,应使 。 A.J=D,K= D B. K=D,J= D C.J=K=D D.J=K= D 18.边沿式 D 触发器是一种 稳态电路。 A .无 B .单 C .双 D .多 二、判断题(正确打√,错误的打×) 1. D 触发器的特性方程为 Q n + 1 = D,与 Q n 无 关 ,所 以 它 没 有 记 忆 功 能 。( ) 2. R S 触发器的约束条件 RS=0 表示不允许出现 R=S=1 的 输 入 。( ) 3. 同步触 发 器 存 在 空 翻 现 象 , 而 边 沿 触 发 器 和 主 从 触 发 器 克 服 了 空 翻 。( ) 4. 主 从 J K 触 发 器 、边 沿 J K 触 发 器 和 同 步 J K 触发器的逻辑功能完 全 相 同 。( ) 5. 若 要 实 现 一 个 可 暂 停 的 一 位 二 进 制 计 数 器 ,控 制 信 号 A=0 计数, A=1 保持,可选用 T 触发器,且令 T=A。( ) 6. 由两个 TTL 或非门构成的基本 RS 触 发 器 ,当 R = S =0 时 ,触 发 器 的状态为不定。 7. 对边沿 J K 触发器,在 C P 为高电平期间,当 J = K = 1 时,状态会 翻 转 一 次 。( ) 三、填空题 1.触发器有 个 稳 态 ,存 储 8 位二进制信息要 个触发器。 2.一个基本 R S 触发器在正常工作时,它的约束条件是 R + S = 1

则它不允许输入S=_且R=_的信号。 3.触发器有两个互补的输出端Q、Q,定义触发器的1状态 为 ,0状态为」 可见触发器的状态 指的是端的状态。 4.一个基本RS触发器在正常工作时,不允许输入R=S=1的信号, 因此它的约束条件是 5,在一个CP脉冲作用下,引起触发器两次或多次翻转的现象称为 触发器的」 ,触发方式为」 式或 式的触发 器不会出现这种现象。 四、S触发器有哪几种功能?写出特征方程和特性表。 五、基本S触发器如图题五所示,试画出Q对应R和S的被形(设Q的初态为0)。 0 sW T/\ 图题五 六、同步S触发器如图题六所示,试画出Q对应R和S的波形(设Q的初态为0) mU sΠ几 R几 图愿六 七、已知下降沿有效的JK触发器CP、」、K及异步置1端S、异步置0端S:的波形如 图题七所示,试画出Q的波形(设Q的初态为0)

则它不允许输入 S = 且 R= 的信号。 3.触发器有两个互补的输出端 Q、 Q ,定义触发器的 1 状 态 为 ,0 状态为 ,可 见 触 发 器 的 状 态 指的是 端的状态。 4.一个基本 R S 触发器在正常工作时,不允许输 入 R = S =1 的信号, 因此它的约束条件是 。 5.在 一 个 C P 脉 冲 作 用 下 ,引 起 触 发 器 两 次 或 多 次 翻 转 的 现 象 称 为 触发器的 ,触发方式为 式 或 式的触发 器不会出现这种现象。 四、RS 触发器有哪几种功能?写出特征方程和特性表。 五、基本 RS 触发器如图题五所示,试画出 Q 对应 R 和 S 的波形(设 Q 的初态为 0)。 图题五 六、同步 RS 触发器如图题六所示,试画出 Q 对应 R 和 S 的波形(设 Q 的初态为 0)。 图题六 七、已知下降沿有效的 JK 触发器 CP、J、K 及异步置 1 端 Sd 、异步置 0 端 Sd 的波形如 图题七所示,试画出 Q 的波形(设 Q 的初态为 0)

Rd K 图避七 八、主从触发器对同步输入信号有什么要求? 九、提高触发器抗干扰能力的主要措施是什么? 十、K触发器有哪几种功能?写出特征方程和特性表。 十、D触发器有哪几种功能?写出特征方程和特性表。 十一、己知CP、D的波形如图题十一,试画出高电平有效和上升沿有效D触发器Q 的波形(设Q的初态为0)。 cp几几几Π 图圈十一 十二、设图十二中的触发器的初态均为0,试画出Q端的波形 2 3 图恩十二 十三、设图盟十三中的触发器的初态均为0,试画出对应A、B的X、Y的波形

图题七 八、主从触发器对同步输入信号有什么要求? 九、提高触发器抗干扰能力的主要措施是什么? 十、JK 触发器有哪几种功能?写出特征方程和特性表。 十、 D 触发器有哪几种功能?写出特征方程和特性表。 十一、 已知 CP、D 的波形如图题十一,试画出高电平有效和上升沿有效 D 触发器 Q 的波形(设 Q 的初态为 0)。 图题十一 十二、 设图题十二中的触发器的初态均为 0,试画出 Q 端的波形。 图题十二 十三、 设图题十三中的触发器的初态均为 0,试画出对应 A、B 的 X、Y 的波形

a几几几几几 B几几几几 图越十三 十四、电路如图题十四所示,S为常开按钮,C是用来防抖动的,是分析当点击S 时,发光二极管LED的发光情况 图题十四 第五章答案 一、选择题 1.ABD 2.CD CD 5.ABC 6.ABD 7.C ACD 9. ACD 10.B 二、判断题 1.√2.3.√4.√5.√ 6.×7. 8.×9.10

图题十三 十四、 电路如图题十四所示,S 为常开按钮,C 是用来防抖动的,是分析当点击 S 时,发光二极管 LED 的发光情况。 图题十四 第五章答案 一、选择题 1. ABD 2. CD 3. A 4. CD 5. ABC 6. ABD 7. C 8. ACD 9. ACD 10. B 二、判断题 1.√ 2.√ 3.√ 4.√ 5.√ 6.× 7.√ 8.× 9.√ 10.√

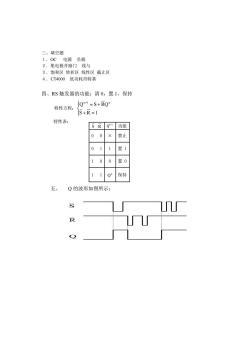

三、填空愿 1,OC电源负载 2.集电极开路门线与 3.饱和区转折区线性区截止区 4.CT4000低功耗肖特基 四、RS触发器的功能:清0,置1,保持 Q=S+RQM 特性方程: S+R=1 特性表: §RQ功能 00×禁止 11 置1 00置0 11Q保持 五、Q的波形如图所示: R

三、填空题 1.OC 电源 负载 2.集电极开路门 线与 3.饱和区 转折区 线性区 截止区 4.CT4000 低功耗肖特基 四、RS 触发器的功能:清 0,置 1,保持 特性方程: + = = + + S R 1 Q S RQ n 1 n 特性表: 五、 Q 的波形如图所示: S R Q n+1 功能 0 0 × 禁止 0 1 1 置 1 1 0 0 置 0 1 1 n Q 保持

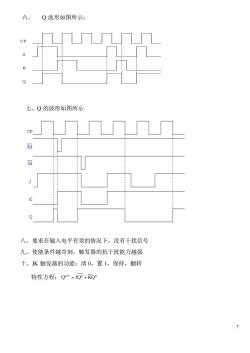

六、Q波形如图所示: CP 七、Q的波形如图所示 CP 八、要求在输入电平有效的情况下,没有干扰信号 九、使能条件越苛刻,触发器的抗干扰能力越强 十、K触发器的功能:清0,置1,保持,翻转 特性方程:Q-JQ+KQ

7 六、 Q 波形如图所示: 七、Q 的波形如图所示 八、要求在输入电平有效的情况下,没有干扰信号 九、使能条件越苛刻,触发器的抗干扰能力越强 十、JK 触发器的功能:清 0,置 1,保持,翻转 特性方程: n 1 n n Q = JQ + KQ +

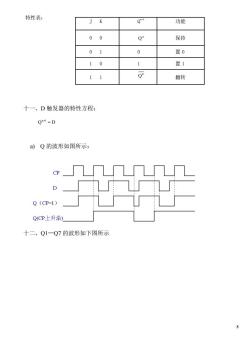

特性表: J K 功能 00 保持 01 0 置0 10 1 置1 11 翻转 十一、D触发器的特性方程: Q=D a)Q的波形如图所示: CP D Q (CP=1) Q(CP上升沿) 十二、Q1一Q7的波形如下图所示 8

8 特性表: 十一、D 触发器的特性方程: Q D n 1 = + a) Q 的波形如图所示: 十二、Q1—Q7 的波形如下图所示 J K Q n+1 功能 0 0 n Q 保持 0 1 0 置 0 1 0 1 置 1 1 1 n Q 翻转

CP Q1 Q20 Q3 9 Q6_ Q70 十三、X、Y的波形如下图所示 B 十四、假设LED初始状态是灭,点击S一下,LED变亮:再点击S一下,LED变灭。 9

9 十三、 X、Y 的波形如下图所示 十四、假设 LED 初始状态是灭,点击 S 一下,LED 变亮;再点击 S 一下,LED 变灭

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第六章 时序逻辑电路(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第八章 可编程逻辑器件及其应用(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第七章 半导体存储器(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第四章 组合逻辑电路(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第三章 集成逻辑门(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第二章 逻辑函数及其简化(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第一章 绪论(含解答).doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计三 数字频率计的设计.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计一 自动交通控制系统.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计四 数字电子密码锁.doc

- 《数字电路与逻辑设计》课程实验指导(实验设计)设计二 数字抢答器的设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十二 移位相加8位乘法器电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十一 电子琴电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(1/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(2/2).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第十章 模数转换器和数模转换器(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)第九章 脉冲单元电路(含解答).doc

- 《数字电路与逻辑设计》课程教学资源(试卷习题)学生常见问题答疑(含解答).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电A卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电B卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电A卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电B卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电B卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电B卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数电A卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电C卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电C卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数电A卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数电B卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数电A卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数电B卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数电C卷(试题).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数电C卷(答案).doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数电A卷(试题).doc

- 内蒙古农业大学:《单片机原理及应用》课程教学大纲 The principle and application of single chip microcomputer A.pdf