《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一)

实验三组合逻辑电路的设计(一) 一、实验目的 1.掌握用SSI器件设计组合逻辑电路的方法: 2.熟悉各种常用MS1组合逻辑电路的功能与使用方法: 3.掌握多片MSI组合逻辑电路的级联、功能扩展: 学会使用MSI逻辑器件设计组合电路 5.培养查找和排除数字电路常见故障的初步能力。 二、实验器件 1,74LS00 四二输入与非门 74LS20 双四输入与非门 2.74LS138 三线一八线译码器 74LS139 双二线一四线译码器 三、实验原理 组合逻辑电路是最常见的逻辑电路,其特点是在任何时刻电路的输出信号仅取决于该时 刻的输入信号,而与信号作用前电路原来所处的状态无关。组合逻辑电路的设计,就是如何 根据逻辑功能的要求及器件资源情况,设计出实现该功能的最佳电路。 在采用小规模器件(SS1)讲行设计时,通常将函数化简成最简与一或表达式,使其包 含的乘积项最少,且每个乘积项所包含的因子数也最少。最后根据所采用的器件的类型进行 当的函数表达式变换,如变换成与非 与非表达式、或非一或排表达式。 与或非表达式及 异或表达式等。 在数字系统中,常用的中规模集成器件(MS)产品有编码器、译码器、全加器、数据选 择/分配器、数值比较器等。用这些功能器件实现组合逻辑函数,基本采用逻辑函数对比方 去。因为每一种中趣横集成器件都具有其种确定的罗辑功能,都可以写出其输出和输入关系 的逻辑函数表达式。在进行设计时,可以将要实现的逻辑函数表达式进行变换,尽可能变换 成与某些中规模集成器件的逻辑函数表达式类似的形式。 下米我们介绍一下使用中小规模器件设计组合逻辑电路的一般方法。 四、组合电路设计原则及其步骤 组合电路的设计是由给定的的逻辑功能要求,设计出实现该功能的逻辑电路,设计过程 大致按下列步骤进行: (1) 分析设计要求,把用文字描述的形式的设计要求抽象成输入、输出变量的逻辑关系 (2)根据分析出的逻辑关系,通过真值表或其他方式列出逻辑函数表达式: (3)根据题目提供给你的芯片,将逻辑函数化简到所需要的函数式: (4)画出罗辑电路图或电路原理图: 对于MSI组合逻辑电路的设计是以所用MS个数最少、品种最少,同时MS间的连线 也最少作为最基本的原则 下面使用中小规模器件我们各举一个例子: 例:用与非门设计三位多数表决器。 步骤:(1)根据真值表写出逻辑表达式: F=AB+BC+AC=AB BCAC (2)画出逻辑图,如图3一1所示

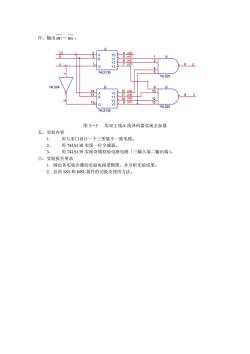

实验三 组合逻辑电路的设计(一) 一、实验目的 1. 掌握用 SSI 器件设计组合逻辑电路的方法; 2. 熟悉各种常用 MSI 组合逻辑电路的功能与使用方法; 3. 掌握多片 MSI 组合逻辑电路的级联、功能扩展; 4. 学会使用 MSI 逻辑器件设计组合电路; 5. 培养查找和排除数字电路常见故障的初步能力。 二、实验器件 1. 74LS00 四二输入与非门 74LS20 双四输入与非门 2. 74LS138 三线—八线译码器 74LS139 双二线—四线译码器 三、实验原理 组合逻辑电路是最常见的逻辑电路,其特点是在任何时刻电路的输出信号仅取决于该时 刻的输入信号,而与信号作用前电路原来所处的状态无关。组合逻辑电路的设计,就是如何 根据逻辑功能的要求及器件资源情况,设计出实现该功能的最佳电路。 在采用小规模器件(SSI)进行设计时,通常将函数化简成最简与—或表达式,使其包 含的乘积项最少,且每个乘积项所包含的因子数也最少。最后根据所采用的器件的类型进行 适当的函数表达式变换,如变换成与非—与非表达式﹑或非—或非表达式﹑与或非表达式及 异或表达式等。 在数字系统中,常用的中规模集成器件(MSI)产品有编码器﹑译码器﹑全加器﹑数据选 择/分配器﹑数值比较器等。用这些功能器件实现组合逻辑函数,基本采用逻辑函数对比方 法。因为每一种中规模集成器件都具有某种确定的逻辑功能,都可以写出其输出和输入关系 的逻辑函数表达式。在进行设计时,可以将要实现的逻辑函数表达式进行变换,尽可能变换 成与某些中规模集成器件的逻辑函数表达式类似的形式。 下来我们介绍一下使用中小规模器件设计组合逻辑电路的一般方法。 四、组合电路设计原则及其步骤 组合电路的设计是由给定的的逻辑功能要求,设计出实现该功能的逻辑电路,设计过程 大致按下列步骤进行: (1) 分析设计要求,把用文字描述的形式的设计要求抽象成输入、输出变量的逻辑关系; (2) 根据分析出的逻辑关系,通过真值表或其他方式列出逻辑函数表达式; (3) 根据题目提供给你的芯片,将逻辑函数化简到所需要的函数式; (4) 画出逻辑电路图或电路原理图; 对于 MSI 组合逻辑电路的设计是以所用 MSI 个数最少、品种最少,同时 MSI 间的连线 也最少作为最基本的原则。 下面使用中小规模器件我们各举一个例子: 例:用与非门设计三位多数表决器。 步骤:(1)根据真值表写出逻辑表达式: F = AB + BC + AC = AB BC AC (2)画出逻辑图,如图 3—1 所示

图3-1 例:用三变量译码器74LS138设计一位全加器 步骤:(1)根据真值表写出全加器逻辑表达式 全加和S=ABC0+ABCo+ABCO+ABC0 进位C=ABCO+ABCO+ABC+ABCO (2)将S、C改写为S=m+m+m4+mm=m.m.m4.m =y1.y2.y4·y7 C=m+ms+ms+m=ms ms m.m =y3·y5·y6.y7 (3)画出逻辑图,如图3一2所示 LS2 图3一2用74LS138设计全加器 若选用双2线/4线译码器741S139,因该译码器只有两个地址输入端,只能对应两个输 入变量,利用使能端可将其扩展为3线8线译码器。对于任意一个三变量的函数表达式总可 以写成它的分解式。 F(A2A1A0)=F1(A1A0)+A2F1(A1A0) 式中,F1(A1A0)用2线4线译码器实现,则上式可用两个同样的译码器来连接,如 图3一3所示。当A20时,译码器(A)工作,输出m~,当A2=1时,译码器(B)工

A B C F 图 3 – 1 例: 用三变量译码器 74LS138 设计一位全加器 步骤:(1)根据真值表写出全加器逻辑表达式 全加和 S= A B C0 + A B C0 +A B C0 +AB C0 进 位 C= A B C0 +A B C0 +AB C0 +AB C0 (2)将 S﹑C 改写为 S = m1 + m2 + m4 + m7 = m1﹒m2 ﹒m4 ﹒m7 = y 1﹒ y 2﹒ y 4﹒ y 7 C = m3 + m5 + m6 + m7 = m3 ﹒m5 ﹒m6 ﹒m7 = y 3﹒ y 5﹒ y 6﹒ y 7 (3)画出逻辑图,如图 3—2 所示 图 3—2 用 74LS138 设计全加器 若选用双 2 线/4 线译码器 74LS139,因该译码器只有两个地址输入端,只能对应两个输 入变量,利用使能端可将其扩展为 3 线/8 线译码器。对于任意一个三变量的函数表达式总可 以写成它的分解式。 F(A2A1A0)= A2 F1(A1A0)+A2 F1(A1A0) 式中,F1(A1A0)用 2 线/4 线译码器实现,则上式可用两个同样的译码器来连接,如 图 3—3 所示。当 A2=0 时,译码器(A)工作,输出 m3 ~m0 ,当 A2=1 时,译码器(B)工 A B C0 S C +5v m0\ m1\ m2\ m3\ m4\ m5\ m6\ m7\ 74LS138 A 1 B 2 C 3 G1 6 G2A 4 G2B 5 Y0 15 Y1 14 Y2 13 Y3 12 Y4 11 Y5 10 Y6 9 Y7 7 A 74LS20 1 2 4 5 6 B 74LS20 9 10 12 13 8

作,输出m7一m4 4 74LS139 15 9m入 74LS139 图3一3用双2线/4线译码器实现全加器 五、实验内容 1.用与非门设计一个三变量不一致电路。 用74LS138实现一位全减器。 用741S139实现奇偶校验电路电路(三输入端二输出端)】 六、实验报告要求 1,画出各实验步骤的实验电路逻辑图,并分析实验结果。 2.总结SSI和MSI器件的功能及使用方法

作,输出 m7 ~ m4 。 图 3—3 用双 2 线/4 线译码器实现全加器 五、实验内容 1. 用与非门设计一个三变量不一致电路。 2. 用 74LS138 实现一位全减器。 3. 用 74LS139 实现奇偶校验电路电路(三输入端二输出端)。 六、实验报告要求 1.画出各实验步骤的实验电路逻辑图,并分析实验结果。 2.总结 SSI 和 MSI 器件的功能及使用方法。 A C0 B m2\ m4\ m7\ m5\ m6\ m0\ m1\ m3\ S C B 74LS139 A 14 B 13 G 15 Y0 12 Y1 11 Y2 10 Y3 9 A 74LS139 A 2 B 3 G 1 Y0 4 Y1 5 Y2 6 Y3 7 A 74LS20 1 2 4 5 6 B 74LS20 9 10 12 13 8 74LS04 1 2

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 西安邮电学院:《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第九章 脉冲单元电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第七章 半导体存储器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(2/2,6.5-6.6).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第六章 时序逻辑电路(1/2,6.1-6.4).ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第五章 触发器.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第三章 集成逻辑门.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第二章 逻辑函数及其简化.ppt

- 西安邮电学院:《数字电路与逻辑设计》课程教学资源(PPT课件)第一章 绪论.ppt

- 《电路》课程教学资源(课后讲稿)第5章 含有运算放大器的电阻电路.pdf

- 《电路》课程教学资源(课后讲稿)第4章 电路定理.pdf

- 《电路》课程教学资源(课后讲稿)第3章 电阻电路的一般分析.pdf

- 《电路》课程教学资源(课后讲稿)第2章 电阻电路的等效变换.pdf

- 《电路》课程教学资源(课后讲稿)第1章 电路模型及定律.pdf

- 《电路》课程教学资源(课后讲稿)第8章 相量法.pdf

- 《电路》课程教学资源(课后讲稿)第6章 储能元件.pdf

- 《电路》课程教学资源(课后讲稿)第9章 正弦稳态电路分析.pdf

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(2/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(1/2).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc