《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述

D ☒ 概述 一、逻辑代数(布尔代数、开关代数) 逻辑:事物因果关系的规律 逻辑函数:逻辑自变量和逻辑结果的关系 Z=f(AB,C.) 逻辑变量取值:0、1分别代表两种对立的状态 种状态 高电平 真 是有 另一状态 低电平 假 非无 ●●● 0

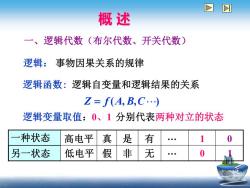

一、逻辑代数(布尔代数、开关代数) 逻辑: 事物因果关系的规律 逻辑函数: 逻辑自变量和逻辑结果的关系 Z = f (A, B,C) 逻辑变量取值:0、1 分别代表两种对立的状态 一种状态 另一状态 高电平 低电平 真 假 是 非 有 无 . . 1 0 0 1 概 述

二、二进制数表示法 1.十进制数(Decimal)-逢十进 数码:0~9 位权:10 (12345)10=1×104+2×103+3×102+4×101+5×10° (143.75)0=1×102+4×10'+3×10°+7×10-1+5×10-2 2.二进制数(Binary)-逢二进一 数码:0,1 位权:2 (1011)2=1×23+0×22+1×21+1×2° (101.11)2=1×22+0×2+1×2°+1×21+1×2地

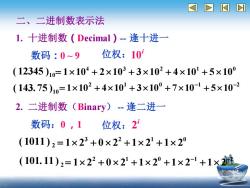

二、二进制数表示法 1. 十进制数(Decimal)- 逢十进一 数码:0 ~ 9 位权: 4 3 2 1 0 = 110 + 210 + 310 + 4 10 + 5 10 2. 二进制数(Binary) - 逢二进一 数码:0 ,1 位权: 2 ( 1011 ) 3 2 1 0 = 1 2 + 0 2 + 1 2 + 1 2 10 ( 12345 ) i 10i 2 2 1 0 1 2 1 10 4 10 3 10 7 10 5 10 − − = + + + + 10 ( 143. 75 ) 2 ( 101.11 ) 2 1 0 1 2 1 2 0 2 1 2 1 2 1 2 − − = + + + +

K I 3.二进制数的缩写形式一八进制数和十六进制数 (1)八进制数(Octal)-逢八进一 数码:0~7 位权:8 (37.41)8=3×8+7×8°+4×81+1×8-2 (2)十六进制数(Hexadecimal)-逢十六进 一 数码:0~9,A(10),B(11),C(12),D(13),E(14),F(15) 位权:16 (2A.7F)16=2×16+10×16°+7×161+15×16-2 任意(N)进制数展开式的普遍形式: D=∑kX k,一第i位的系数N一第i位的权

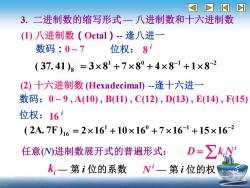

3. 二进制数的缩写形式 — 八进制数和十六进制数 数码:0 ~ 7 位权: 8 ( 37. 41 ) 1 0 1 2 3 8 7 8 4 8 1 8 − − = + + + (2) 十六进制数 (Hexadecimal) -逢十六进一 数码:0 ~ 9 , A(10) , B(11) , C(12) , D(13) , E(14) , F(15) 位权: i 8 i 16 16 ( 2A. 7F ) 1 0 1 2 2 16 10 16 7 16 15 16 − − = + + + 任意(N)进制数展开式的普遍形式: i D = ki N ki i — 第 i 位的系数 N — 第 i 位的权 (1) 八进制数(Octal)- 逢八进一

4.几种常用进制数之间的转换 ()二十转换:将二进制数按位权展开后相加 (101.11)2=1×22+0×2'+1×2°+1×21+1×2-2 =4+1+0.5+0.25=(5.75)10 (2)十-二转换: 降幂比较法一要求熟记20~210的数值。 20 21 22 23 24 25 26 27 28 29 210 2 4 8 16 32 64 128 256512 1024

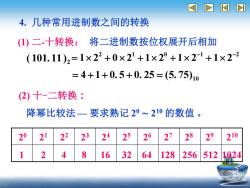

4. 几种常用进制数之间的转换 (1) 二-十转换: 将二进制数按位权展开后相加 2 ( 101.11) 2 1 0 1 2 1 2 0 2 1 2 1 2 1 2 − − = + + + + 10 = 4 +1+ 0. 5 + 0. 25 = (5. 75) (2) 十-二转换: 降幂比较法 — 要求熟记 2 0 ∼ 2 10 的数值 。 2 0 2 1 2 2 2 3 2 4 2 5 2 6 2 7 2 8 2 9 2 10 1 2 4 8 16 32 64 128 256 512 1024

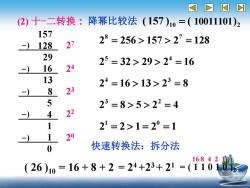

I 2)十-二转换:降幂比较法(157)10=(10011101)2 157 -)128 27 28=256>157>27=128 29 25=32>29>24=16 16 24 13 24=16>13>23=8 8 23 5 23=8>5>22=4 -) 4 22 1 2=2>1=2°=1 1 20 0 快速转换法:拆分法 168421 (26)10=16+8+2=24+23+21=(1101

10 2 ( 157 ) = ( 10011101 ) 157 −) 128 29 −) 16 −) 8 5 2 7 2 4 13 快速转换法:拆分法 ( 26 )10 = 16 + 8 + 2 = 2 4 +23 + 21 = ( 1 1 0 1 0 )2 −) 4 1 1 16 8 4 2 1 (2) 十-二转换: 降幂比较法 2 3 2 2 2 0 −) 0 2 256 157 2 128 8 7 = = 2 32 29 2 16 5 4 = = 2 16 13 2 8 4 3 = = 2 8 5 2 4 3 2 = = 2 2 1 2 1 1 0 = = =

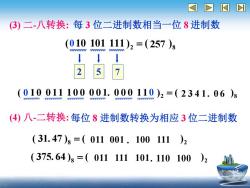

(3)二-八转换:每3位二进制数相当一位8进制数 (010101111)2=(257)8 (010011100001.000110)2=(2341.06)8 (4)八-二转换:每位8进制数转换为相应3位二进制数 (31.47)g=(011001.100111)2 (375.64)8=(011111101.110100)2

(3) 二-八转换: 2 8 ( 10 101 111 ) = ( 257 ) 5 7 (4) 八-二转换:每位 8 进制数转换为相应 3 位二进制数 8 2 ( 31. 47 ) = ( 011 001 . 100 111 ) 每 3 位二进制数相当一位 8 进制数 8 2 ( 375. 64 ) = ( 011 111 101 . 110 100 ) 0 2 8 ( 0 10 011 10 0 0 01. 0 0 0 11 0 ) = ( 2 3 4 1 . 0 6 ) 2

(5)二十六转换: 每4位二进制数相当一位16进制数 (26)10=(00011010)2=(1A)16 1 (000110110110.0010)2=(1B6.2)16 (6)十六-二转换: 每位16进制数换为相应的4位二进制数 (8FA.C6)16=(100011111010.11000110)2 (ED8.2F)16=(111011011000.0010111d

(5)二-十六转换: 每 4 位二进制数相当一位 16 进制数 10 2 16 ( 26 ) = ( 1 1010 ) = ( 1A ) 1 A (6)十六-二转换: 每位 16 进制数换为相应的 4 位二进制数 1 6 2 ( 8 F A .C 6 ) = ( 10 0 0 ) 1 6 2 ( ED 8 . 2F ) = ( 1110 ) 1111 1010 .110 0 0110 1101 10 0 0 .0 010 1111 ( 1 1011 0110 . 0 01 ) ( ) 2 = 1B6. 2 1 6 000 000 0

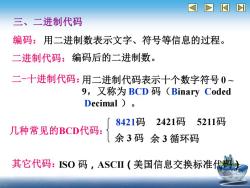

三、二进制代码 编码:用二进制数表示文字、符号等信息的过程。 二进制代码:编码后的二进制数。 二-十进制代码:用二进制代码表示十个数字符号0~ 9,又称为BCD码(Binary Coded Decimal )0 8421码 2421码 5211码 几种常见的BCD代码: 1余3码余3循环码 其它代码:ISO码,ASCⅡ(美国信息交换标准代码

编码:用二进制数表示文字、符号等信息的过程。 二进制代码:编码后的二进制数。 用二进制代码表示十个数字符号 0 ~ 9,又称为 BCD 码(Binary Coded Decimal )。 几种常见的BCD代码: 8421码 余 3 码 2421码 5211码 余 3 循环码 其它代码:ISO 码,ASCII(美国信息交换标准代码) 三、二进制代码 二-十进制代码:

DI 十进 几种常见的BCD代码 制数 8421码 余3码 2421(A)码 5211码 余3循环码 0000 0011 0000 0000 0010 0001 0100 0001 0001 0110 2 0010 0101 0010 0100 0111 3 0011 0110 0011 0101 0101 4 0100 0111 0100 0111 0100 0101 1000 1011 1000 1100 6 0110 1001 1100 1001 1101 0111 1010 1101 1100 1111 8 1000 1011 1110 1101 1110 9 1001 1100 1111 1111 101 权 8421 2421 5211

0 十进 制数 1 2 3 4 5 6 7 8 9 8421 码 余 3 码 2421(A)码 5211 码 余3循环码 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 1 1 1 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 1 1 0 0 0 1 0 0 1 1 1 0 0 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 0 0 1 0 0 1 1 0 0 1 1 1 1 1 0 0 1 1 1 0 1 0 1 0 权 8 4 2 1 2 4 2 1 5 2 1 1 几种常见的 BCD 代码

✉冈 四、EDA技术(Electronics Design Automation) 一种以计算机作为工作平台,以EDA软件 工具为开发环境,以VDL为设计语言,以可 编程逻辑器件为实验载体,以ASIC、SoC芯片 为目标器件,以数字系统设计为应用方向的电子 产品自动化设计技术。 VHDL是一种硬件描述语言,用软件编程语 言形式描述硬件电路功能,比原理图方式更方便、 更高效地反映电路的功能

四、EDA 技术 (Electronics Design Automation ) 一种以计算机作为工作平台,以 EDA 软件 工具为开发环境,以 VHDL为设计语言,以可 编程逻辑器件为实验载体,以 ASIC、SoC芯片 为目标器件,以数字系统设计为应用方向的电子 产品自动化设计技术。 VHDL 是一种硬件描述语言,用软件编程语 言形式描述硬件电路功能,比原理图方式更方便、 更高效地反映电路的功能

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程试卷习题(自我检测)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第6章 脉冲产生和整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第5章 时序逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第4章 触发器.doc

- 内蒙古科技大学:《数字电子技术》课程设计指导书.doc

- 内蒙古科技大学:《数字电子技术》课程教学实验指导书(共八个实验).doc

- 内蒙古科技大学:《数字电子技术》课程实验教学大纲 Electronic Techniques Experiments.doc

- 内蒙古科技大学:《数字电子技术》课程教学大纲 Digital electric technology.doc

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第十章 可编程逻辑器件.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第六章 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt