《数字电子技术》课程授课教案(讲义)第4章 触发器

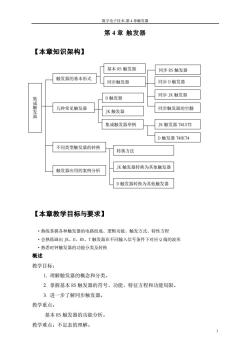

数字电子技术第4章触发器 第4章触发器 【本章知识架构】 基本RS触发器 同步RS触发器 触发器的基本形式 同步触发器 同步D触发器 同步K触发器 D触发器 集成触发器 几种常见触发器 JK触发器 同步触发器的空翻 集成触发器举例 JK触发器74S72 D触发器74HC74 不同类型触发器的转换 转换方法 触发器应用的案例分析 JK触发器转换为其他触发器 D触发器转换为其他触发器 【本章教学目标与要求】 ·熟练掌握各种触发器的电路组成、逻辑功能、触发方式、特性方程 ·会熟练画出瓜、D、S、T触发器在不同输入信号条件下对应Q端的波形 ·熟悉时钟触发器的功能分类及转换 概述 教学目标: 1.理解触发器的概念和分类。 2.掌握基本S触发器的符号、功能、特征方程和功能局限 3.进一步了解同步触发器。 教学重点: 基本RS触发器的功能分析。 教学难点:不定态的理解

数字电子技术-第 4 章触发器 1 第 4 章 触发器 【本章知识架构】 【本章教学目标与要求】 ·熟练掌握各种触发器的电路组成、逻辑功能、触发方式、特性方程 ·会熟练画出 JK、D、RS、T 触发器在不同输入信号条件下对应 Q 端的波形 ·熟悉时钟触发器的功能分类及转换 概述 教学目标: 1. 理解触发器的概念和分类。 2. 掌握基本 RS 触发器的符号、功能、特征方程和功能局限。 3. 进一步了解同步触发器。 教学重点: 基本 RS 触发器的功能分析。 教学难点:不定态的理解。 基本 RS 触发器 同步 RS 触发器 同步触发器 触发器应用的案例分析 集 成 触 发 器 几种常见触发器 不同类型触发器的转换 JK 触发器 D 触发器 触发器的基本形式 转换方法 JK 触发器转换为其他触发器 D 触发器转换为其他触发器 同步 D 触发器 同步 JK 触发器 同步触发器的空翻 集成触发器举例 JK 触发器 74LS72 D 触发器 74HC74

数字电子技术第4章触发器 1、时序逻辑电路一一输出由输入信号与电路前一个状态共同决定。 含有存储电路。 触发器一一时序逻辑电路的基本单元。 2、触发器的特点 令两个稳定状态:具有记忆(“0”或“1”)功能,能存储二进制数码, 令两个状态的转换靠触发(激励)信号来实现。 3、分类:电路结构:基本RS触发器、同步RS触发器、D触发器、JK触发器等。 触发方式:电平触发、边沿触发、主从触发 逻辑功能:S触发器、D触发器、JK触发器、T触发器 4.1基本触发器 4.1.1由与非门组成的基本S触发器 (1)电路结构。由两个与非门的输入输出端交叉耦合。它与组合电路的根本区别 在于,电路中有反馈线。 图4-1与非门组成的基本RS触发器(a)逻辑图 (b)逻辑符号 它有二个输入端R、S,有两个输出端Q、Q。一般情况下,Q、Q是互补的。 定义:当Q=1,0=0时,称为触发器的1状态: 当Q=0,0=1时,称为触发器的0状态。 (2)逻辑功能表。 可见,触发器的新状态(也称次态)不仅与输入状态有关,也与触发器原来的 状态(也称现态或初态)有关。 表41与非门组成基本RS触发器逻辑功能表 R on Qn+1 功能说明 0 0 0 不稳定状态 0 0 1

数字电子技术-第 4 章触发器 2 1、时序逻辑电路——输出由输入信号与电路前一个状态共同决定。 含有存储电路。 触发器——时序逻辑电路的基本单元。 2、触发器的特点 两个稳定状态:具有记忆(“0”或“1”)功能,能存储二进制数码, 两个状态的转换靠触发(激励)信号来实现。 3、分类:电路结构:基本 RS 触发器、同步 RS 触发器、D 触发器、JK 触发器等。 触发方式:电平触发、边沿触发、主从触发 逻辑功能:RS 触发器、D 触发器、JK 触发器、T 触发器 4.1 基本触发器 4.1.1 由与非门组成的基本 RS 触发器 (1)电路结构。由两个与非门的输入输出端交叉耦合。它与组合电路的根本区别 在于,电路中有反馈线。 G & & G 1 2 (a) (b) R R S S Q Q Q Q 图 4-1 与非门组成的基本 RS 触发器 (a)逻辑图 (b)逻辑符号 它有二个输入端 R、S,有两个输出端 Q、Q 。一般情况下,Q、Q 是互补的。 定义:当 Q=1,Q =0 时,称为触发器的 1 状态; 当 Q=0,Q =1 时,称为触发器的 0 状态。 (2)逻辑功能表。 可见,触发器的新状态 Q n+1(也称次态)不仅与输入状态有关,也与触发器原来的 状态 Q n(也称现态或初态)有关。 表 4-1 与非门组成基本 RS 触发器逻辑功能表 R S Qn Qn+1 功能说明 0 0 0 0 0 1 × × 不稳定状态

数字电子技术-第4章触发器 0 0 0 置0(复位) 0 0 1 0 0 置1(置位) 0 保持原状态 触发器的特点: ①有两个互补的输出端,有两个稳态。 ②有复位(Q=0)、置位(Q=1)、保持原状态三种功能。 ③R为复位输入端,S为置位输入端,该电路为低电平有效。 ④由于反馈线的存在,无论是复位还是置位,有效信号只须作用很短的一段时 间。即“一触即发”。 (3)波形分析. 【例41】用与非门组成的基本RS触发器如图43(a)所示,设初始状态为0, 已知输入R、S的波形图如图44,画出输出Q、O的波形图。 解:由表41可画出输出Q、0的波形如图42所示。 图中虚线所示为考虑门电路的延迟时间的情况。 R 图4-2例4-1波形图 基本RS触发器具有复位(Q=0)、置位(Q=1)、保持原状态三种功能 R为复位输入端,S为置位输入端,可以是低电平有效,也可以是高电平有效,取决 于触发器的结构。 3

数字电子技术-第 4 章触发器 3 0 1 0 1 0 1 0 0 置 0(复位) 1 0 1 0 0 1 1 1 置 1(置位) 1 1 1 1 0 1 0 1 保持原状态 触发器的特点: ① 有两个互补的输出端,有两个稳态。 ② 有复位(Q=0)、置位(Q=1)、保持原状态三种功能。 ③ R 为复位输入端,S 为置位输入端,该电路为低电平有效。 ④ 由于反馈线的存在,无论是复位还是置位,有效信号只须作用很短的一段时 间。即“一触即发”。 (3)波形分析。 【例 4-1】用与非门组成的基本 RS 触发器如图 4-3(a)所示,设初始状态为 0, 已知输入 R、S 的波形图如图 4-4,画出输出 Q、Q 的波形图。 解:由表 4-1 可画出输出 Q、Q 的波形如图 4-2 所示。 图中虚线所示为考虑门电路的延迟时间的情况。 图 4-2 例 4-1 波形图 基本 RS 触发器具有复位(Q=0)、置位(Q=1)、保持原状态三种功能, R 为复位输入端,S 为置位输入端,可以是低电平有效,也可以是高电平有效,取决 于触发器的结构。 R S Q Q 2 tpd tpd

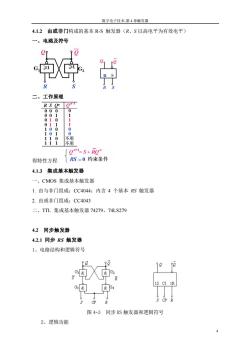

数字电子技术第4章触发器 4.1.2由或非门构成的基本R-S触发器(R、S以高电平为有效电平) 一、电路及符号 二、工作原理 110 「Q1-S+RQ” 得特性方程1RS=0约束条件 4.1.3集成基本触发器 一、CMOS集成基本触发器 1.由与非门组成:CC4044:内含4个基本R5触发器 2.由或非门组成:CC4043 二、TTL集成基本触发器74279、74LS279 4.2同步触发器 4.2.1同步RS触发器 1、电路结构和逻辑符号 图4-3同步RS触发器和逻辑符号 2、逻辑功能

数字电子技术-第 4 章触发器 4 4.1.2 由或非门构成的基本 R-S 触发器(R、S 以高电平为有效电平) 一、电路及符号 二、工作原理 得特性方程 4.1.3 集成基本触发器 一、CMOS 集成基本触发器 1. 由与非门组成:CC4044:内含 4 个基本 RS 触发器 2. 由或非门组成:CC4043 二、TTL 集成基本触发器 74279、74LS279 4.2 同步触发器 4.2.1 同步 RS 触发器 1、电路结构和逻辑符号 图 4-3 同步 RS 触发器和逻辑符号 2、逻辑功能

数字电子技术-第4章触发器 (1)CP=0时,R=1、5=l,触发器保持原来状态不变。 (2)CP=1时,工作情况与基本S触发器相同, 特性表: CP R 功能 0 + QQ=Q”保持 0 0 0 0 Q1=Q”保持 0 1 0 0 1 1 1 Q1=1置1 0 Q=0置0 0 不用 1 1 不用 不允许 3、触发器外部逻辑特性的描述方法 真值表(特性表)、驱动表、符号图、特性方程、状态转换图、时序图(波形图)。 (1)驱动表(又称激励表) 概念:根据触发器的现态和次态的转化关系来确定输入信号取值的关系表称为驱 动表。 表4-3同步RS触发器的驱动表 o" Q R s 0 0 0 0 1 0 1 0 1 1 0 (2)特性方程 概念:指描述触发器次态Q1与R、S及现态Q之间关系的逻辑表达式。 同步RS触发器的特性方程为: [o"=S+RO" S=0(约束条件) (CP=1期间有效) (3)状态转换图 概念:它表示触发器从一个状态变化到另一个状态或保持原状态不变时,对输入

数字电子技术-第 4 章触发器 5 (1)CP=0 时, R =1、S =1,触发器保持原来状态不变。 (2)CP=1 时,工作情况与基本 RS 触发器相同。 特性表: CP R S Qn Q n+1 功能 0 × × × Q n n n Q = Q +1 保持 1 0 0 0 1 0 0 1 0 1 n n Q = Q +1 保持 1 0 1 0 1 0 1 1 1 1 1 1 = n+ Q 置 1 1 1 0 0 1 1 0 1 0 0 0 1 = n+ Q 置 0 1 1 1 0 1 1 1 1 不用 不用 不允许 3、触发器外部逻辑特性的描述方法 真值表(特性表)、驱动表、符号图、特性方程、状态转换图、时序图(波形图)。 (1)驱动表(又称激励表) 概念:根据触发器的现态和次态的转化关系来确定输入信号取值的关系表称为驱 动表。 表 4-3 同步 RS 触发器的驱动表 n Q n 1 Q + R S 0 0 × 0 0 1 0 1 1 0 1 0 1 1 0 × (2)特性方程 概念:指描述触发器次态 n 1 Q + 与 R、S 及现态 n Q 之间关系的逻辑表达式。 同步 RS 触发器的特性方程为: = = + + 0( ) 1 RS 约束条件 Q S RQ n n (CP=1 期间有效) (3)状态转换图 概念:它表示触发器从一个状态变化到另一个状态或保持原状态不变时,对输入

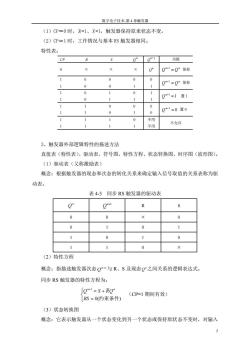

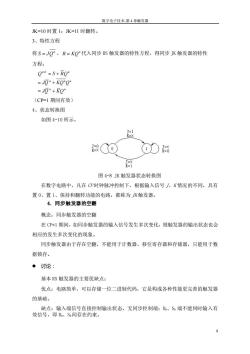

数字电子技术第4章触发器 信号(R、S)提出的要求。 或:描述触发器的状态转换关系及转换条件的图形称为状态图 ·状态转换图与真值表是统一的,它是真值表的直观形象表示。 同步RS触发器的状态转换图如图4-4所示。 R=0S=1 (0 R=1S=0 图4-4同步S触发器的状态转换图 4、同步RS触发器的主要特点 (1)时钟电平控制。在CP=1期间接收输入信号,CP=0时状态保持不变,与 基本S触发器相比,对触发器状态的转变增加了时间控制。 (2)R、S之间有约束。不能允许出现R和S同时为1的情况,否则会使触发器 处于不确定的状态。 2.同步D触发器(D锁存器) 为避免同步RS触发器同时出现R和S都为1的情况而设计。 1、电路结构和逻辑符号 如图4-5所示。 (包)D触发器的构成 ()D触发器的简化电路 何逻辑符号 图4-5同步D触发器和逻辑符号 2、逻辑功能 将S=D、R=D代入同步RS触发器的特性方程,得同步D触发器的特性方程:

数字电子技术-第 4 章触发器 6 信号(R、S)提出的要求。 或:描述触发器的状态转换关系及转换条件的图形称为状态图 ·状态转换图与真值表是统一的,它是真值表的直观形象表示。 同步 RS 触发器的状态转换图如图 4-4 所示。 图 4-4 同步 RS 触发器的状态转换图 4、同步 RS 触发器的主要特点 (1)时钟电平控制。在 CP=1 期间接收输入信号,CP=0 时状态保持不变,与 基本 RS 触发器相比,对触发器状态的转变增加了时间控制。 (2)R、S 之间有约束。不能允许出现 R 和 S 同时为 1 的情况,否则会使触发器 处于不确定的状态。 2. 同步 D 触发器(D 锁存器) 为避免同步 RS 触发器同时出现 R 和 S 都为 1 的情况而设计。 1、电路结构和逻辑符号 如图 4-5 所示。 图 4-5 同步 D 触发器和逻辑符号 2、逻辑功能 将 S=D、R= D 代入同步 RS 触发器的特性方程,得同步 D 触发器的特性方程:

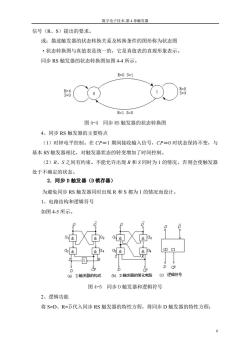

数字电子技术.第4章触发器 Q1=S+0 (CP=1期间有效) =D+DO"=D 由此,可得同步D触发器的特性表和驱动表。 状态转换图如右图4-6所示。 D-1 0 图4-6同步D触发器的状态转换图 3.同步JK触发器 1、电路结构、逻辑符号 如图4-7所示。 X白 图4-7同步JK触发器的电路及逻辑符号 2、功能分析 逻辑功能分析结果如特性表44所示。即: CP J KO" 功能 0 + P, Q1=Q”保持 0 Q+=0置0 0 Q=1置1 0 Q1=0”翻转 1 0 表44同步K触发器的特性表 JK=00时不变;JK=01时置0:

数字电子技术-第 4 章触发器 7 D DQ D Q S RQ n n n = + = = + +1 (CP=1 期间有效) 由此,可得同步 D 触发器的特性表和驱动表。 状态转换图如右图 4-6 所示。 图 4-6 同步 D 触发器的状态转换图 3. 同步 JK 触发器 1、电路结构、逻辑符号 如图 4-7 所示。 图 4-7 同步 JK 触发器的电路及逻辑符号 2、功能分析 逻辑功能分析结果如特性表 4-4 所示。即: 表 4-4 同步 JK 触发器的特性表 JK=00 时不变;JK=01 时置 0; CP J K Qn Q n+1 功能 0 × × × Q n n n Q = Q +1 保持 1 0 0 0 1 0 0 1 0 1 n n Q = Q +1 保持 1 0 1 0 1 0 1 1 0 0 0 1 = n+ Q 置 0 1 1 0 0 1 1 0 1 1 1 1 1 = n+ Q 置 1 1 1 1 0 1 1 1 1 1 0 n n Q = Q +1 翻转

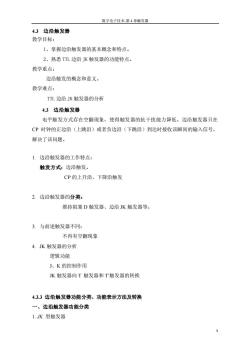

数字电子技术第4章触发器 K=10时置1:JK=11时翻转。 3、特性方程 将S=JQ”、R=KQ”代入同步RS触发器的特性方程,得同步JK触发器的特性 方程: Q1=S+0 =J0+ko"O" =J顶"+KQ (CP=1期间有效) 4、状态转换图 如图4-10所示. 國 &Go) O力 图48JK触发器状态转换图 在数字电路中,凡在CP时钟脉冲控制下,根据输入信号、K情况的不同,具有 置0、置1、保持和翻转功能的电路,都称为瓜触发器。 4.同步触发器的空翻 概念:同步触发器的空翻 在CP=1期间,如同步触发器的输入信号发生多次变化,则触发器的输出状态也会 相应的发生多次变化的现象。 同步触发器由于存在空翻,不能用于计数器、移位寄存器和存储器,只能用于数 据锁存。 ·讨论: 基本RS触发器的主要优缺点: 优点:电路简单,可以存储一位二进制代码,它是构成各种性能更完善的触发器 的基础。 缺点:输入端信号直接控制输出状态,无同步控制端:R、S端不能同时输入有 效信号,即R、S间存在约束

数字电子技术-第 4 章触发器 8 JK=10 时置 1;JK=11 时翻转。 3、特性方程 将 n S = JQ 、 n R = KQ 代入同步 RS 触发器的特性方程,得同步 JK 触发器的特性 方程: n n n n n n n JQ KQ JQ KQ Q Q S RQ = + = + = + +1 (CP=1 期间有效) 4、状态转换图 如图 4-10 所示。 图 4-8 JK 触发器状态转换图 在数字电路中,凡在 CP 时钟脉冲控制下,根据输入信号 J、K 情况的不同,具有 置 0、置 1、保持和翻转功能的电路,都称为 JK 触发器。 4. 同步触发器的空翻 概念:同步触发器的空翻 在 CP=1 期间,如同步触发器的输入信号发生多次变化,则触发器的输出状态也会 相应的发生多次变化的现象。 同步触发器由于存在空翻,不能用于计数器、移位寄存器和存储器,只能用于数 据锁存。 ⚫ 讨论: 基本 RS 触发器的主要优缺点: 优点:电路简单,可以存储一位二进制代码,它是构成各种性能更完善的触发器 的基础。 缺点:输入端信号直接控制输出状态,无同步控制端;RD、SD 端不能同时输入有 效信号,即 RD、SD间存在约束

数字电子技术-第4章触发器 4.3边沿触发器 教学目标: 1、掌握边沿触发器的基本概念和特点 2、熟悉TTL边沿JK触发器的功能特点。 教学重点: 边沿触发的概念和意义。 教学难点: TTL边沿JK触发器的分析 4.3边沿触发器 电平触发方式存在空翻现象,使得触发器的抗干扰能力降低。边沿触发器只在 CP时钟的正边沿(上跳沿)或者负边沿(下跳沿)到达时接收该瞬间的输入信号, 解决了该问题。 1.边沿触发器的工作特点: 触发方式:边沿触发。 CP的上升沿、下降沿触发 2.边沿触发器的分类: 维持阻塞D触发器、边沿K触发器等。 3.与前述触发器不同 不再有空翻现象 4.K触发器的分析 逻辑功能 」、K的控制作用 K触发器向T触发器和T触发器的转换 4.3.3边沿触发器功能分类、功能表示方法及转换 一、边沿触发器功能分类 1.JK型触发器

数字电子技术-第 4 章触发器 9 4.3 边沿触发器 教学目标: 1、掌握边沿触发器的基本概念和特点。 2、熟悉 TTL 边沿 JK 触发器的功能特点。 教学重点: 边沿触发的概念和意义。 教学难点: TTL 边沿 JK 触发器的分析 4.3 边沿触发器 电平触发方式存在空翻现象,使得触发器的抗干扰能力降低。边沿触发器只在 CP 时钟的正边沿(上跳沿)或者负边沿(下跳沿)到达时接收该瞬间的输入信号, 解决了该问题。 1. 边沿触发器的工作特点: 触发方式:边沿触发。 CP 的上升沿、下降沿触发 2. 边沿触发器的分类: 维持阻塞 D 触发器、边沿 JK 触发器等。 3. 与前述触发器不同: 不再有空翻现象 4. JK 触发器的分析 逻辑功能 J、K 的控制作用 JK 触发器向 T 触发器和 T’触发器的转换 4.3.3 边沿触发器功能分类、功能表示方法及转换 一、边沿触发器功能分类 1. JK 型触发器

数字电子技术第4章触发器 逻辑符号 JK触发器的特性表 JKC 000. 10 01 JK触发器的特性方程Q=J0,+Q 即在CP作用下,人、K取值不同时,具有保持、置0、置1、翻转功能的电路,都叫 做K型时钟触发器,简称瓜触发器 2.D型触发器 逻辑符号 D触发器的特性表 DQ1功能 ID CI 0 0 置0 D CP 1 置1 D触发器的特性方程Q=DCP上升沿时刻有效 在CP作用下,D取值不同时,具有置0、置1功能的电路,叫做D型时钟触发器 3.T型触发器 逻辑符号 T触发器的特性表 918@ TQ*功能 0 保持 T CP 1翻转 特性方程Q=TQ+TQ”=T⊕QCP下降沿有效 在CP作用下,当T=0时保持状态不变,T=1时状态翻转的电路叫T型时钟触发器。 4.T'型触发器一一只具有翻转功能的触发器 每来一个CP就翻转一次的电路叫T型时钟触发器 逻辑符号 特性方程Q1=Q”CP下降沿有效

数字电子技术-第 4 章触发器 10 逻辑符号 JK 触发器的特性表 JK 触发器的特性方程 n n 1 n Q JQ KQ + = + 即在 CP 作用下,J、K 取值不同时, 具有保持、置 0、置 1、翻转功能的电路,都叫 做 JK 型时钟触发器,简称 JK 触发器 2. D 型触发器 逻辑符号 D 触发器的特性表 D 触发器的特性方程 n 1 Q D + = CP 上升沿 时刻有效 在 CP 作用下,D 取值不同时,具有置 0、置 1 功能的电路,叫做 D 型时钟触发器。 3. T 型触发器 逻辑符号 T 触发器的特性表 特性方程 n n n n 1 Q TQ TQ T Q + = + = CP 下降沿有效 在 CP 作用下,当 T = 0 时保持状态不变,T =1 时状态翻转的电路叫 T 型时钟触发器。 4. T ’ 型触发器——只具有翻转功能的触发器 每来一个 CP 就翻转一次的电路叫 T ’型时钟触发器. 逻辑符号 特性方程 n n 1 Q Q + = CP 下降沿有效

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程试卷习题(自我检测)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第6章 脉冲产生和整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第5章 时序逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第4章 触发器.doc

- 内蒙古科技大学:《数字电子技术》课程设计指导书.doc

- 内蒙古科技大学:《数字电子技术》课程教学实验指导书(共八个实验).doc

- 内蒙古科技大学:《数字电子技术》课程实验教学大纲 Electronic Techniques Experiments.doc

- 内蒙古科技大学:《数字电子技术》课程教学大纲 Digital electric technology.doc

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第十章 可编程逻辑器件.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第六章 时序逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第八章 半导体存储器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第九章 数模与模数转换器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第七章 脉冲单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt