《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路

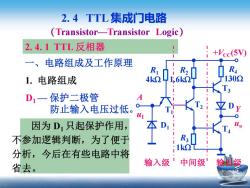

2.4TTL集成门电路 (Transistor-Transistor Logic) 2.4.1TTL反相器 +Vcc(5V) 电路组成及工作原理 1.电路组成 D1一保护二极管 A 防止输入电压过低。 D 因为D1只起保护作用, 本D1 不参加逻辑判断,为了便于 R3 :1k2t 分析,今后在有些电路中将 省去。 输入级'中间级” 输山级

2. 4 TTL 集成门电路 (Transistor—Transistor Logic) 2. 4. 1 TTL 反相器 一、电路组成及工作原理 +VCC(5V) R1 uI uo 4k A D1 T1 T2 T3 T4 D R2 1.6k R3 1k R4 130 Y 输入级 中间级 输出级 D1 — 保护二极管 防止输入电压过低。 当 uI < - 0.5 ~ - 0.7 V 时, D1 导通, uI 被钳制在 - 0.5 ~ - 0.7 V,不可能继 续下降。 1. 电路组成 因为 D1 只起保护作用, 不参加逻辑判断,为了便于 分析,今后在有些电路中将 省去

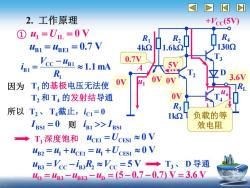

D☑I 2.工作原理 +Vcc(5V) ①4,=UL=0V 1R4 4g1=gE1=0.7V 4k2 1.6k2 宁1302 Vcc-ls1≈1.1mA 0.7V A R 应D 3.6 因为T的基极电压无法使 OV T,和T4的发射结导通 所以T2、T4截止,iC1=0 R3 1kQ7负载的等 Is1=0则i1>Igs1 效电阻 →T,深度饱和cEI=Ucs1≈0V UB2 =i+ucer =u +UCESI 0V 4B3=Vcc-B3R≈Vcc=5V→T3、D导通 0=4g3-g3-4=(5-0.7-0.7)V=3.6V

2. 工作原理 +VCC(5V) R1 uI uo 4k A T1 T2 T3 T4 D R2 1.6k R3 1k R4 130 Y uI = UIL = 0 V 1.1 mA 1 CC B 1 B 1 - = R V u i uB 1 = uBE1 = 0.7 V 0V T1 的基极电压无法使 T2 和 T4 的发射结导通 IBS1 = 0 B1 BS1 i I T1 深度饱和 uCE1 = UCES1 0 V uB 2 = uI + uCE1 = uI +UCES1 0 V T2 、 T4截止,iC1 = 0 RL 拉电流 uB 3 =VCC - i B 3R2 VCC = 5 V T3 、 D 导通 uO = uB 3 - uBE3 - uD = (5 - 0.7 - 0.7) V = 3.6 V 0V 3.6V 0V 0.7V 0V 负载的等 效电阻 5ViC1 因为 所以 则 ①

2.工作原理 +Vcc(5V) ②41=Um=3.6V T,倒置放大状态 kΩ .6k 1302 因为:uE>uB>uc, 即 2.1V 发射结反偏 0.3V应D 集电结正偏 3.6V T2饱和,T3、D均截止 0.7N T4饱和导通 uo=UcEs4≤0.3V 则 uNV Ho/V 所以 B:≈0.02 。大。 0 3.6 Y-A ie=R。ie=业以 3.6 0.3

+VCC(5V) R1 uI uo 4k A T1 T2 T3 T4 D R2 1.6k R3 1k R4 130 Y 2. 工作原理 e b c 因为 : uE> uB > uC ,即 发射结反偏 集电结正偏 i 0.02 i i = βi i ib =(1+ βi )ib 4.3V c e 3.6 V 1.4V 0.7V 2.1V ② uI = UIH = 3.6 V T1 倒置放大状态 T2 饱和,T3 、D 均截止 T4 饱和导通 uO = UCES4 ≤ 0.3V 1V 0.3V 0.3 uI /V uO/V 0 3.6 3.6 0.3 则 所以 Y = A

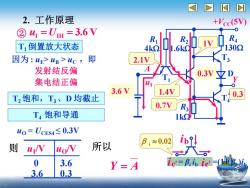

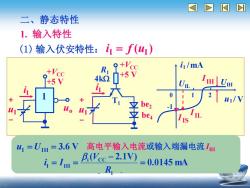

D I 二、静态特性 1.输入特性 (1)输入伏安特性:i=f(4) +Vcc R i/mA +5V 4k2 IH U be2 w/八 es 41=U1m=3.6V高电平输入电流或输入端漏电流1m =1m= B(Vcc-2.1V) =0.0145m4 R

输入短路电流IIS 二、静态特性 1. 输入特性 (1) 输入伏安特性: ( ) I uI i = f 1 i I +VCC +5 V uI + - uo T1 i I uI + - be2 be4 +VCC +5 V R1 4k uI / V iI /mA 0 1 2 -1 uI = UIL = 0V 1.05mA 1 CC BE1 I I S = - - = = - R V u i I uI = UIL = 0.3V 1 mA 1 CC BE1 I L I I L = - - - = = - R V u U i I IS I IL I UIL UIH IH I 低电平输入电流I uI = UI H = 3.6 V IL 0.0145 mA ( 2.1V) 1 i CC I I H = - = = R V i I 高电平输入电流或输入端漏电流IIH

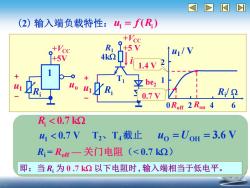

(2)输入端负载特性:4=f(R) +Vcc +V r1+5V u/V +5V 1.4V 立be2 0.7V R/2 0Roft 2 Ron 4 6 R<0.7k2 41<0.7VT2、T4截止 uo =UoH =3.6 V R:=Rr一关门电阻(<0.7k2) 即:当R为0.7kΩ以下电阻时,输入端相当于低电平

即:当 Ri 为 2.5 k 以上电阻时,输入由低电平变为高电平 (2) 输入端负载特性: ( ) I Ri u = f 1 +VCC +5V uI + - uo Ri T1 iB1 uI + - be2 be4 +VCC R1 +5 V 4k Ri Ri / 0 2 4 6 1 2 uI / V 2. 5 k ~ ( ) Ri = 悬空 uI 1.4V T2、T4饱和导通 uO = UOL 0.3V Ri = Ron — 开门电阻(2.5 kΩ) Ron Ri 0.7 k uI 0.7 V T2、T4 截止 uO = UOH = 3.6 V Ri = Roff — 关门电阻(< 0.7 k) 即:当 Ri 为 0 .7 k 以下电阻时, 输入端相当于低电平。 Roff 0.7 V 1.4 V

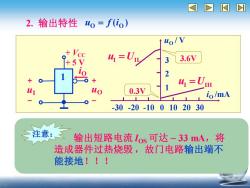

2.输出特性uo=f(io) +Vcc +5V 3 3.6V 2 4,=U 0.3V io/mA -30-20-100102030 注意: 输出短路电流Ios可达-33mA,将 造成器件过热烧毁,故门电路输出端不 能接地!!!

2. 输出特性 uO = f (i O ) uO 1 + VCC + 5 V uI + - + - iO uO / V iO /mA -30 -20 -10 0 10 20 30 1 2 3 (1) , : uI = UIH uO = UOL 在输出为低电平条件下,带灌 电流负载能力 IOL 可达 16 mA uI = UIH 0.3V (2) , : uI = UIL uO = UOH 受功耗限制,带拉电流负载能 力 IOH 可一般为 - 400 A uI = UIL 3.6V 注意: 输出短路电流 IOS 可达 - 33 mA,将 造成器件过热烧毁 ,故门电路输出端不 能接地!!!

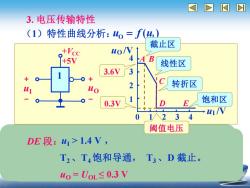

I 3.电压传输特性 (1)特性曲线分析:Wo=f(4) 截止区 +V uo/V +5V 4 线性区 3.6V C 转折区 0.3V D 饱和区 uI/V 0 1Λ23 4 阈值电压 DE段:w1>1.4V, T2、T4饱和导通,T3、D截止。 uo=UoL≤0.3V

3. 电压传输特性 ( ) O uI u = f 1 +VCC +5V uI + - uO + - A B 0 uO /V uI /V 1 2 3 4 1 2 3 4 AB 段:uI 1.4 V , T2 、T4 饱和导通, T3 、D 截止。 uO = UOL ≤ 0.3 V 阈值电压 (1)特性曲线分析:

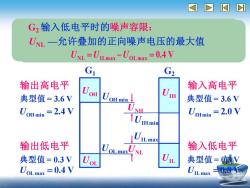

D G2输入低电平时的噪声容限: UL一允许叠加的正向噪声电压的最大值 UNL=UILmax-UoLmax =0.4V G 输出高电平 输入高电平 典型值=3.6V UOH min 典型值=3.6V UoH min =2.4 V U NH Utmin=2.0 V IL max 输出低电平 输入低电平 典型值=0.3V 典型值=储V UOL max =0.4V UILmax 08

(2)输入端噪声容限 1 uO uI G1 G2 1 UIHmin UILmax UNH UNL UOH UOL UOH min UOL max UIH UIL 输出高电平 UOH min = 2.4 V 典型值 = 3.6 V 输出低电平 UOL max = 0.4 V 典型值 = 0.3 V 输入高电平 UIHmin = 2.0 V 典型值 = 3.6 V 输入低电平 UILmax = 0.8 V 典型值 = 0.3 V UNH —允许叠加的负向噪声电压的最大值 G2 输入高电平时的噪声容限: UN H = UOHmin -UIHmin = 0.4 V UNL —允许叠加的正向噪声电压的最大值 G2 输入低电平时的噪声容限: UN L = UILmax -UOLmax = 0.4 V

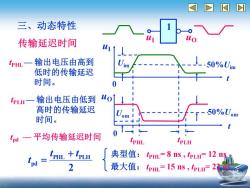

I 三、动态特性 传输延迟时间 pHL一 输出电压由高到 -↓_.50%Uim 低时的传输延迟 时间。 tpLH一 输出电压由低到 uo 高时的传输延迟 50%Uom 时间。 1一平均传输延迟时间 LPHL PLH 典型值:p=8ns,pH12nS 2 最大值:tpH=15ns,pH22的

三、动态特性 传输延迟时间 1 uI uO 50%Uom 50%Uim t uI 0 t uO 0 Uim Uom tPHL— 输出电压由高到 低时的传输延迟 时间。 tpd — 平均传输延迟时间 2 PHL PLH pd t t t + = tPLH— 输出电压由低到 高时的传输延迟 时间。 tPHL tPLH 典型值: tPHL= 8 ns , tPLH= 12 ns 最大值: tPHL= 15 ns , tPLH= 22 ns

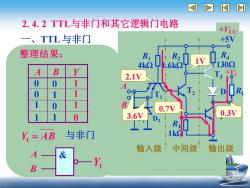

I 2.4.2TTL与非门和其它逻辑门电路 +Vcc 一、TTL与非门 +5V 整理结果: 4k2 302 A B 2.1V 0.7 3.6V 0.3V Y=AB 与非门 1k 输入级·中间级: 输出级

+VCC +5V R1 4k A D2 T1 T2 T3 T4 D R2 1.6k R3 1k R4 130 Y 输入级 中间级 输出级 D1 B T1 — 多发射极三极管 e1 e2 b c 等效电路: 1. A、B 只要有一个为 0 0.3V 1V uB 1 = (0.3 + 0.7) V = 1 V T2 、 T4截止 5V T3 、 D 导通 3.6 V O (5 0.7 0.7) V = u - - 3.6V uA = uB = 0.3 V uA = 0.3 V , uB = 3.6 V uA = 3.6 V , uB = 0.3 V 2. 4. 2 TTL与非门和其它逻辑门电路 一、TTL 与非门 2. A、B 均为 1 uA = uB = 3.6 V 理论: uB 1 = (3.6 + 0.7) V = 4.3 V 实际: uB 1 = (30.7) V = 2.1 V T2 、 T4 导通 T3 、 D 截止 uO = UCES4 ≤ 0.3V 3.6V 0.7V 1V 0.3V 4.3V +VCC +5V 4k A D2 T1 T2 T3 T4 D 1.6k 1k 130 Y 输入级 中间级 输出级 D1 B R1 R2 R3 R4 3.6V 4.3V 21 RL +VC C 0.7V 1V 0.3V 整理结果: 1 1 1 0 A B Y 0 0 0 1 1 0 1 1 Y1 = AB 与非门 A B Y1 &

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt