《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结

第二章小结 一、半导体二极管、三极管和MOS管 是数字电路中的基本开关元件,一般都工作在开关状态。 1.半导体二极管:是不可控的,利用其开关特性可构成 二极管与门和或门。 2.半导体三极管:是一种用电流控制且具有放大特性的开 关元件,利用三极管的饱和导通与截止 特性可构成非门和其它TTL集成门电 路。 3.MOS管:是一种具有放大特性的由电压控制的开关元件, 利用N沟道MOS管和P沟道MOS管可湘成 CMOS反相器和其它CMOS集成门电路

第二章 小结 一、半导体二极管、三极管和 MOS 管 是数字电路中的基本开关元件,一般都工作在开关状态。 1. 半导体二极管:是不可控的,利用其开关特性可构成 二极管与门和或门。 2. 半导体三极管:是一种用电流控制且具有放大特性的开 关元件, 利用三极管的饱和导通与截止 特性可构成非门 和其它 TTL 集成门电 路。 3. MOS管:是一种具有放大特性的由电压控制的开关元件, 利用 N 沟道 MOS 管和 P 沟道 MOS 管可构成 CMOS 反相器和其它CMOS 集成门电路

冈I 二、分立元件门电路 主要介绍了由半导体二极管、三极管和MOS 管构成的与门、或门和非门。 虽然,分立元件门电路不是本章的重点,但是 通过对这些电路的分析,可以体会到与、或、非三 种最基本的逻辑运算,是如何用半导体电子电路实 现的,这将有助于后面集成门电路的学习

二、分立元件门电路 主要介绍了由半导体二极管、三极管和 MOS 管构成的与门、或门和非门。 虽然,分立元件门电路不是本章的重点,但是 通过对这些电路的分析,可以体会到与、或、非三 种最基本的逻辑运算,是如何用半导体电子电路实 现的,这将有助于后面集成门电路的学习

三、集成门电路一本章重点 主要介绍了CMOS和TTL集成门电路,重点应 放在它们的输出与输入之间的逻辑特性和外部电气特 性上。 1.逻辑特性(逻辑功能): 普通功能一与门、或门、非门、与非门、或非门、与或非 门和异或门。 特殊功能一三态门、OC门、OD门和传输门。 2.电气特性: 静态特性一主要是输入特性、输出特性和传输特性。 动态特性一主要是传输延迟时间的概念

三、集成门电路 — 本章重点 主要介绍了 CMOS 和 TTL 集成门电路,重点应 放在它们的输出与输入之间的逻辑特性和外部电气特 性上。 1. 逻辑特性(逻辑功能): 普通功能 — 与门、或门、非门、与非门、或非门、与或非 门和异或门。 特殊功能 — 三态门、OC门、OD门和传输门。 2. 电气特性: 静态特性 — 主要是输入特性、输出特性和传输特性。 动态特性 — 主要是传输延迟时间的概念

D 四、集成门电路使用中应注意的几个问题 分类 TTL CMOS 工作电源 Vcc =5V D=3~18V 输出电平 UOL=0.3 V UoH=3.6 V UoL≈0VUoH≈D 阈值电压 UT=1.4 V UTH=0.5 VDD 输入端串 当R>Rm(2.5k2) 在一定范围内,R的改 接电阻R 输入由0→1 变不会影响输入电平 输入端 即R=o0 悬空 输入为“1” 灸 多余输入 1.与门、与非门接电源;或门、或非门接地。 端的处理 2.与其它输入端并联

四、集成门电路使用中应注意的几个问题 分类 TTL CMOS 工作电源 VCC = 5 V VDD = 3 18 V 输出电平 UOL= 0.3 V UOH = 3.6 V UOL 0 V UOH VDD 阈值电压 UTH = 1.4 V UTH = 0.5 VDD 输入端串 接电阻Ri 当 Ri > Ron(2.5 k ) 输入由 0 → 1 在一定范围内,Ri的改 变不会影响输入电平 输入端 悬空 即 Ri = 输入为 “1” 不允许 多余输入 端的处理 1. 与门、与非门接电源;或门、或非门接地。 2. 与其它输入端并联

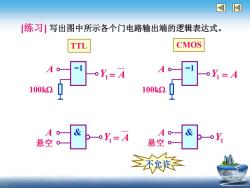

[练习]写出图中所示各个门电路输出端的逻辑表达式。 TTI CMOS oY=1 100k2 100k2

[练习] 写出图中所示各个门电路输出端的逻辑表达式。 TTL CMOS A & Y1 100k 100 = = 1 A A & Y1 100k 100 = 1 A ≥1 Y1 100k 100 = A A ≥1 Y1 100k 100 = 0 = A

练习]写出图中所示各个门电路输出端的逻辑表达式。 TTL CMOS oY=A 100k2 &

[练习] 写出图中所示各个门电路输出端的逻辑表达式。 TTL CMOS A =1 Y1 100k 100 = A A =1 Y1 100k 100 = A = A A & 悬空 Y1 A & 悬空 Y1 不允许 = A

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt