《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器

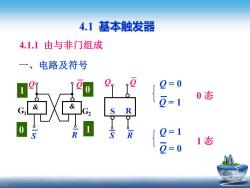

4.1基本触发器 4.1.1由与非门组成 一、电路及符号 2=0 0=1 0态 0=1 0=0 1态

G2 4.1 基本触发器 4.1.1 由与非门组成 一、电路及符号 Q G1 R & & S Q Q Q S R S R Q = 0 Q = 1 0 态 Q = 1 Q = 0 1 态 1 0 0 1 0 1 1 0

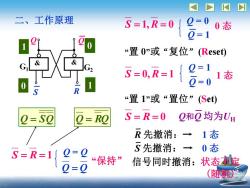

I 二、工作原理 S=1,R=0 2=00态 0=1 “置0”或“复位”(Reset) 5=-0R=1{81态 “置1”或“置位”(Set) Q-50 S=R=0 Q和2均为UH R先撤消:一1态 先撤消: →0态 s=R=1{8=8 0=0 “保持” 信号同时撤消: 状态剂定 (随机

G2 Q G1 R & & S Q Q = SQ Q = RQ 二、工作原理 S = R = 1 Q = Q Q = Q “保持” S = 1,R = 0 1 0 0 1 Q = 0 Q = 1 0 态 “置 0”或“复位”(Reset) S = 0,R = 1 0 1 1 0 Q = 1 Q = 0 1 态 “置 1”或“置位”(Set) S = R = 0 Q和Q 均为UH R 先撤消: 1 态 S 先撤消: 0 态 信号同时撤消:状态不定 (随机)

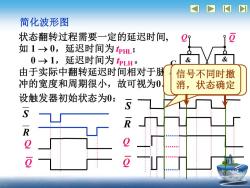

简化波形图 状态翻转过程需要一定的延迟时间, 如1→0,延迟时间为p; 0→1,延迟时间为pLH。 & 由于实际中翻转延迟时间相对于脉 信号不同时撤 冲的宽度和周期很小,故可视为0 消,状态确定 设触发器初始状态为0: s S F

简化波形图 状态翻转过程需要一定的延迟时间, 如 1 → 0,延迟时间为 tPHL; 0 → 1,延迟时间为 tPLH 。 由于实际中翻转延迟时间相对于脉 冲的宽度和周期很小,故可视为0。 Q G1 R & & S Q 设触发器初始状态为0: S R Q Q S R Q Q 信号同时撤消,出 现不确定状态 信号不同时撤 消,状态确定

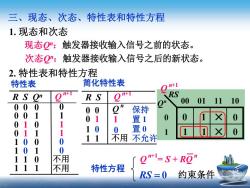

三、现态、次态、特性表和特性方程 1.现态和次态 现态Q:触发器接收输入信号之前的状态。 次态Q”:触发器接收输入信号之后的新状态。 2.特性表和特性方程 特性表 简化特性表 O1 R S On RS RS 00 01 11 10 00 0 0 00 保持 001 1 01 1 置1 010 1 011 1 1 0 0 置0 100 0 11 不用不允许 101 0 110 不用 2=S+RO 111 不用 特性方程 RS=0 约束条件

三、现态、次态、特性表和特性方程 1. 现态和次态 现态Qn:触发器接收输入信号之前的状态。 次态Qn:触发器接收输入信号之后的新状态。 2. 特性表和特性方程 R S Qn Q n+1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 1 1 1 0 0 不用 不用 特性表 简化特性表 R S Q n+1 0 0 0 1 1 0 1 1 Q n 保持 1 置 1 0 置 0 不用 不允许 RS 0 1 Q n 00 01 11 10 Q n+1 0 1 1 1 0 0 Q n+1 = S + RQ n RS = 0 约束条件 特性方程

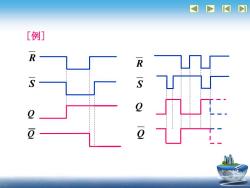

I [例] R R -S

[ 例 ] SR QQ RSQQ

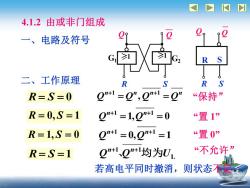

I 4.1.2由或非门组成 一、电路及符号 R S 二、工作原理 R R R=S=0 2+1=Q",Q+1=Q” “保持” R=0,S=1 2+1=1,Q+1=0 “置1” R=1,S=0 2"+1=0,Q+1=1 “置0” R=S=1 Q+1、2+1均为U, “不允许” 若高电平同时撤消,则状态不定

4.1.2 由或非门组成 一、电路及符号 Q Q R S 二、工作原理 R S R = S = 0 n n n n Q = Q Q = Q +1 +1 , R = 0, S = 1 1, 0 1 1 = = n+ n+ Q Q R = 1, S = 0 0, 1 1 1 = = n+ n+ Q Q R = S = 1 L 1 1 Q Q U n+ 、 n+ 均为 “保持” “置 0” “置 1” “不允许” 若高电平同时撤消,则状态不定。 G2 Q G1 R S Q >1 >1

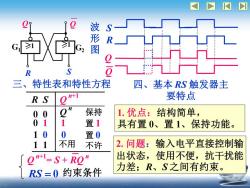

I 波形图 三、特性表和特性方程 四、基本RS触发器主 RS + 要特点 00 保持 1.优点:结构简单, 01 1 置1 具有置0、置1、保持功能。 10 0 置0 11 不用 不许 2.问题:输入电平直接控制输 出状态,使用不便,抗干扰能 RS=0约束条件 力差;R、S之间有约束

S R Q Q 三、特性表和特性方程 R S Q n+1 0 0 0 1 1 0 1 1 Q n 保持 置 1 置 0 不许 1 0 不用 Q n+1 = S + RQ n RS = 0 约束条件 四、基本 RS 触发器主 要特点 1. 优点:结构简单, 具有置 0、置 1、保持功能。 2. 问题:输入电平直接控制输 出状态,使用不便,抗干扰能 力差;R、S 之间有约束。 G2 Q G1 R S Q >1 >1 波 形 图

4.1.3集成基本触发器 一、 CMOS集成基本触发器 1.由与非门组成:CC4044 +Vcc 16 EN 1R R图 3 SA 1Q 1 。5 1 2 74279 2Q EN 。6 10 c 2S741S279 3 & 5。 2、 o山d 3SA EN p 4。 4R 40 15 4S EN 8 内含4个基本RS触发器 2.由或非门组成:CC4043(略)

4.1.3 集成基本触发器 一、CMOS 集成基本触发器 1. 由与非门组成:CC4044 & & 1 R TG S ENEN Q 1 1 EN EN EN 三态 RS 锁存触发器特性表 R S EN Q n+1 注 0 Z 高阻态 0 0 1 0 1 1 1 0 1 1 1 1 Q n 保 持 置 1 置 0 不允许 1 0 不用 内含 4 个基本 RS 触发器 2. 由或非门组成:CC4043(略) +VCC 1R 1SA 1SB 2R 2S 3R 3SA 3SB 4R 4S 1Q 2Q 3Q 4Q 1 2 3 5 6 10 11 12 14 15 4 7 9 13 Q1 Q2 Q3 Q4 8 16 74279 74LS279 R1 S11 S12 R2 S2 R3 S31 S32 R4 S4 – – – – – – – – – –

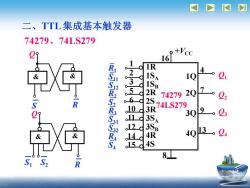

二、TTL集成基本触发器 74279、74LS279 1R P世 1Q 2R 74279 2Q 06d 2S 10。 3R 74LS279 23 o11 c 3S 3Q 3SB 4R 130 15。 4S 8 S1 S2

二、TTL 集成基本触发器 74279、74LS279 Q R & & S Q R & & S1 S2 +VCC 1R 1SA 1SB 2R 2S 3R 3SA 3SB 4R 4S 1Q 2Q 3Q 4Q 1 2 3 5 6 10 11 12 14 15 4 7 9 13 Q1 Q2 Q3 Q4 8 16 74279 74LS279 R1 S11 S12 R2 S2 R3 S31 S32 R4 S4 – – – – – – – – – –

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH63 多谐振荡器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 SUM6 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH70 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH71 D/A转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH72 A/D转换器.ppt