《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器

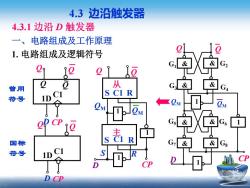

4.3边沿触发器 4.3.1边沿D触发器 一、电路组成及工作原理 1.电路组成及逻辑符号 曾用 从 符号 1D S C1 R 2M Gs& 国标 R G& & 符号 0 CE 0

4.3 边沿触发器 4.3.1 边沿 D 触发器 一、电路组成及工作原理 QM QM CP S R Q Q S C1 R S C1 R 1 1 1 D G7 CP Q & & Q G3 & & D G2 G4 & & & & G6 G8 1 G1 G5 1 1 QM QM 从 主 曾用 符号 国标 符号 Q Q CP C1 1D D Q Q CP C1 1D D Q Q 1. 电路组成及逻辑符号

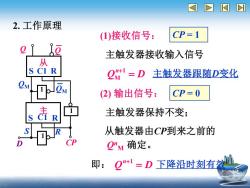

DI 2.工作原理 (1)接收信号: CP=1 主触发器接收输入信号 从 2'=D 主触发器跟随D变化 2M (2)输出信号: CP=0 主 主触发器保持不变; 从触发器由CP到来之前的 Q"M确定。 即:Q+1=D下降沿时刻有效

2. 工作原理 (1)接收信号: CP = 1 主触发器接收输入信号 Q D n = +1 M 主触发器跟随D变化 (2) 输出信号: CP = 0 主触发器保持不变; 从触发器由CP到来之前的 Qn M 确定。 QM QM CP S R Q Q S C1 R S C1 R 1 1 1 D 从 主 即: Q D n = +1 下降沿时刻有效

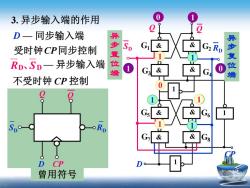

3.异步输入端的作用 D一同步输入端 异 受时钟CP同步控制 Sp G2 RD RD、SD一异步输入端 位 步复位端 不受时钟CP控制 ● D CP 曾用符号

3. 异步输入端的作用 G7 CP Q & & Q G3 & & D G2 G4 & & & & G6 G8 1 G1 G5 1 1 D — 同步输入端 受时钟CP同步控制 SD RD RD、S D — 异步输入端 不受时钟 CP 控制 0 1 直 接 置 位 端 直 接 复 位 端 异 步 置 位 端 异 步 复 位 端 国标符号 曾用符号 SD D CP RD – – Q Q 1 1 1 0 1 0 01 10 0 1 0 1 1 1 – – SD RD D CP Q Q

4.波形 CP CP 触发器的初始0状态可利用异步复位端接低电平实现

4. 波形 Q Q CP C1 1D D 触发器的初始 0 状态可利用异步复位端接低电平实现

二、集成边沿D触发器 1.CMOS边沿D触发器 CC4013(双D触发器) 1 11 992 符号 引出端 12 132 C1 R 功能 14 ss 特性表 SDD CP RD 653489110 CP2. CP D Rp Qn+1 注 D D Sp 个 0 0 0 同步置0 0 1 同步置1 CP上升沿触发 个 1 0 Qn 保持八无效) 0 异步置1 0 异步置0 0 不 不允许

二、 集成边沿D 触发器 1. CMOS 边沿 D 触发器 CC4013 (双 D 触发器) 符号 引出端 功能 Q1 Q1 VDD SD1 CP1 SD2 CP2 D1 RD1 D2 RD2 Q2 Q2 VSS 6 5 3 4 8 9 11 10 1 2 13 12 14 7 特性表 CP D RD SD Qn+1 注 0 0 0 1 0 0 0 0 0 0 1 Qn 1 0 不用 同步置0 同步置1 保持(无效) 异步置1 异步置0 不允许 CP 上升沿触发 Q Q CP C1 1D D S R SD RD

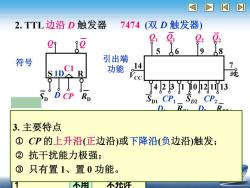

I 2.TTL边沿D触发器 7474(双D触发器) 91 2 02 6 08 符号 引出端 、C1 SIDR 功能 14 地 423 1012113 Sp D CP Rp 3.主要特点 ① CP的上升沿(正边沿)或下降沿(负边沿)触发; ②抗干扰能力极强; ③ 只有置1、置0功能。 不用 不分旺

2. TTL 边沿 D 触发器 7474 (双 D 触发器) 符号 引出端 功能 特性表 CP D RD SD Qn+1 注 0 1 1 1 1 1 1 1 0 0 1 Qn 0 1 不用 同步置0 同步置1 保持(无效) 异步置0 异步置1 不允许 Q1 Q1 VCC SD1 CP1 SD2 CP2 D1 RD1 D2 RD2 Q2 Q2 地 4 2 3 1 10 12 11 13 5 6 9 8 14 7 – – – – – – 3. 主要特点 CP 的上升沿(正边沿)或下降沿(负边沿)触发; 抗干扰能力极强; 只有置 1、置 0 功能。 Q Q CP C1 1D D S R SD RD

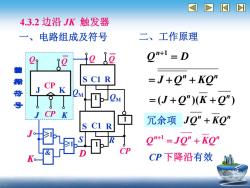

4.3.2边沿JK触发器 一、电路组成及符号 二、工作原理 Q"+1=D =J+Q”+KQ” 符号 =(J+2”)K+2") CP K 1 冗余项JQ”+KQ” Q+1=JQ"+KQ” CP下降沿有效

4.3.2 边沿 JK 触发器 一、电路组成及符号 二、工作原理 QM QM CP S R Q Q S C1 R S C1 R 1 1 1 D >1 >1 & J K Q D n = +1 n n = J +Q + KQ ( )( ) n n = J + Q K + Q n n = JK + JQ + KQ n n n Q = JQ + KQ +1 冗余项 国 标 符 号 Q Q CP C1 1J IK J K Q Q CP CP J K J K 曾 用 符 号 CP 下降沿有效

I 二、集成边沿JK触发器 1.CMOS边沿JK触发器 CC4027 29 1 0 02 国 1 2 ¥15 014 标 16 号 SpJ CP KRp K1 Sp2 CP2 Rp2 2 SDI CPI RDI 曾用符号 - S Sp CP p Rp 引出端功能 CP

二、 集成边沿 JK 触发器 1. CMOS 边沿 JK 触发器 CC4027 国 标 符 号 曾 用 符 号 Q Q CP C1 1J IK J K S R SD RD Q Q CP CP J K J K SD RD SD RD 引出端功能 Q1 Q1 VDD J1 K1 SD2 CP2 RD2 SD1 CP1 RD1 J2 K2 Q2 Q2 VSS 7 6 3 5 4 9 10 13 1112 1 2 15 14 16 8

特性表 K Qn Rp Sp Q+1 注 CP 0 0 0 0 0 保持 1 0 0 同步置0. 0 1 同步置1- 1 0 翻 转

J K Qn RD SD CP Q n+1 注 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 0 01001110 保 持 同步置 0 同步置 1 翻 转 特 性 表

I 2.TTL边沿JK触发器74LS112(双JK触发器) ·CP下降沿触发 ·异步复位端D、异步置位端S,均为低电平有效 3.主要特点 ①CP的上升沿或下降沿触发; ②抗干扰能力极强,工作速度很高,在触发沿瞬间, 按 Q"+1=JQ”+规定更新状态; ③功能齐全(保持、置1、置0、翻转),使用方便

2. TTL 边沿 JK 触发器 • CP 下降沿触发 • 异步复位端 RD、异步置位端 SD 均为低电平有效 74LS112 (双 JK 触发器) 3. 主要特点 CP 的上升沿或下降沿触发; 抗干扰能力极强,工作速度很高,在触发沿瞬间, 按 的规定更新状态; n n n Q = JQ + KQ +1 功能齐全(保持、置 1、置 0、翻转),使用方便

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH63 多谐振荡器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 SUM6 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH70 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH71 D/A转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH72 A/D转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 SUM7 小结.ppt

- 西安邮电大学:《现代通信网》课程教学大纲 Modern Communication Network C.doc