《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路

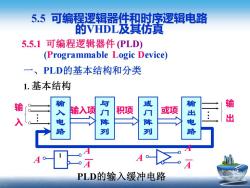

5.5可编程逻辑器件和时序逻辑电路 的VHDL及其仿真 5.5.1可编程逻辑器件(PLD) (Programmable Logic Device) 一、 PLD的基本结构和分类 1.基本结构 输 输 输入项 积项 武 或项 电 阵 阵 输出电 出 列 A PLD的输入缓冲电路

5.5.1 可编程逻辑器件 (PLD) (Programmable Logic Device) 一、PLD的基本结构和分类 1. 基本结构 输 入 电 路 与 门 阵 列 或 门 阵 列 输 出 电 路 • • • • • • 输 入 输入项 积项 或项 输 出 1 A A A A A A PLD的输入缓冲电路 5.5 可编程逻辑器件和时序逻辑电路 的VHDL及其仿真

✉D冈I 2.分类 ()按可编程情况分 分类 与阵列 或阵列 输出电路 出现年代 PROM 固定 可编程 固定 70年代初 PLA 可编程 可编程 固定 70年代中 PAL 可编程 固定 固定 70年代末 GAL 可编程 固定 可组态 80年代初

2. 分类 (1) 按可编程情况分 分 类 与阵列 或阵列 输出电路 出现年代 PROM 固定 可编程 固定 70年代初 PLA 可编程 可编程 固定 70年代中 PAL 可编程 固定 固定 70年代末 GAL 可编程 固定 可组态 80年代初

PROM 可编程只读存储器 (Programmable Read Only Memory) 2110 或阵列 可编程) 缺点: ·只能实现标准 与或式 ·芯片面积大 ·利用率低,不经济 用途: ·存储器 ·函数表 与阵列 显示译码电路 (固定)

● PROM — 可编程只读存储器 I2 I1 I0 O2 O1 O 0 与阵列 (固定) 或阵列 (可编程) 缺点: • 只能实现标准 与或式 • 芯片面积大 • 利用率低,不经济 用途: • 存储器 • 函数表 • 显示译码电路 (Programmable Read Only Memory)

●PLA 可编程逻辑阵列 (Programmable Logic Array) 或阵列 (可编程) 优点: ·与阵列、或阵列 米米 都可编程 能实现最简与或式 缺点: 。 价格较高 ·门的利用率不高 与阵列 (可编程) 020100

● PLA — 可编程逻辑阵列 I2 I1 I0 O2 O1 O 0 与阵列 (可编程) 或阵列 (可编程) 优点: • 与阵列、或阵列 都可编程 • 能实现最简与或式 缺点: • 价格较高 • 门的利用率不高 (Programmable Logic Array)

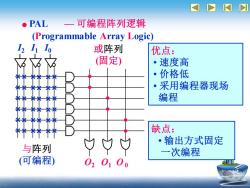

●PAL - 可编程阵列逻辑 (Programmable Array Logic) 2I10 或阵列 优点: (固定) ·速度高 米米米米米 ·价格低 ·采用编程器现场 编程 缺点: •输出方式固定 与阵列 一次编程 (可编程) 020100

● PAL — 可编程阵列逻辑 I2 I1 I0 O2 O1 O 0 与阵列 (可编程) 或阵列 (固定) 优点: • 速度高 • 价格低 • 采用编程器现场 编程 缺点: • 输出方式固定 一次编程 (Programmable Array Logic)

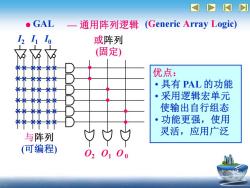

●GAL 通用阵列逻辑(Generic Array Logic) 210 或阵列 衣✉ (固定) 米一 优点: ·具有PAL的功能 ·采用逻辑宏单元 使输出自行组态 ·功能更强,使用 与阵列 的夕为 灵活,应用广泛 (可编程) 020100

● GAL — 通用阵列逻辑 I2 I1 I0 O2 O1 O 0 与阵列 (可编程) 或阵列 (固定) 优点: • 具有 PAL 的功能 • 采用逻辑宏单元 使输出自行组态 • 功能更强,使用 灵活,应用广泛 (Generic Array Logic)

(2)按可编程和改写方法分 PLD 编程方式 改写方法 特点、用途 第一代 一次性掩模 不能改写 固定程序、数据、函 (厂家) 数表、字符发生器 第二代 编程器(用户) 紫外光擦除 先擦除,后编程 第三代 编程器(用户) 电擦除 擦除、编程同时进行 第四代 在系统可编程 软件 直接在目标系统或线 路板上编程 3) 按组合、时序分 组合 PROM、PLA 时序 时序型PAL 电路 组合型PAL 电路 GAL(也可实现组合电路)

(2) 按可编程和改写方法分 PLD 编程方式 改写方法 特点、用途 第一代 一次性掩模 (厂家) 不能改写 固定程序、数据、函 数表、字符发生器 第二代 编程器(用户) 紫外光擦除 先擦除,后编程 第三代 编程器(用户) 电擦除 擦除、编程同时进行 第四代 在系统可编程 软件 直接在目标系统或线 路板上编程 (3) 按组合、时序分 组合型 PAL 组合 电路 PROM、 PLA 时序 电路 时序型 PAL GAL (也可实现组合电路)

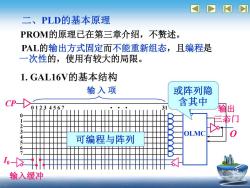

二、PLD的基本原理 PROM的原理已在第三章介绍,不赘述。 PAL的输出方式固定而不能重新组态,且编程是 一次性的,使用有较大的局限。 1.GAL16V的基本结构 输入项 或阵列隐 含其中 输出 0 三态门 可编程与阵列 输入缓冲

二、PLD的基本原理 PROM的原理已在第三章介绍,不赘述。 PAL的输出方式固定而不能重新组态,且编程是 一次性的,使用有较大的局限。 1. GAL16V的基本结构 I0 0 1 2 3 4 5 6 7 • • • 31 0 1 2 3 4 5 6 7 O 输 入 项 CP OLMC • 可编程与阵列 输入缓冲 输出 三态门 或阵列隐 含其中

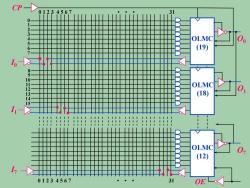

CP- 01234567 (19) OLMC (18) OLMC (12) 01234567 OE

I0 0 1 2 3 4 5 6 7 • • • 31 01234567 O 0 CP OLMC (19) • O 1 OLMC (18) • 89 10 11 12 13 14 15 I1 • O 7 OLMC (12) • OE • I7 0 1 2 3 4 5 6 7 • • • 31

I 2.输出逻辑宏单元 输出逻辑宏单元(OLMC一Out Logic Cell) ·OLMC有5种不同的输出组态 ·5种输出组态由结构控制字来决定 ·通过编程对GAL芯片内部的结构控制字寄存器 进行设置

2. 输出逻辑宏单元 输出逻辑宏单元 (OLMC — Out Logic Cell) • OLMC 有 5 种不同的输出组态 • 5种输出组态由结构控制字来决定 • 通过编程对GAL芯片内部的结构控制字寄存器 进行设置

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH63 多谐振荡器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 SUM6 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH70 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH71 D/A转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH72 A/D转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 SUM7 小结.ppt

- 西安邮电大学:《现代通信网》课程教学大纲 Modern Communication Network C.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第一章 绪论.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第二章 传送网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第三章 数据链路层.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第五章 同步网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第六章 电话网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第四章 No.7信令网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第八章 分组网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第十一章 计算机网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第十二章 宽带综合IP网.doc