《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM)

3.6只读存储器 (ROM) 掩模ROM 分类 可编程ROM(PROM一Programmable ROM) 可擦除可编程ROM(EPROM一Erasable PROM) 说明: 掩模ROM 生产过程中在掩模板控制下写入,内容固定, 不能更改 PROM 内容可由用户编好后写入,一经写入不能更改 紫外光擦除(约二十分钟) EPROM 存储数据可以更改,但改写麻烦,工作时只读 EEPROM或E2PROM电擦除(几十毫秒)

3.6 只读存储器(ROM) 分类 掩模 ROM 可编程 ROM(PROM — Programmable ROM) 可擦除可编程ROM(EPROM — Erasable PROM) 说明: 掩模 ROM PROM 生产过程中在掩模板控制下写入,内容固定, 不能更改 内容可由用户编好后写入,一经写入不能更改 紫外光擦除(约二十分钟) EPROM 存储数据可以更改,但改写麻烦,工作时只读 EEPROM 或 E2PROM 电擦除(几十毫秒)

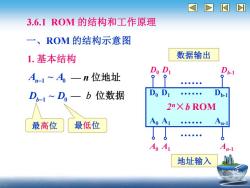

☒DI 3.6.1ROM的结构和工作原理 一、ROM的结构示意图 1.基本结构 数据输出 Do Di An-1~A一n位地址 。●●●●● D-1~D,一b位数据 Do D1 2nX b ROM 最高位 最低位 Ao A1 地址输入

3.6.1 ROM 的结构和工作原理 1. 基本结构 一、ROM 的结构示意图 地址输入 数据输出 An−1 ~ A0 — n 位地址 Db−1 ~ D0 — b 位数据 A0 A1 An-1 D0 D1 Db-1 D0 D1 Db-1 A0 A1 An-1 2 n×b ROM . . . . 最高位 最低位

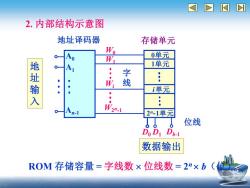

DI 2.内部结构示意图 地址译码器 存储单元 W o 0单元 1单元 地址输 W 线 i单元 n-1 W2-1 2n-1单元 位线 Do D1 D6-1 数据输出 ROM存储容量=字线数×位线数=2"×b(⑥

2. 内部结构示意图 存储单元 数据输出 字 线 位线 地址译码器 ROM 存储容量 = 字线数 位线数 = 2n b(位) 地 址 输 入 0单元 1单元 i单元 2 n-1单元 D0 D1 Db-1 A0 A1 An-1 W0 W1 Wi W2 n -1

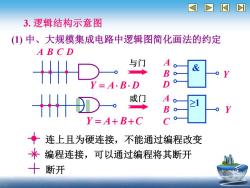

3.逻辑结构示意图 ()中、大规模集成电路中逻辑图简化画法的约定 ABCD HHD & B Q Y=4.B.D HD-。 或门 A B Y=A+B+C ★ 连上且为硬连接,不能通过编程改变 米 编程连接,可以通过编程将其断开 十断开

3. 逻辑结构示意图 (1) 中、大规模集成电路中逻辑图简化画法的约定 连上且为硬连接,不能通过编程改变 编程连接,可以通过编程将其断开 断开 Y = A B D A B C D A B D Y & Y = A+ B+C A B C Y ≥1 与门 或门

D I 缓冲器 0 4 Y=A 回方可 同相输出 反相输出 互补输出

A Y=A A Y=A Z=A Y=A A A Y 1 A 1 Y A 1 Y Z 缓冲器 同相输出 反相输出 互补输出

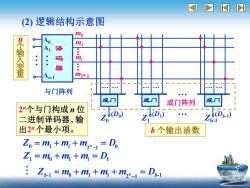

D☑I (2)逻辑结构示意图 mo m 个输入变 译 ● 码 器 'n-l t2.1 与门阵列 或门 或门阵列 2m个与门构成n位 二进制译码器,输 出2"个最小项。 b个输出函数 Z=m+m,+m2-1=D, Z1=%+m1+m=D1 :Z1=+m+m,+m2-1=D1

(2) 逻辑结构示意图 m0 A0 A1 An-1 m1 mi m2 n-1 译 码 器 Z0 (D0 ) . . 或门 Z1 (D1 ) . . 或门 Zb-1 (Db-1 ) . . 或门 . 2 . n个与门构成 n 位 二进制译码器, 输 出2 n 个最小项。 Z0 = m1 + mi + m2 n −1 = D0 Z1 = m0 + m1 + mi = D1 . . . Zb -1 = m0 + m1 + mi + m2 n −1 = Db -1 n 个 输 入 变 量 b 个输出函数 或门阵列 与门阵列

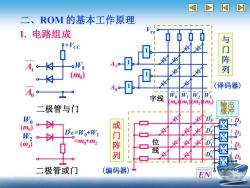

二、ROM的基本工作原理 1.电路组成 9+Vcc 与门 A,。 列 (m) (译码器) A 士 字线 % 店 o)水m1水m2Km3) 二极管与门 W ( 或 W 。以 Do=Wo+W2 =m0+m2 阵列 位 线 又 二极管或门 (编码器) EN

W0 (m0 ) W2 (m2 ) D 0=W0+W2 =m0 +m2 二、ROM 的基本工作原理 1. 电路组成 二极管或门 二极管与门 W0 (m0 ) +VCC A1 A0 A 1 1 1 A 1 0 1 Vcc EN D3 EN D2 EN D1 EN D0 D3 D2 D1 D0 W0 (m0 ) W1 (m1 ) W2 (m2 ) W3 (m3 ) 与 门 阵 列 (译码器) 或 门 阵 列 (编码器) 位 线 字线 输出 缓冲 EN

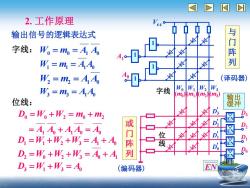

I 2.工作原理 输出信号的逻辑表达式 门 字线:W。=m=A1A 阵 Wi=m=AAo W2 =m =AA 巴 (译码器) W3=ms=AAo 字线 Wo W W2 ()m1K2)m3) 位线: D。=W+W2=m+m2 =A Ao+A4o=Ao 或门 D=W+W2+W3=4+A 阵 线 D,=Wo+W2+W3=4+4 D3=Wi+W3=Ao (编码器) EN

2. 工作原理 输出信号的逻辑表达式 W0 = m0 = A1 A0 W1 = m1 = A1 A0 W2 = m2 = A1 A0 W3 = m3 = A1 A0 1 0 1 0 0 0 0 2 0 2 A A A A A D W W m m = + = = + = + D1 =W1 +W2 +W3 = A1 + A0 D2 =W0 +W2 +W3 = A0 + A1 D3 =W1 +W3 = A0 A 1 1 1 1 A0 1 Vcc EN D3 EN D2 EN D1 EN D0 D3 D2 D1 D0 W0 (m0 ) W1 (m1 ) W2 (m2 ) W3 (m3 ) 与 门 阵 列 (译码器) 或 门 阵 列 (编码器) 位 线 输出 缓冲 EN 字线 字线: 位线:

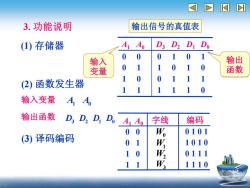

3.功能说明 输出信号的真值表 (1)存储器 A1 A0 D3 D2 D Do 输入 0 0 0 0 输出 变量 0 函数 (2)函数发生器 1 0 1 输入变量 :AA 输出函数D,D2D1D 0A1A0 字线 编码 00 0101 (3)译码编码 W 01 1010 1 0 0111 W 1110

输出信号的真值表 0 0 0 1 1 0 1 1 0 1 0 1 A1 A0 D3 D2 D1 D0 1 0 1 0 0 1 1 1 1 1 1 0 3. 功能说明 (1) 存储器 (2) 函数发生器 地址 存储 数据 输入变量 1 0 A A 输出函数 3 2 1 0 D D D D (3) 译码编码 字线 编码 W0 0 1 0 1 1 0 1 0 0 1 1 1 1 1 1 0 A1 A0 0 0 0 1 1 0 1 1 输入 变量 输出 函数 W1 W2 W3

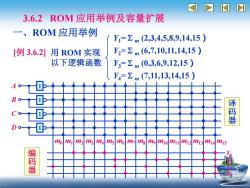

3.6.2R0M应用举例及容量扩展 一、ROM应用举例 Y1=Σm(2,3,4,5,8,9,14,15) [例3.6.2用ROM实现 Y2=∑m(6,7,10,11,14,15) 以下逻辑函数 Y3=Σm(03,6,9,12,15) Y4=2m(7,11,13,14,15) 译码器 mo m m2 m3 ma ms mo m ms my miomm12 m13 m1mis 码器

3.6.2 ROM 应用举例及容量扩展 一、ROM 应用举例 用 ROM 实现 以下逻辑函数 [例 3.6.2] Y1= m (2,3,4,5,8,9,14,15) Y2= m (6,7,10,11,14,15) Y3= m (0,3,6,9,12,15) Y4= m (7,11,13,14,15) A 1 B 1 C 1 D 1 m0 m1 m2 m3 m4 m5 m6 m7 m8 m9 m10 m11 m12 m13 m14 m15 Y2 Y3 Y4 Y1 译 码 器 编 码 器

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt