《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路

2.3 CMOS集成门电路 2.3.1CMOS反相器 一、电路组成及工作原理 +VDD UTN=2V UTP=-2V +10V WGSN WGSP TN Tr y Te UiN >Urp 导通 截止 Y-A

+VDD +10V G1 B1 D1 S1 uA uY TN TP B2 D2 S2 G2 VSS + - uGSN + u - GSP 2. 3 CMOS 集成门电路 2. 3. 1 CMOS 反相器 Y = A 一、电路组成及工作原理 A Y 1 0V +10V uA uGSN uGSP TN TP uY 0 V UTN > UTP 导通 截止 0 V UTN = 2 V UTP = - 2 V +10V RONP uY +VDD 10V TN S TP +10V RONN uY +VDD 0V S TN TP

I 二、静态特性 1.电压传输特性: =f(4) Q+VDD A B B2 D uo NH B E S →WIV U +忙山了 噪声容限:指为规定值时,允许波动的最大范围。 U江:输入为低电平时的噪声容限。 U:输入为高电平时的噪声容限。 0.3VDD

二、静态特性 1. 电压传输特性: ( ) O uI u = f iD +VDD G1 B1 D1 S1 + uI - uO TN TP B2 D2 S2 G2 VSS A B C D E F UTN VDD UTH UTP UNL UNH AB 段:uI < UTN , uO = VDD 、 iD 0, 功耗极小。 0 uO /V uI /V BC 段: uI UTN , TTN 截止、TP 导通, CD 段: uI = 0.5VDD N , 导通TN、,TuP O 均略下降。 导通。 uO i D = i D(max)。 DE、EF 段: 与 BC、AB 段对应,TN、TP 的状态与之相反。 TN : 截止导通 TP : 导通截止 转折电压 指为规定值时,允许波动的最大范围。 UNL:输入为低电平时的噪声容限。 UNH:输入为高电平时的噪声容限。 = 0.3VDD 噪声容限:

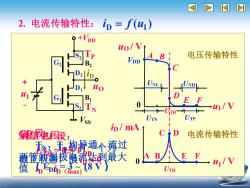

I 2.电流传输特性:iD=f(山1) +VDD uo/V JS.Tp 电压传输特性 B2 VDD D2 D uo UNHL G B TN 0 E F u/V UTN UTP ip mA 裙纯压段: 电流传输特性 万趣骨通个海过 覃雀级海极袅扰达到最大 u/V 值 6,38V) UTH

2. 电流传输特性: ( ) D uI i = f iD +VDD G1 B1 D1 S1 + uI - uO TN TP B2 D2 S2 G2 VSS A B C D E F UTN VDD UTH UTP UNL UNH 0 uO / V uI / V A B C D E F 0 iD / mA uI / V UTH 电压传输特性 AB、EF 段: 电流传输特性 TN、TP总有一个为 截止状态,故 iD 0 。 CD 段: TN、Tp 均导通,流过 两管的漏极电流达到最大 值 iD = iD(max) 。 阈值电压: UTH = 0.5 VDD (VDD = 3 ~ 18 V)

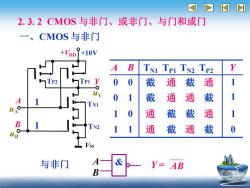

I 2.3.2CM0S与非门、或非门、与门和或门 一、CMOS与非门 +VpD +10V A B TNI TPI TN2 TPZ D 0 截通 截 通 截通 通 截 通截截 通 B 通 截通 截 B 与非门 A & Y=AB B

2. 3. 2 CMOS 与非门、或非门、与门和或门 A B TN1 TP1 TN2 TP2 Y 0 0 0 1 1 0 1 1 截 通 截 通 通 通 通 截 截 通 截 截 截 截 通 通 1 1 1 0 与非门 一、CMOS 与非门 uA +VDD +10V VSS TP1 TN1 TP2 TN2 A B Y uB uY A B & 0 0 1 1 Y = AB

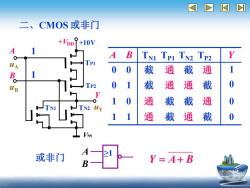

二、CMOS或非门 +on9+10V A B TNI TPI TN2 TP2 0 截通截通 1 B WB TP2 0 截通通 截 0 通截截 通 TNI TN2 通 截通 截 0 或非门 Y=A+B

或非门 Y = A+ B 二、CMOS 或非门 uA +VDD +10V VSS TP1 TN1 TN2 TP2 A B Y uB uY A B TN1 TP1 TN2 TP2 Y 0 0 0 1 1 0 1 1 截 通 截 通 通 通 通 截 截 通 截 截 截 截 通 通 1 0 0 0 A B ≥1 0 0 1 1

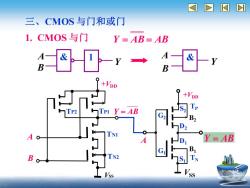

I 三、CMOS与门和或门 1.CMOS与门 Y=AB=AB A一 +VpD +VpD Tp HTPI Y=AB G2 B2 D ● D Y=AB G B SS

三、CMOS 与门和或门 1. CMOS 与门 A B & Y 1 Y = AB = AB +VDD VSS TP1 TN1 TP2 TN2 A B Y A B Y & = AB +VDD G B1 1 D1 S1 A TN TP B2 D2 S2 G2 VSS Y==AAB

☒D☒I 2.CMOS或门 Y=A+B=A+B -一 +VDD TPI Tp G2 B2 B D2 D Y=A+B TNI HTN2 Y=A+B B ⊥Vs

2. CMOS 或门 Y 1 Y = A+ B = A+ B = A+ B +VDD G B1 1 D1 S1 A TN TP B2 D2 S2 G2 VSS Y = A A B ≥1 A B Y ≥1 +VDD VSS TP1 TN1 TN2 TP2 A B Y Y = A+ B

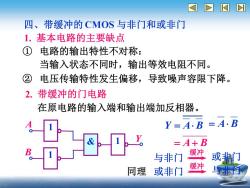

I 四、带缓冲的CMOS与非门和或非门 1.基本电路的主要缺点 ① 电路的输出特性不对称: 当输入状态不同时,输出等效电阻不同。 ② 电压传输特性发生偏移,导致噪声容限下降。 2.带缓冲的门电路 在原电路的输入端和输出端加反相器。 Y=4.B =A·B =4+B 与非门 缓冲 或门 同理 或非门 缓冲 与非9

四、带缓冲的 CMOS 与非门和或非门 1. 基本电路的主要缺点 ① 电路的输出特性不对称: 当输入状态不同时,输出等效电阻不同。 ② 电压传输特性发生偏移,导致噪声容限下降。 2. 带缓冲的门电路 在原电路的输入端和输出端加反相器。 A 1 B Y Y = A B = A B = A+ B 与非门 或非门 同理 缓冲 或非门 与非门 缓冲 & 1 1

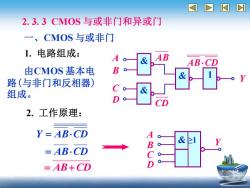

2.3.3CM0S与或非门和异或门 一、CMOS与或非门 1.电路组成: & AB AB.CD 由CMOS基本电 B & 路(与非门和反相器) 组成。 CD 2.工作原理: Y=AB.CD =AB.CD =AB+CD

2. 3. 3 CMOS 与或非门和异或门 一、CMOS 与或非门 1. 电路组成: & & & A B C D & ≥1 Y A B C D Y 1 2. 工作原理: Y = ABCD = ABCD = AB+CD ABCD ABCD 由CMOS 基本电 路(与非门和反相器) 组成

I 二、CMOS异或门 1.电路组成: A·AB 由CMOS基本电 路(与非门)组成。 2.工作原理: AB:B Y=A·AB.AB·B =A·AB+AB·B 一 =AB+AB=A⊕B

二、CMOS 异或门 1. 电路组成: & & A & B Y 2. 工作原理: Y = A AB AB B = A AB + AB B = A B AB A AB & AB B = A B + A B Y AB =1 由CMOS 基本电 路 (与非门 )组成

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程试卷习题(自我检测)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt