《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器

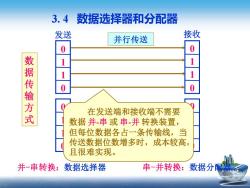

3.4数据选择器和分配器 发送 并行传送 接收 0 数据传输方式 0110 11 0 在发送端和接收端不需要 数据并串或串并转换装置, 但每位数据各占一条传输线,当 传送数据位数增多时,成本较高, 且很难实现。 并-串转换:数据选择器 串-并转换:数据分宿

数 据 传 输 方 式 0 1 1 0 发送 0 1 1 0 并行传送 0 1 1 0 串行传送 并-串转换:数据选择器 串-并转换:数据分配器 3. 4 数据选择器和分配器 接收 0 1 1 0 在发送端和接收端不需要 数据 并-串 或 串-并 转换装置, 但每位数据各占一条传输线,当 传送数据位数增多时,成本较高, 且很难实现

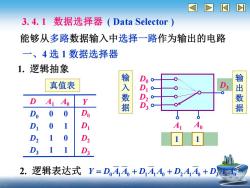

D 3.4.1数据选择器(Data Selector) 能够从多路数据输入中选择一路作为输出的电路 一、4选1数据选择器 1.逻辑抽象 真值表 D A1 A0 输入数据 0 D3 输出数据 Do 0 0 Do Di 0 1 D 0 D2 0 D2 D; D, 2. 逻辑表达式Y=D,AA+DA1A+D2AA,+D

3. 4. 1 数据选择器 ( Data Selector ) 能够从多路数据输入中选择一路作为输出的电路 一、4 选 1 数据选择器 输 入 数 据 输 出 数 据 选择控制信号 A0 4选1 Y 数据选择器 D0 D3 D1 D2 A1 1. 逻辑抽象 0 10 1 D0123 D0 0 0 D0 D A1 A0 真值表 D1 0 1 D2 1 0 D3 1 1 Y D1 D2 D3 2. 逻辑表达式 Y = D0 A1 A0 + D1 A1 A0 + D2 A1 A0 + D3 A1 A0

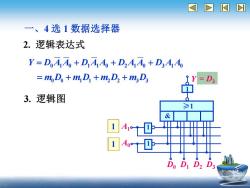

一、4选1数据选择器 2.逻辑表达式 Y=Do44o+D:44o+D2A4o+D3 4 4o =moDo+mD+m2D2 ms Ds 3.逻辑图 ≥1 & 14T 1 401 Do D D2 D3

一、4 选 1 数据选择器 2. 逻辑表达式 Y = D0 A1 A0 + D1 A1 A0 + D2 A1 A0 + D3 A1 A0 3. 逻辑图 = m0 D0 + m1 D1 + m2 D2 + m3 D3 1 & ≥1 1 Y A1 A0 1 D0 D1 D2 D3 0 0 1 1 = D0123

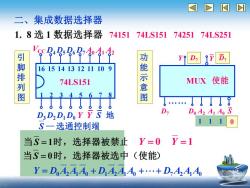

二、集成数据选择器 1.8选1数据选择器 7415174LS1517425174LS251 引 ccD4D5D6D1404142 D 161514131211109 排列图 74LS151 1234 56 78 示意图 MUX使能 。 D3D2D1DYTS地 DoA2 A1 Ao S 111 S一选通控制端 0 当S=1时,选择器被禁止 Y=0 Y=1 当S=0时,选择器被选中(使能) Y=D4A40+D 444o++D42440

╳ ╳ ╳ 二、集成数据选择器 1. 8 选 1 数据选择器 74151 74LS151 74251 74LS251 引 脚 排 列 图 功 能 示 意 图 S — 选通控制端 VCC 地 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 74LS151 D4 D5 D6 D7 A0 A1 A2 D3 D2 D1 D0 Y Y S MUX D7 D0 A2 A1 A0 S Y Y . 使能禁止 0 1 0 0 0 D01234567 D01234567 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 01 A2 A0 — 地址端 D7 D0 — 数据输入端 Y 、 Y — 数据输出端 Y = 0 Y = 1 Y D0 A2 A1 A0 D1 A2 A1 A0 + D7 A2 A1 A0 = + + 当S = 1时,选择器被禁止 当S = 0时,选择器被选中(使能 )

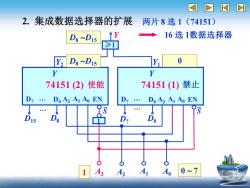

☒D☒I 2.集成数据选择器的扩展 两片8选1(74151) Ds ~DIs 16选1数据选择器 Y2 Ds ~D15 0 Y Y 74151(2)使能 74151(1)禁止 D2. DoA2 A1 Ao EN D2. DoA2 A1 Ao EN D15 Ds D D 0~7

2. 集成数据选择器的扩展 两片 8 选 1(74151) 16 选 1数据选择器 A3 A2 A1 A0 D15 D8 ≥1 Y 1 S 74151 (2) D7 D0 A2 A1 A0 EN Y Y2 . . D7 D0 74151 (1) D7 D0 A2 A1 A0 EN S Y Y1 . . 高位 低位 0 禁止 使能 0 7 0 D0 D7 D0 D7 1 使能 禁止 D8 D15 0 D8 D15

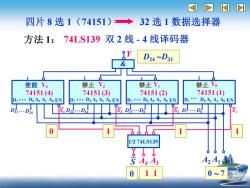

>K I 四片8选1(74151)◆32选1数据选择器 方法1:74LS139双2线-4线译码器 D24~D31 1 使能Y 禁止Y 禁止Y 禁止Yo 74151(4 74151(3) 74151(2) 74151(1) D2·D0A2AAEN D·D6A2A1AEN D2·D6A2AA0EN D. DoA2 AI Ao EN D1.D24 4D2.D1 D.Ds 2D.D 1/274LS139 A2A 0~7

0 四片 8 选 1(74151) 32 选 1 数据选择器 1/2 74LS139 S A4 A3 A2 A1 A0 & Y 方法 1: 74LS139 双 2 线 - 4 线译码器 74151 (4) D7 D0 A2 A1 A0 EN S4 Y3 74151 (1) D7 D0 A2 A1 A0 EN D0 S1 Y0 74151 (2) D7 D0 A2 A1 A0 EN S2 Y1 74151 (3) D7 D0 A2 A1 A0 EN S3 Y2 . . . . D31.D24 D23.D16 D15.D8 D7 . 1 1 1 1 1 0 7 禁止 禁止 禁止 禁止 0 0 0 1 1 1 0 禁止 禁止 禁止 使能 0 1 使能 使能禁止 禁止使能 禁止 1 0 1 1 D168024D157231 10 10 01 1

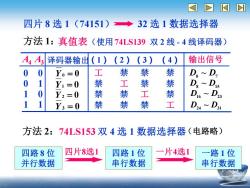

四片8选1(74151)◆32选1数据选择器 方法1:真值表(使用74LS139 双2线-4线译码器) A A3 译码器输出 (1) (2)(3) (4) 输出信号 0 0 Yo=0 工 禁 林 丙 禁 ~D, 0 Y1=0 禁 工 然 禁 Ds 0 Y2 =0 禁 工 D6~D3 Y3=0 禁 禁 林 工 D~Ds 方法2: 74LS153双4选1数据选择器(电路略) 四路8位 四片8选1 四路1位 片4选1 一路1位 并行数据 串行数据 串行数据

方法 2:74LS153 双 4 选 1 数据选择器 A4 A3 (1) (2) (3) (4) 输出信号 0 0 工 禁 禁 禁 D0 ~ D7 0 1 禁 工 禁 禁 D8 ~ D15 1 0 禁 禁 工 禁 D16 ~ D23 1 1 禁 禁 禁 工 D24 ~ D31 译码器输出 Y 0 = 0 Y1 = 0 Y 2 = 0 Y 3 = 0 方法 1: 四片 8 选 1(74151) 32 选 1 数据选择器 四路 8 位 并行数据 四片8选1 四路 1 位 串行数据 一片4选1 一路 1 位 串行数据 (电路略) 真值表(使用74LS139 双 2 线 - 4 线译码器)

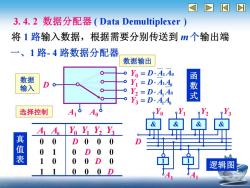

3.4.2数据分配器(Data Demultiplexer) 将1路输入数据,根据需要分别传送到m个输出端 一、1路-4路数据分配器 数据输出 Yo=D.A1A0 数据 Y=D.A1Ao 输入 Y2=D.A Ao Y3=D.AAo 式 选择控制 A A0 Yo YI Y Y3 真 0 0 D 00 0 0 0 0 表 0 0 D 0 逻辑图 0 0 0 D

3. 4. 2 数据分配器 ( Data Demultiplexer ) 将 1 路输入数据,根据需要分别传送到 m 个输出端 一、1 路- 4 路数据分配器 数据 输入 数据输出 选择控制 0 0 0 1 1 0 1 1 A1 A0 0 1 2 3 Y Y Y Y D 0 0 0 0 D 0 0 0 0 D 0 0 0 0 D = D A1A0 0 = D A1A 0 = D A1 A D A1 A0 = & Y0 & Y1 & Y2 & Y3 1 A1 1 A1 D D A0 1 路-4 路 数据分配器 Y0 Y3 Y1 Y2 A1 真 值 表 函 数 式 逻辑图

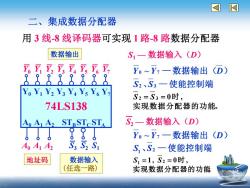

二、集成数据分配器 用3线-8线译码器可实现1路-8路数据分配器 数据输出 S1一数据输入(D) I可可4Z。 7。~7,一数据输出 (D) &888888 8 S2、S一使能控制端 Yo YI Y2 Y3 Y4 Y5 Y6Y7 S2=S3=0时, 74LS138 实现数据分配器的功能。 Ao A1 A2 STBSTCSTA S,一 数据输入(D) Y。~Y,一数据输出(D) A0 A1 42 S3 S2 S1 S,、S,一使能控制端 地址码 数据输入 S1=1,S2=0时, (任选一路) 实现数据分配器的功能

二、集成数据分配器 用 3 线-8 线译码器可实现 1 路-8 路数据分配器 数据输出 S1 — 数据输入(D) S2 、S3 — 使能控制端 Y0 ~ Y7 — 数据输出(D) 地址码 数据输入 (任选一路) 实现数据分配器的功能。 S2 = S3 = 0时 , S2 — 数据输入(D) Y0 ~ Y7 — 数据输出(D) 2 S1 、S — 使能控制端 实现数据分配器的功能。 1 , 2 0时 , S1 = S = 74LS138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB STC STA Y7

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt