《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法

5.1时序电路的基本分析和设计方法 5.1.1时序电路的基本分析方法 一、分析的一般步骤 时序电路 驱动方程 时钟方程 输出方程 特性方 状态方程 计算 CP 状态表 状态图 时序图 触发沿

5.1 时序电路的基本分析和设计方法 5.1.1 时序电路的基本分析方法 一、 分析的一般步骤 时序电路 时钟方程 驱动方程 状态表 状态图 时序图 CP 触 发 沿 特 性 方 程 输出方程 状态方程 计算

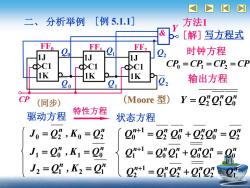

二、分析举例[例5.1.1] 方法1 [解]写方程式 FFo FF 02 时钟方程 >C1 >C1 CP=CP=CP =CP 1K 1K 输出方程 CP (同步) (Moore型) Y=222"2 驱动方程 特性方程 状态方程 J0=Q2,K0=22 2+1=05+0226=02 J1=26,K1=26 0+1=g601+0621”=99 J2=2,K2=2” 02+1=21"25+21"2

二、 分析举例 写方程式 时钟方程 CP0 = CP1 = CP2 = CP 输出方程 n n n (同步) Y = Q2 Q1 Q0 驱动方程 n n J0 = Q2 , K0 = Q2 n n J1 = Q0 , K1 = Q0 n n J2 = Q1 , K2 = Q1 状态方程 特性方程 n n n n n n Q Q2 Q0 Q2 Q0 Q2 1 0 = + = + n n n n n n Q Q0 Q1 Q0 Q1 Q0 1 1 = + = + n n n n n n Q Q1 Q2 Q1 Q2 Q1 1 2 = + = + (Moore 型) [例 5.1.1] [解] 1J 1K C1 Q0 Q0 1J 1K C1 1J 1K C1 Q1 Q2 Q1 Q2 & FF0 FF1 FF2 CP Y 方法1

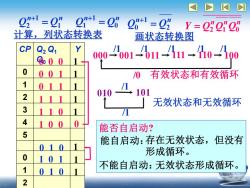

2+1=2121=262+1=5 计算,列状态转换表 画状态转换图 CP Q2 Q 0004001-4011-111→40-100 o0 0有效状态和有效循环 010 101 无效状态和无效循环 3 1 4 能否自启动? 5 能自启动:存在无效状态,但没有 形成循环。 0 1 不能自启动:无效状态形成循环。 01 2

n n Q Q2 1 0 = Q n Q n + 0 1 1 = n n + Q Q1 1 2 = + n n n Y = Q2 Q1 Q0 计算,列状态转换表 CP Q2 Q1 Q0 Y 0 1 2 3 4 5 0 1 2 0 0 0 1 0 0 1 1 0 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 0 1 0 1 1 0 1 1 0 1 0 1 画状态转换图 000 001 /1 011 /1 111 /1 110 /1 100 /1 /0 有效状态和有效循环 010 101 /1 /1 无效状态和无效循环 能否自启动? 能自启动:存在无效状态,但没有 形成循环。 不能自启动:无效状态形成循环

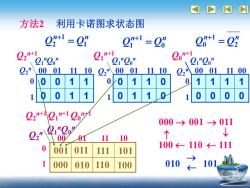

I 方法2 利用卡诺图求状态图 22+'=21州 21+1=2 2+1=25 o 212" 2"2" 20 21"2" 22"\0001 1110 22m0001 1110 220001 1100 0小0 0 00 1 0 1 1 0 0 1 1 0 0 0 02+121+12o 000→001→011 ↓ 00 11 10 个 100←110←111 001 011 111 101 000 010 110 100 010 101

方法2 利用卡诺图求状态图 n n Q Q2 1 0 = n n + Q Q0 1 1 = Q n Q n + 1 1 2 = + 0 0 1 1 0 0 1 1 Q2 n+1 Q2 n Q1 nQ0 n 0 1 00 01 11 10 0 1 1 0 0 1 1 0 Q1 n+1 Q2 n Q1 nQ0 n 0 1 00 01 11 10 0 0 0 0 1 1 1 1 Q0 n+1 Q2 n Q1 nQ0 n 0 1 00 01 11 00 Q2 n+1 Q1 n+1 Q0 n+1 Q1 nQ0 n Q2 n 0 1 00 01 11 10 001 011 111 101 000 010 110 100 000 → 001 → 011 111 → 110 → 100 → 010 → →101 →

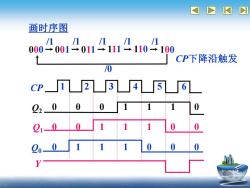

画时序图 /1 /1/1/1/1 000→001→011→111→110→100 CP下降沿触发 /0 cP1234 6 22

画时序图 000 001 /1 011 /1 111 /1 110 /1 100 /1 /0 CP 1 2 3 4 5 6 CP下降沿触发 Q2 Q1 Q0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 0 1 0 0 0 0 0 Y

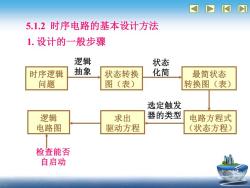

5.1.2时序电路的基本设计方法 1.设计的一般步骤 逻辑 状态 时序逻辑 抽象 状态转换 化简 最简状态 问题 图(表) 转换图(表) 选定触发 逻辑 求出 器的类型 电路方程式 电路图 驱动方程 (状态方程) 检查能否 自启动

5.1.2 时序电路的基本设计方法 1. 设计的一般步骤 时序逻辑 问题 逻辑 抽象 状态转换 图(表) 状态 化简 最简状态 转换图(表) 电路方程式 (状态方程) 求出 驱动方程 选定触发 逻辑 器的类型 电路图 检查能否 自启动

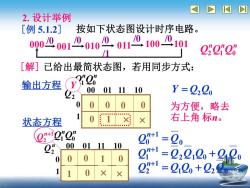

DI 2.设计举例 [例5.1.2] 按如下状态图设计时序电路。 00401心010901巴100少101 1 22"2 [解]已给出最简状态图,若用同步方式: 输出方程 12 00 01 11 10 Y=2220 0 0 0 0 为方便,略去 状态方程 0 右上角标n。 4 asssak■nn g2+p" 00 01 2'=2o 10 0 0 2+1=2222+940 22+1=22+22

2. 设计举例 按如下状态图设计时序电路。 000 /0 /0 /0 /0 /0 001 010 011 100 101 /1 n n n Q2 Q1 Q0 [解] 已给出最简状态图,若用同步方式: 输出方程 00 01 11 10 0 1 n Q2 n n Q1 Q0 Y 0 0 0 0 0 1 Y = Q2 Q0 为方便,略去 右上角 标n。 状态方程 00 01 11 10 0 1 n Q2 n n Q1 Q0 1 0 n+ Q 1 0 0 1 1 0 0 1 Q0 Q n = 1 + 1 n+ Q 0 1 0 2 1 0 1 0 1 Q1 Q Q Q Q Q n = + + 1 2 n+ Q 0 1 0 1 1 0 2 0 1 Q2 Q Q Q Q n = + + [例 5.1.2]

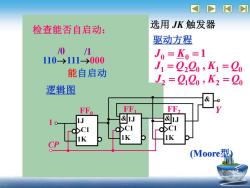

I 检查能否自启动: 选用JK触发器 驱动方程 /0 1 110→111→>000 J0=K0=1 能自启动 J1=0200,K1=20 J2=220,K2=00 逻辑图 FFo CP (Moore型)

0 1 Q0 Q n = + 2 1 0 1 0 1 Q1 Q Q Q Q Q n = + + 1 0 2 0 1 Q2 Q Q Q Q n = + + 选用 JK 触发器 J0 = K0 = 1 1 2 0 1 0 J = Q Q , K = Q 驱动方程 约束项 1 0 2 2 2 0 = Q Q (Q +Q )+Q Q Q1 Q0 Q2 Q1 Q0 Q2 Q2 Q0 = + + Q1 Q0 Q2 Q2 Q0 = + 逻辑图 CP 1K C1 FF1 & 1J Y 1J 1K C1 FF0 1K C1 FF2 & 1J 1 & 检查能否自启动: 110→111→000 能自启动 /0 /1 2 1 0 K2 Q0 J = Q Q , = (Moore型)

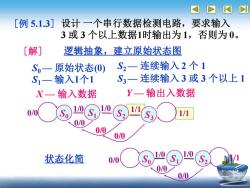

网网I [例5.1.3] 设计一个串行数据检测电路,要求输入 3或3个以上数据1时输出为1,否则为0。 [解] 逻辑抽象,建立原始状态图 S,一原始状态(O) S2一连续输入2个1 S1一输入1个1 S3一连续输入3或3个以上1 X一输入数据 Y一输出入数据 0/0 1/0 /0 1/1 0/0 0/0 0/0 状态化简 0/0 0/0

1/1 [例 5.1.3] 设计 一个串行数据检测电路,要求输入 3 或 3 个以上数据1时输出为 1,否则为 0。 [解] 逻辑抽象,建立原始状态图 S0 — 原始状态(0) S1 — 输入1个1 S2 — 连续输入 2 个 1 S3 — 连续输入 3 或 3 个以上 1 S0 S1 S2 S3 X — 输入数据 Y — 输出入数据 0/0 1/0 0/0 1/0 0/0 0/0 1/1 状态化简 0/0 S0 S1 S2 1/0 0/0 1/0 0/0 1/1 0/0 0/0

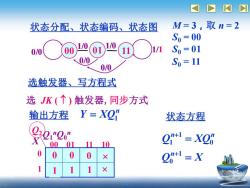

状态分配、状态编码、状态图 M=3,取n=2 S,=00 S=01 0/0 0/0 Sw=11 选触发器、写方程式 选JK(个)触发器,同步方式 输出方程 Y=XQ” 状态方程 0001 10 211=XQ 201=X

状态分配、状态编码、状态图 0/0 S0 S1 S2 1/0 0/0 1/0 0/0 1/1 M = 3,取 n = 2 S0 = 00 S0 = 01 S0 = 11 0/0 00 01 11 1/0 0/0 1/0 0/0 1/1 选触发器、写方程式 选 JK ( ) 触发器,同步方式 输出方程 Q1 nQ0 n X 0 1 00 01 11 10 Y 0 0 0 0 0 1 n Y = XQ1 Q1 1 n n Q XQ0 1 1 = 2 + 1 Q X n = +1 0 状态方程

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH63 多谐振荡器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 SUM6 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH70 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH71 D/A转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH72 A/D转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 SUM7 小结.ppt

- 西安邮电大学:《现代通信网》课程教学大纲 Modern Communication Network C.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第一章 绪论.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第二章 传送网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第三章 数据链路层.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第五章 同步网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第六章 电话网.doc