《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器

5.2计数器(Counter) 5.2.1计数器的特点和分类 一、计数器的功能及应用 1.功能:对时钟脉冲CP计数。 2.应用:分频、定时、产生节拍脉冲和脉冲 序列、进行数字运算等。 二、计数器的特点 1.输入信号: 计数脉冲CP Moore型 2.主要组成单元:时钟触发器

5.2 计数器 (Counter) 5.2.1 计数器的特点和分类 一、计数器的功能及应用 1. 功能: 对时钟脉冲 CP 计数。 2. 应用: 分频、定时、产生节拍脉冲和脉冲 序列、进行数字运算等。 二、计数器的特点 1. 输入信号: 计数脉冲 CP Moore 型 2. 主要组成单元: 时钟触发器

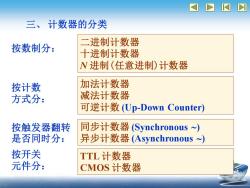

三、计数器的分类 按数制分: 二进制计数器 十进制计数器 N进制(任意进制)计数器 按计数 加法计数器 方式分: 减法计数器 可逆计数(Up-Down Counter) 按触发器翻转 同步计数器(Synchronous~) 是否同时分: 异步计数器(Asynchronous~) 按开关 TTL计数器 元件分: CMOS计数器

三、 计数器的分类 按数制分: 二进制计数器 十进制计数器 N 进制(任意进制)计数器 按计数 方式分: 加法计数器 减法计数器 可逆计数 (Up-Down Counter) 按触发器翻转 是否同时分: 同步计数器 (Synchronous ) 异步计数器 (Asynchronous ) 按开关 元件分: TTL 计数器 CMOS 计数器

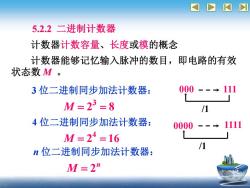

5.2.2二进制计数器 计数器计数容量、长度或模的概念 计数器能够记忆输入脉冲的数目,即电路的有效 状态数M。 3位二进制同步加法计数器: 000-→111 M=23=8 /1 4位二进制同步加法计数器: 0000-→1111 M=24=16 /1 n位二进制同步加法计数器: M=2

5.2.2 二进制计数器 计数器计数容量、长度或模的概念 计数器能够记忆输入脉冲的数目,即电路的有效 状态数 M 。 3 位二进制同步加法计数器: 2 8 3 M = = 0000 1111 /1 4 位二进制同步加法计数器: 000 111 /1 2 16 4 M = = n 位二进制同步加法计数器: n M = 2

☒冈I 一、二进制同步计数器 1.3位二进制同步加法计数器 ()结构示意框图与状态图 CP 三位二进制同步 Carry 输入计数脉冲 加法计数器 送给高位的进位信号 000-901001040119100910191091 /1

一、二进制同步计数器 1. 3位二进制同步加法计数器 (1) 结构示意框图与状态图 三位二进制同步 加法计数器 CP Carry 输入计数脉冲 送给高位的进位信号 000 001 /0 010 /0 011 /0 100 /0 101 /0 110 /0 111 /0 /1

2)分析和选择触发器 FF2、FF1、FFo 22、21、20 设计方法一:按前述设计步骤进行(P297~299) 设计方法二: 按计m生业行级联 来一个CP Q2Q1Qo CP 当Q=1,CP 22"1"2" 0 当220=1,CP 到来即翻转 =1=T0 123456 0 J1=K1=20=T1 0 00 J2=K2=2120=T2 7 8

FF2、FF1、FF0 Q2、Q1、Q0 设计方法一:按前述设计步骤进行 (P297 299) 设计方法二:按计数规律进行级联 CP Q2Q1Q0 C 0 1 2 3 4 5 6 7 8 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 0 0 0 0 0 0 0 1 0 C = Q2 n Q1 n Q0 n 来一个CP 翻转一次 J0= K0 = 1 当Q0=1,CP 到来即翻转 J1= K1 = Q0 当Q1Q0=1,CP 到来即翻转 J2= K2 = Q1Q0 = T0 = T1 = T2 (2) 分析和选择触发器

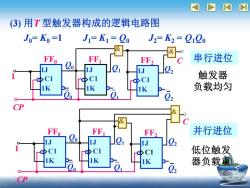

冈I 3)用T型触发器构成的逻辑电路图 J0=K0=1 J1=K1=20 J2=K2=2120 FF FF2 串行进位 触发器 负载均匀 D FF FF 并行进位 低位触发 器负载重 D

J0= K0 =1 J1= K1 = Q0 J2= K2 = Q1Q0 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & & C Q0 Q1 Q2 Q0 Q1 Q2 串行进位 触发器 负载均匀 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & & C Q0 Q1 Q2 Q0 Q1 Q2 并行进位 低位触发 器负载重 (3) 用T 型触发器构成的逻辑电路图

(④)用T型触发器构成的逻辑电路图 22 CP (⑤)n位二进制同步加法计数器级联规律: T=g%02.g0-1 i=0

(5) n 位二进制同步加法计数器级联规律: -1 0 1 2 1 0 = = − − = i j n j n n n i n Ti Qi Q Q Q Q (4) 用T ’型触发器构成的逻辑电路图 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & C Q0 Q1 Q2 Q0 Q1 Q2 1 & 1 &

>K H 2.3位二进制同步减法计数器 C Q2Q1Qo B FF2、FF1、FFo 22、21、20 0 0 0 0 1 级联规律: 1 1 1 1 0 1 1 0 0 7=0%0200-1g 3 1 0 1 0 1 0 0 T0=1 T=2o" T2=21"夏" 5 0 1 1 0 67 0 1 0 0 0 0 1 0 FF FF CP ●

B = Q2 n Q1 n Q0 n Borrow 若用T 触发器: 2. 3 位二进制同步减法计数器 C P Q2Q1Q0 B 0 1 2 3 4 5 6 7 0 0 0 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 1 0 0 0 0 0 0 0 FF2 、FF1 、FF0 Q2 、Q1 、Q0 — 向高位发出的借位信号 T0 = 1 T1=Q0 n T2= Q1 n Q0 n 级联规律: -1 0 1 2 1 0 = = − − = i j n j n n n i n Ti Qi Q Q Q Q CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF1 & & B Q0 Q1 Q2 Q0 Q1 Q2

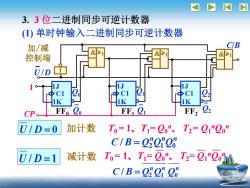

3.3位二进制同步可逆计数器 ()单时钟输入二进制同步可逆计数器 加/减 & 控制端 UID 1J 1 1K FFo Co FF FF2 U/D=0 加计数 T0=1、T1=2om、T2=21"2” C1B=221"26 U/D=1 减计数 To=1、T1=2"、T2=21"2 C/B=25212

3. 3 位二进制同步可逆计数器 (1) 单时钟输入二进制同步可逆计数器 加/减 控制端 U / D = 0 加计数 T0 = 1、T1= Q0 n 、T2= Q1 nQ0 n / 2 1 0 n n n C B = Q Q Q U / D = 1 减计数 T0 = 1、T1= Q0 n 、T2= Q1 nQ0 n n n n C B Q2 Q1 Q0 / = CP Q0 1J 1K C1 FF0 1 Q0 Q2 1J 1K C1 FF2 Q2 Q1 1J 1K C1 FF1 Q1 U /D 1 & 1 & 1 & 1 C/B

(2)双时钟输入二进制同步可逆计数器 FFo FF 加计数脉冲 CPU 减计数脉冲 CPD CPo=CPU+CPD CPu和CPD互相排斥 CP=CPu2"+CPD·2" CPU=CP,CPD=0 CP2=CPu·21"2o+CPD·21"Qn CPD=CP,CPL

(2) 双时钟输入二进制同步可逆计数器 加计数脉冲 减计数脉冲 CP0= CPU+ CPD CP1= CPU ·Q0 n + CPD · Q0 n CP2=CPU · Q1 n Q0 n+ CPD · Q1 n Q0 n CPU 和CPD 互相排斥 CPU= CP,CPD= 0 CPD= CP,CPU= 0 CPU Q0 1J 1K C1 1 FF0 Q0 Q2 1J 1K C1 1 FF2 Q2 Q1 1J 1K C1 1 FF1 Q1 1 & 1 & 1 CPD

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH63 多谐振荡器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 SUM6 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH70 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH71 D/A转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH72 A/D转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 SUM7 小结.ppt

- 西安邮电大学:《现代通信网》课程教学大纲 Modern Communication Network C.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第一章 绪论.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第二章 传送网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第三章 数据链路层.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第五章 同步网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第六章 电话网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第四章 No.7信令网.doc