《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器

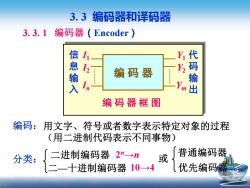

3.3编码器和译码器 3.3.1编码器 Encoder) 息输 编码器 In 代码输出 编码器框图 编码:用文字、符号或者数字表示特定对象的过程 (用二进制代码表示不同事物) 普通编码器 分类: 二进制编码器2"→n 或 二一十进制编码器10→4 优先编码器

3. 3 编码器和译码器 3. 3. 1 编码器(Encoder) 编码:用文字、符号或者数字表示特定对象的过程 (用二进制代码表示不同事物) 二进制编码器 二—十进制编码器 分类: 普通编码器 优先编码器 2 n→n 10→4 或 Y1 I1 编 码 器 Y2 Ym I2 In 代 码 输 出 信 息 输 入 编 码 器 框 图

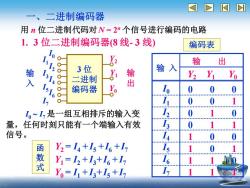

I 一、二进制编码器 用n位二进制代码对N=2"个信号进行编码的电路 1.3位二进制编码器(8线-3线) 编码表 10 2 输 出 输 3位 输 输入 Y2 YI Yo 11 二进制 出 编码器 Yo 0 0 0 0 0 1,~I,是一组互相排斥的输入变 0 0 量,任何时刻只能有一个端输入有效 0 HEAENEENBAASAAAMANASAAAANNNNANNNAANS8 信号。 0 Y2=I4+I5+L6+7 15 数式 Y1=2+3+I6+ 6 Y=I1+3+I5+I7

一、二进制编码器 用 n 位二进制代码对N = 2n 个信号进行编码的电路 1. 3 位二进制编码器(8 线- 3 线) 编码表 函 数 式 Y2 = I4 + I5 + I6 + I7 Y1 = I2 + I3+ I6 + I7 Y0 = I1 + I3+ I5 + I7 输 入 输 出 I0 I7 是一组互相排斥的输入变 量,任何时刻只能有一个端输入有效 信号。 输 入 输 出 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Y2 Y1 Y0 I0 I1 I2 I3 I4 I5 I6 I7 3 位 二进制 编码器 I0 I1 I6 I7 Y2 Y1 Y0 I2 I4 I5 I3

DI 函数式 y2=14+13+16+12=4131.1 y=I2+L3+16+17=23161 Y=I1+13+s+12=1·13·13·I7 逻辑图 一用或门实现 一用与非门实现 & & & I-Io Is Ia

函数式 逻辑图 — 用或门实现 — 用与非门实现 2 4 5 6 7 Y = I + I + I + I 1 2 3 6 7 Y = I + I + I + I 0 1 3 5 7 Y = I + I + I + I 4 5 6 7 = I I I I 2 3 6 7 = I I I I 1 3 5 7 = I I I I Y0 Y1 Y2 ≥1 ≥1 ≥1 I7 I6 I5 I4 I3 I2 I1 I0 & & & Y0 Y1 Y2 7 6 5 4 I I I I 3 2 I I 1 0 I I

>K 2.3位二进制优先编码器 优先编码:允许几个信号同时输入,但只对优先级别最高 的进行编码。优先顺序:→0 编码表 函数式 输 入 输 出 1l615432l0 Y2 Y1 Y=I+I6+Is+I 1 y=12+16+I5143 0 1 +1514l2 0 0 Y=12+16l3+16143 0 0 +161412l 0 0

优先编码:允许几个信号同时输入,但只对优先级别最高 的进行编码。优先顺序:I7 → I0 编码表 输 入 输 出 I7 I6 I5 I4 I3 I2 I1 I0 Y2 Y1 Y0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 1 0 0 0 1 1 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 1 0 1 函数式 2. 3 位二进制优先编码器 2 7 6 5 4 Y = I + I + I + I 2 5 4 3 5 4 1 7 6 I I I Y I I I I I + = + + 1 6 4 2 3 6 4 5 6 0 7 I I I I Y I I I I I I + = + +

D冈I 逻辑图 Y & 输入 输出 为反 变 3 121

输入 输出 为原 变量逻辑图 输入 输出 为反 变量 Y2 Y1 Y0 ≥ 1 ≥ 1 ≥ 1 & & 1 1 1 1 1 1 1 1 1 1 1 1 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 I 1 1 1 Y2 Y1 Y0 I7 I6 I5 I4 I3 I2 I1 I0

I 二、二-十进制编码器 用4位二进制代码对0~9十个信号进行编码的电路。 1.8421BCD编码器 2.8421BCD优先编码器 3.集成10线-4线优先编码器 二十进制 (74147 74LS147) 三、几种常用编码 161 编码器 Y2 oY3 1.二十进制编码 8421码余3码 2421码 5211码余3循环码右移循环码 2.其他 循环码(反射码或格雷码) ISO码 ANSCⅢ(ASC)码

用 4 位二进制代码对 0 ~ 9 十个信号进行编码的电路。 1. 8421 BCD 编码器 2. 8421 BCD 优先编码器 3. 集成 10线 -4线优先编码器 (74147 74LS147) 三、几种常用编码 1. 二-十进制编码 8421 码 余 3 码 2421 码 5211 码 余 3 循环码 右移循环码 循环码(反射码或格雷码) ISO码 ANSCII(ASCII)码 二、二-十进制编码器 2. 其他 二-十进制 编码器 I0 I2 I4 I6 I8 I1 I3 I5 I7 I9 Y0 Y1 Y2 Y3

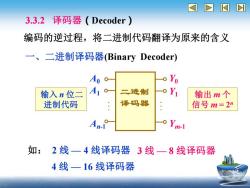

3.3.2译码器(Decoder) 编码的逆过程,将二进制代码翻译为原来的含义 一、二进制译码器(Binary Decoder) oYo 输入n位二 二进制 输出m个 进制代码 译码器 信号m=2” A Ym-i 如:2线一4线译码器3线一8线译码器 4线一16线译码器

3.3.2 译码器(Decoder) 编码的逆过程,将二进制代码翻译为原来的含义 一、二进制译码器(Binary Decoder) 输入 n 位二 进制代码 如: 2 线 — 4 线译码器 3 线 — 8 线译码器 4 线 — 16 线译码器 A0 Y0 A1 An-1 Y1 Ym-1 二进制 . 译码器 . 输出 m 个 信号 m = 2n

1.3位二进制译码器(3线-8线) A09 4 AA YY Ys YYYYY 3位 oY1 A1° 0 00 00000001 二进制 0 0 0000001 0 译码器 A° 0 0 00000100 0 00001000 真值表 00 00010000 0 0010.0.00.0 0 函数式 01000000 000000 0 Yo=444o =4A40 Y=444o Yo=4Ao Y=AA 40 Y3=44 40 Ys=AA A0Y=A

1. 3位二进制译码器 ( 3 线 – 8 线) 真值表 函数式 Y7 = A2 A1 A0 Y0 = A2 A1 A0 Y1 = A2 A1 A0 Y2 = A2 A1 A0 Y3 = A2 A1 A0 Y4 = A2 A1 A0 Y5 = A2 A1 A0 Y6 = A2 A1 A0 A0 Y0 A1 A2 Y1 Y7 3 位 二进制 译码器 . 2 1 0 A A A 7 6 5 4 3 2 1 0 Y Y Y Y Y Y Y Y 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

I 3线-8线译码器逻辑图一 输出低电平有效 1 &&& & & & & & 工作原理:

3 线 - 8 线译码器逻辑图 0 0 0 — 输出低电平有效 工作原理: 1 1 1 1 1 1 1 0 & Y7 & Y6 & Y5 & Y4 & Y3 & Y2 & Y1 & Y0 A2 A2 A1 A1 A0 A0 1 1 1 1 1 1 A2 A1 A0 0 0 1 1 1 1 1 1 1 0 1 0 1 0 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1

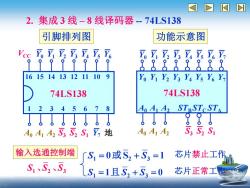

D☒I 2.集成3线-8线译码器-74LS138 引脚排列图 功能示意图 Vcc可五可4了。 7.1了3。 88888888 161514131211109 Yo YI Y2 Y3 Y4 Y5 Y6 Y7 74LS138 74LS138 12345678 A0 A1 A2 STBSTCSTA ↓。 88 A0A1A2S3S2S1了地 A0 A1 42 S3 S2 S 输入选通控制端 S1=0或S2+S3=1 芯片禁止工作 S1、S2、S LS1=1且S2+S3=0 芯片正常工作

2. 集成 3 线 – 8 线译码器 - 74LS138 引脚排列图 功能示意图 S1 、S2 、S3 输入选通控制端 S1 = 0或S2 + S3 = 1 芯片禁止工作 S1 = 1且 S2 + S3 = 0 芯片正常工作 VCC 地 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 74LS138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y7 74LS138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 A0 A1 A2 S3 S2 S1 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A0 A1 A2 STB STC STA Y7

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt