《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真

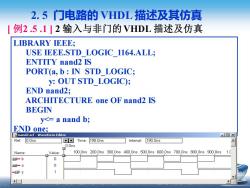

2.5门电路的VDL描述及其仿真 [例2.5.12输入与非门的VHDL描述及仿真 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY nand2 IS PORT(a,b:IN STD LOGIC; y:OUT STD LOGIC); END nand2; ARCHITECTURE one OF nand2 IS BEGIN y<=a nand b; END one; nand2.scf-Waveform Editor ▣x Ref:0.0ns Time: 190.0ns Interval:190.0ns 0.Ons Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns700.0ns800.0ns900.0ns1.0 b 0 工=a 0 y 口

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY nand2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END nand2; ARCHITECTURE one OF nand2 IS BEGIN y<= a nand b; END one; [ 例2 .5 .1 ] 2 输入与非门的VHDL 描述及仿真 2. 5 门电路的 VHDL 描述及其仿真

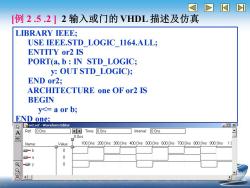

D I 例2.5.2】2输入或门的VHDL描述及仿真 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY or2 IS PORT(a,b:IN STD LOGIC; y:OUT STD LOGIC); END or2; ARCHITECTURE one OF or2 IS BEGIN y<=a or b; END one; or2.scf-Waveform Editor -▣x A Ref.0.0ns +中Time:O.Ons Interval: 0.0n3 0.0ns Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns:700.0r1s800.Cins9000ns1C 工-b 0 工-a 0 ® -@y 0 a

[例 2 .5 .2 ] 2 输入或门的 VHDL 描述及仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END or2; ARCHITECTURE one OF or2 IS BEGIN y<= a or b; END one;

例2.5.3非门的VHDL描述及仿真 LIBRARY IEEE: USE IEEE.STD LOGIC 1164.ALL; ENTITY hnot IS PORT(a:IN STD LOGIC; y:OUT STD LOGIC); END hnot; ARCHITECTURE one OF hnot IS BEGIN y<=not a; END one; hnot.scf-Waveform Editor -▣x Ref: 0.0ns 图Time: 635.0ns Interval: 635.0ns Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns700.0ns80C.0ns900.0ns1.0 工-a 0 y 1

[例 2 .5 .3 ] 非门的 VHDL 描述及仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY hnot IS PORT(a : IN STD_LOGIC; y: OUT STD_LOGIC); END hnot; ARCHITECTURE one OF hnot IS BEGIN y<= not a; END one;

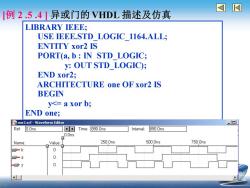

☒ [例2.5.4]异或门的VHDL描述及仿真 LIBRARY IEEE: USE IEEE.STD LOGIC 1164.ALL; ENTITY xor2 IS PORT(a,b:IN STD LOGIC; y:OUT STD LOGIC); END xor2; ARCHITECTURE one OF xor2 IS BEGIN y<=a xor b; END one; xor2.scf-Waveform Editor ▣ Ref 0.0ns 中 Time:890.0ns Interval: 890.0ns 0.Ons Name Value: 250.0ns 500.0ns 750.0ns D-b D-a 0 o●y

[例 2 .5 .4 ] 异或门的 VHDL 描述及仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY xor2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END xor2; ARCHITECTURE one OF xor2 IS BEGIN y<= a xor b; END one;

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt