《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路

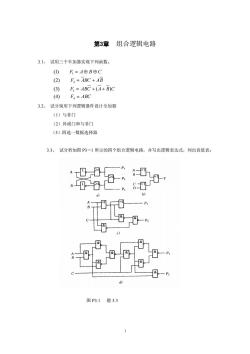

第3章组合逻辑电路 3.1、试用三个半加器实现下列函数, ()F=A⊕B⊕C (2) F=ABC+AB (3) F=ABC+(+B)C (4)F=ABC 3.2、试分别用下列逻辑器件设计全加器 (1)与非门 (2)异或门和与非门 (3)四选一数据选择器 3.3、试分析如图P3一1所示的四个组合逻辑电路,并写出逻辑表达式,列出真值表: 巴开D和, a) d) 图P3.1题3.3

1 第3章 组合逻辑电路 3.1、 试用三个半加器实现下列函数。 3.2、 试分别用下列逻辑器件设计全加器 (1)与非门 (2)异或门和与非门 (3)四选一数据选择器 3.3、 试分析如图 P3-1 所示的四个组合逻辑电路,并写出逻辑表达式,列出真值表; 图 P3.1 题 3.3 F ABC F ABC A B C F ABC AB F A B C = = + + = + = 4 3 2 1 (4) (3) ( ) (2) (1)

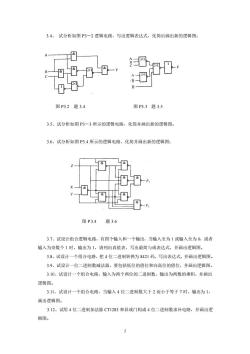

3.4、试分析如图P3一2逻辑电路,写出逻辑表达式,化简后画出新的逻辑图: 图P3.2题3.4 图P3.3题35 3.5、试分析如图P3一3所示的逻辑电路,化简并画出新的逻辑图: 3.6、试分析如图P3.4所示的逻辑电路,化简并画出新的逻辑图: 图P34题36 37、试设计组合逻辑电路,有四个输入和一个输出,当输入全为1或输入全为0,或者 输入为奇数个1时,输出为1,请列出真值表,写出最简与或表达式,并画出逻辑图。 38、试设计一个组合电路,把4位二进制转换为8421码,写出表达式,并画出逻辑图 3.9、试设计一位二进制数减法器,要包括低位的借位和向高位的借位,并画出逻辑图。 3.10、试设计一个组合电路,输入为两个两位的二进制数,输出为两数的乘积,并画出 逻辑图。 3.11、试设计一个组合电路,当输入4位二进制数大于2而小于等于7时,输出为1, 画出逻辑图。 3.12、试用4位二进制加法器CT1283和异或门构成4位二进制数求补电路,并画出逻 辑图

2 3.4、 试分析如图 P3-2 逻辑电路,写出逻辑表达式,化简后画出新的逻辑图; 图 P3.2 题 3.4 图 P3.3 题 3.5 3.5、试分析如图 P3-3 所示的逻辑电路,化简并画出新的逻辑图; 3.6、试分析如图 P3.4 所示的逻辑电路,化简并画出新的逻辑图; 图 P 3.4 题 3.6 3.7、试设计组合逻辑电路,有四个输入和一个输出,当输入全为 1 或输入全为 0,或者 输入为奇数个 1 时,输出为 1,请列出真值表,写出最简与或表达式,并画出逻辑图。 3.8、试设计一个组合电路,把 4 位二进制转换为 8421 码,写出表达式,并画出逻辑图。 3.9、试设计一位二进制数减法器,要包括低位的借位和向高位的借位,并画出逻辑图。 3.10、试设计一个组合电路,输入为两个两位的二进制数,输出为两数的乘积,并画出 逻辑图。 3.11、试设计一个组合电路,当输入 4 位二进制数大于 2 而小于等于 7 时,输出为 1, 画出逻辑图。 3.12、试用 4 位二进制加法器 CT1283 和异或门构成 4 位二进制数求补电路,并画出逻 辑图

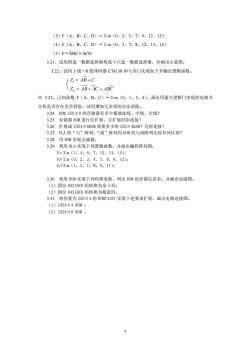

3.13、试用一片CT1283实现数值比较,当输入4位二进制数大于等于8时,输出为1, 否则为0(提示:用进位输出端C为.输出)。 3.14、试用两片数值比较器CT1085实现两个7位二进制数比较的逻辑图。 3.15、试用3线-8线译码器扩展为5线一32线译码器,并画 出示意图。 3.16、试用3线一8译码器CT4138和与非门实现下列逻辑函 数。(1)Y=AC+BC+ABC (2)Y=(A+B(A+C Y。Y,YY,Y,下 (3)Y=AB+BC T413w (4)Y=ABC+AC 3.17、试写出图P3.5由四选一数据选择器构成的输出Z的 A月C 100 最简与或表达式。 P3.5题3.17 3.18、试用四选一数据选择器C1153分别实现下列逻辑函数。 (1)Y=ABC+ABC+AB (2)Y=A+B (3)Y=ABC+ABC+ABC+ABC 3.19、试用双四选一数据选择器CT1153和逻辑门分别实现下列逻辑函数(要尽可能节 省芯片)。 图3.6题3.19 (1)Z(A、B、CD)=Σm(0、2、3、5、6、7、8、9、10、12) (2)Z(A、B、C.D)=Σm(0、2、45,6、7、8、9、13、15) (3)Z(A、B、C、D)=ABD+ABC 3.20、试用八选一数据选择器CT1151和逻辑门分别实现下列逻辑函数。 (1)F(A、B、C)=m(0、1、5、6) (2)F(A、B、C)=Σm(1、2、4、7)

3 3.13、试用一片 CT1283 实现数值比较,当输入 4 位二进制数大于等于 8 时,输出为 1, 否则为 0(提示:用进位输出端 C0 为.输出)。 3.14、试用两片数值比较器 CT1085 实现两个 7 位二进制数比较的逻辑图。 3.15、试用 3 线-8 线译码器扩展为 5 线-32 线译码器,并画 出示意图。 3.16、试用 3 线-8 译码器 CT4138 和与非门实现下列逻辑函 数。 (1) Y = AC + BC + ABC (2) Y = (A + B)(A + C) (3) Y = AB+ BC (4) Y = ABC + AC 3.17、试写出图 P3.5 由四选一数据选择器构成的输出 Z 的 最简与或表达式。 P3.5 题 3.17 3.18、试用四选一数据选择器 C1153 分别实现下列逻辑函数。 (1) Y = ABC + ABC + AB (2) Y = A + B (3) Y = ABC + ABC + ABC + ABC 3.19、试用双四选一数据选择器 CT1153 和逻辑门分别实现下列逻辑函数(要尽可能节 省芯片)。 图 3.6 题 3.19 (1)Z(A、B、C、D)=Σm(0、2、3、5、6、7、8、9、10、12) (2)Z(A、B、C、D)=Σm(0、2、4、5、6、7、8、9、13、15) (3)Z(A、B、C、D)= ABD + ABC 3.20、试用八选一数据选择器 CT1151 和逻辑门分别实现下列逻辑函数。 (1)F(A、B、C)=Σm(0、1、5、6) (2)F(A、B、C)=Σm(1、2、4、7)

(3)F(A、B、C、D)=Σm(0、2、5、7、9、12、15) (4)F(A、B、C、D)=Σm(0、3、7、8、12、13、14) (5)F=ABC+ACD 3.21、试用四选一数据选择器构成十六选一数据选择器,并画出示意图 3.22、试用3线一8线译码器CT4138和与非门实现如下多输出逻辑函数 ∫Z=AB+C Z,=AB+AC+ABC ※3.23、己知函数F(A、B、C)=Σm(0、1、3、4),画出用最少逻辑门实现的电路并 分析是否存在竞争冒险,试用增加冗余项的办法消除。 324 OW256×8的存储器有多少根地址线、字线、位线 3.25存储器OW进行位扩展、字扩展时如连接? 3.26扩展成1024×8RAM需要多少块256×4RAM?怎样连接? 3.27PLA的“与”阵列,“或”阵列同OM的与或阵列比较有何区别? 328用P0W实现全减器 3.29利用RLA实现下列逻辑函数,并画出编程阵列图 F=Σm(3,4,6,7,12,14,15): F=zm(0,2,3,4,7,8,9,12): F=m(1,3,7,8,9,11): 3.30利用ROM实现下列码型变换,列出ROM的存储信息表,并画出电路图 (1)四位8421BCD码转换为余3码 (2)四位8421BCD码转换为格雷码。 3.31将容量为256×4的ROM74187实现下述要求扩展,画出电路连接图。 (1)1024×4R0w: (2)1024×8R0M

4 (3)F(A、B、C、D)=Σm(0、2、5、7、9、12、15) (4)F(A、B、C、D)=Σm(0、3、7、8、12、13、14) (5)F=ABC+ACD 3.21、试用四选一数据选择器构成十六选一数据选择器,并画出示意图。 3.22、试用 3 线-8 线译码器 CT4138 和与非门实现如下多输出逻辑函数。 Z1 = AB + C Z2 = AB + AC + ABC ※ 3.23、已知函数 F(A、B、C)=Σm(0、1、3、4),画出用最少逻辑门实现的电路并 分析是否存在竞争冒险,试用增加冗余项的办法消除。 3.24 ROM 256×8 的存储器有多少根地址线、字线、位线? 3.25 存储器 ROM 进行位扩展、字扩展时如连接? 3.26 扩展成 1024×8RAM 需要多少块 256×4RAM?怎样连接? 3.27 PLA 的“与”阵列,“或”阵列同 ROM 的与或阵列比较有何区别? 3.28 用 ROM 实现全减器。 3.29 利用 RLA 实现下列逻辑函数,并画出编程阵列图。 F1=Σm(3,4,6,7,12,14,15); F2=Σm(0,2,3,4,7,8,9,12); F3=Σm(1,3,7,8,9,11); 3.30 利用 ROM 实现下列码型变换,列出 ROM 的存储信息表,并画出电路图。 (1)四位 8421BCD 码转换为余 3 码; (2)四位 8421BCD 码转换为格雷码。 3.31 将容量为 256×4 的 ROM74187 实现下述要求扩展,画出电路连接图。 (1)1024×4 ROM ; (2)1024×8 ROM

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程试卷习题(自我检测)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第6章 脉冲产生和整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第5章 时序逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第4章 触发器.doc

- 内蒙古科技大学:《数字电子技术》课程设计指导书.doc

- 内蒙古科技大学:《数字电子技术》课程教学实验指导书(共八个实验).doc

- 内蒙古科技大学:《数字电子技术》课程实验教学大纲 Electronic Techniques Experiments.doc

- 内蒙古科技大学:《数字电子技术》课程教学大纲 Digital electric technology.doc

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第十章 可编程逻辑器件.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第六章 时序逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第八章 半导体存储器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第九章 数模与模数转换器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第七章 脉冲单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第五章 记忆单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第二章 分析与设计数字电路的工具.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第三章 逻辑门电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第一章 初识数字电路.ppt

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH11 逻辑代数基本概念、公式和定理.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH12 逻辑函数的化简方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH13 逻辑函数的表示方法及其相互之间的转换.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH14 EDA技术的基础知识.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 SUM1 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH20 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH21 二极管、三极管的开关特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH22 分立元器件门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH23 CMOS集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH24 TTL 集成门电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 CH25 门电路的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第二章 门电路 SUM2 小结.ppt