石河子大学:《数字电子技术》课程教学资源(PPT课件)第六章 时序逻辑电路

数字电子技术Digital Eleetronics Technolo 第六章时序逻辑电路 名阿子大学《数字电子技术》保程组 电 活:0993-2057237 电子邮箱:rl mac@shzu.edu.cn 机电学院电气工程系 上一页下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 第六章 时序逻辑电路 数字电子技术Digital Electronics Technology 石河子大学《数字电子技术》课程组 电 话:0993-2057237 电子邮箱:rl_mac@shzu.edu.cn

6.1时序逻辑电路的基本概念 6.2时序逻辑电路的一般分析方法 6.3计数器 6.4寄存器 6.5时序逻辑电路的设计方法 6.6时序逻辑电路的VHDL描述 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 6.4 寄存器 6.2 时序逻辑电路的一般分析方法 6.3 计数器 6.5 时序逻辑电路的设计方法 6.1 时序逻辑电路的基本概念 6.6 时序逻辑电路的VHDL描述

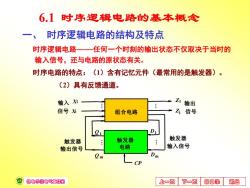

6.1时序逻辑电路的基本概念 一、时序逻辑电路的结构及特点 时序逻辑电路一任何一个时刻的输出状态不仅取决于当时的 输入信号,还与电路的原状态有关。 时序电路的特点:(1)含有记忆元件(最常用的是触发器)。 (2)具有反馈通道。 输入1 输出 信号ǚ 组合电路 Z信号 触发器 触发器 触发器 : 输出信号 电路 输入信号 CP 机电学院电气工程系 上一页 下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 6.1 时序逻辑电路的基本概念 一、 时序逻辑电路的结构及特点 时序逻辑电路————任何一个时刻的输出状态不仅取决于当时的 输入信号,还与电路的原状态有关。 时序电路的特点:(1)含有记忆元件(最常用的是触发器)。 (2)具有反馈通道。 组合电路 触发器 电路 X1 Xi Z1 Zj Q 1 Q m D1 Dm . . . . 输入 信号 信号 输出 触发器 触发器 输入信号 输出信号 CP

6.2时序逻辑电路的一般分析方法 一、分析时序逻辑电路的一般步骤 1.由逻辑图写出下列各逻辑方程式: (1)各触发器的时钟方程。 (2)时序电路的输出方程。 (3)各触发器的驱动方程。 2.将驱动方程代入相应触发器的特性方程,求得时序逻辑电路的状 态方程。 3.根据状态方程和输出方程,列出该时序电路的状态表,画出状态 图或时序图。 4.根据电路的状态表或状态图说明给定时序逻辑电路的逻辑功能。 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 6.2 时序逻辑电路的一般分析方法 一、分析时序逻辑电路的一般步骤 1.由逻辑图写出下列各逻辑方程式: (1)各触发器的时钟方程。 (2)时序电路的输出方程。 (3)各触发器的驱动方程。 2.将驱动方程代入相应触发器的特性方程,求得时序逻辑电路的状 态方程。 3.根据状态方程和输出方程,列出该时序电路的状态表,画出状态 图或时序图。 4.根据电路的状态表或状态图说明给定时序逻辑电路的逻辑功能

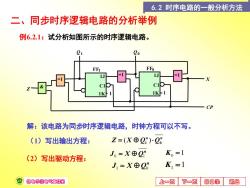

6.2时序电路的一般分析方法 二、同步时序逻辑电路的分析举例 例6.2.1:试分析如图所示的时序逻辑电路。 FFo CP 解:该电路为同步时序逻辑电路,时钟方程可以不写。 (1)写出输出方程: Z=(X⊕2")2 J。=X⊕2” K。=1 (2)写出驱动方程: J1=X⊕2 K1=1 机电学院电气工程系 上一页下-页 回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 二、同步时序逻辑电路的分析举例 解:该电路为同步时序逻辑电路,时钟方程可以不写。 (1)写出输出方程: n n Z X Q1 Q0 = ( ) n J0 = X Q1 K0 =1 n J1 = X Q0 K1 =1 (2)写出驱动方程: 例6.2.1:试分析如图所示的时序逻辑电路。 1J 1K C1 1J 1K C1 Q1 Q0 CP X Z =1 =1 =1 & FF1 FF0 1 1 6.2 时序电路的一般分析方法

6.2时序电路的一般分析方法 (3)写出JK触发器的特性方程,然后将各驱动方程代入JK触发器 的特性方程,得各触发器的次态方程: 2"+1=J20+K2=(X⊕2")2 2"+=J,2"+K,2=(X⊕2)21 (4)作状态转换表及状态图 ①当X=0时:触发器的次态方程简化为: 2m+=2"26 输出方程简化为:Z=2”Q 2"1=221 作出X=0的状态表Z=(X⊕2)Q X=0时的状态图 现 态 次 态 输出 21n20n 211Q1 Z 0 0 0 1 0 0 1 1 0 0 0 0 0 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (4)作状态转换表及状态图 ①当X=0时:触发器的次态方程简化为: 作出X=0的状态表: n n n n n Q J0 Q0 K0 Q0 X Q1 Q0 1 0 = + = ( ) + n n n n n Q J1 Q1 K1 Q1 X Q0 Q1 1 1 = + = ) + ( n n n Q Q1 Q0 1 0 = + n n n Q Q0 Q1 1 1 = + 输出方程简化为: n n Z = Q1 Q0 现 态 次 态 输 出 Q1 n Q0 n Q1 n+1 Q0 n+1 Z 0 0 0 1 0 1 1 0 0 1 0 0 0 0 1 n n Z X Q1 Q0 = ( ) (3)写出JK触发器的特性方程,然后将各驱动方程代入JK触发器 的特性方程,得各触发器的次态方程: X=0时的状态图 /1 Q /0 Q /0 0 01 10 1 00 6.2 时序电路的一般分析方法

6.2时序电路的一般分析方法 各触发器的次态方程: 21=J20+K26=(X⊕2")2 2+=J12”+K2=(X⊕2)2 ②当X=1时:触发器的次态方程简化为: 2"+=2"2 2+1=221 X=1时的状态图 212o 输出方程简化为:Z=2”2 作出X=1的状态表: Z=(X⊕2")2 0 现 态 次态 输出 完整的状态图 Oin Oon 21+1Q0+1 Z 0/0 0 0 1 0 1 00 01 0 0 1 0 1/0 0 0 0 0 /0 0/0 将X=0与X=1的状态图合并起来得完整的状态图。 0/1 达机电学院电气王程深 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 作出X=1的状态表: 将X=0与X=1的状态图合并起来得完整的状态图。 n n n Q Q1 Q0 1 0 = + n n n Q Q0 Q1 1 1 = + n n Z = Q1 Q0 各触发器的次态方程: n n n n n Q J0 Q0 K0 Q0 X Q1 Q0 1 0 = + = ( ) + n n n n n Q J1 Q1 K1 Q1 X Q0 Q1 1 1 = + = ) + ( 现 态 次 态 输 出 Q1 n Q0 n Q1 n+1 Q0 n+1 Z 0 0 1 0 1 0 0 1 1 0 1 0 0 0 0 n n Z X Q1 Q0 = ( ) ②当X=1时:触发器的次态方程简化为: 输出方程简化为: X=1时的状态图 /0 00 10 /0 Q 01 1 0 /1 Q 1/0 01 0/1 1/1 0/0 00 0/0 10 1/0 完整的状态图 6.2 时序电路的一般分析方法

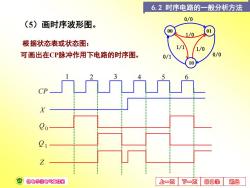

6.2时序电路的一般分析方法 0/0 (5)画时序波形图。 00 1/0 根据状态表或状态图: /0 可画出在CP脉冲作用下电路的时序图。 0/1 0/0 Z 机电学院电气工程系 上一页下页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (5)画时序波形图。 X CP 1 2 3 4 5 6 Q0 Z Q1 根据状态表或状态图: 可画出在CP脉冲作用下电路的时序图。 1/0 01 0/1 1/1 0/0 00 0/0 10 1/0 6.2 时序电路的一般分析方法

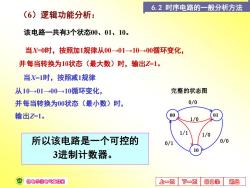

6.2时序电路的一般分析方法 (6)逻辑功能分析: 该电路一共有3个状态00、01、10。 当X=0时,按照加1规律从0001→10→00循环变化, 并每当转换为10状态(最大数)时,输出☑=1。 当X=1时,按照减1规律 从10→01→00→10循环变化, 完整的状态图 并每当转换为00状态(最小数)时, 0/0 输出Z=1。 00 1/0 1/1 1/0 所以该电路是一个可控的 0/1 0/0 3进制计数器。 10 机电学院电气工程系 上一页下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (6)逻辑功能分析: 当X=1时,按照减1规律 从10→01→00→10循环变化, 并每当转换为00状态(最小数)时, 输出Z=1。 该电路一共有3个状态00、01、10。 当X=0时,按照加1规律从00→01→10→00循环变化, 并每当转换为10状态(最大数)时,输出Z=1。 所以该电路是一个可控的 3进制计数器。 1/0 01 0/1 1/1 0/0 00 0/0 10 1/0 完整的状态图 6.2 时序电路的一般分析方法

6.2时序电路的一般分析方法 三、异步时序逻辑电路的分析举例 例6.2.2:试分析如图所示的时序逻辑电路 FF FFo CP 该电路为异步时序逻辑电路。具体分析如下: (1)写出各逻辑方程式。 ①时钟方程: CP=CP (时钟脉冲源的上升沿触发。) CP1=2o(当F℉的2由0→1时,Q1才可能改变状态。) 机电学院电气工程系 上一页 下-页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 三、异步时序逻辑电路的分析举例 例6.2.2:试分析如图所示的时序逻辑电路 该电路为异步时序逻辑电路。具体分析如下: (1)写出各逻辑方程式。 ①时钟方程: CP0=CP (时钟脉冲源的上升沿触发。) CP1=Q0 (当FF0的Q0由0→1时,Q1才可能改变状态。) C1 FF0 ∧ 1D FF1 C1 ∧ 1D CP Q 1 Q 0 Z & 6.2 时序电路的一般分析方法

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第八章 半导体存储器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第九章 数模与模数转换器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第七章 脉冲单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第五章 记忆单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第二章 分析与设计数字电路的工具.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第三章 逻辑门电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第一章 初识数字电路.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第9章 DSP Builder设计初步.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第10章 DSP Builder设计深入.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第8章 VHDL结构.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第7章 VHDL语句.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第6章 16位CISC CPU设计.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第5章 VHDL状态机.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第4章 Quartus II使用方法.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第3章 VHDL基础.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第2章 PLD硬件特性与编程技术.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第1章 概述.ppt

- 《数字电子技术》课程教学资源(自测题)第十一章 AD和DA转换器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第十章 脉冲产生和整形自测题和答案.doc

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第十章 可编程逻辑器件.ppt

- 内蒙古科技大学:《数字电子技术》课程教学大纲 Digital electric technology.doc

- 内蒙古科技大学:《数字电子技术》课程实验教学大纲 Electronic Techniques Experiments.doc

- 内蒙古科技大学:《数字电子技术》课程教学实验指导书(共八个实验).doc

- 内蒙古科技大学:《数字电子技术》课程设计指导书.doc

- 《数字电子技术》课程试卷习题(自我检测)第4章 触发器.doc

- 《数字电子技术》课程试卷习题(自我检测)第5章 时序逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第6章 脉冲产生和整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第4章 触发器.doc

- 《数字电子技术》课程授课教案(讲义)第5章 时序逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程授课教案(讲义)第2章 门电路.doc

- 《数字电子技术》课程教学课件(PPT讲稿)第一章 逻辑代数基础与EDA技术的基础知识 CH10 概述.ppt