石河子大学:《数字电子技术》课程教学资源(PPT课件)第五章 记忆单元电路

数字电子技术Digital Eleetronics Technolo 第五章记忆单元电路 石阿子大学《煞字电子枝术》裸程组 电 话:0993-2057237 电子邮精:rl mac@shzu.edu.cn 机电学院电气工程 上一页下一页回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 第五章 记忆单元电路 数字电子技术Digital Electronics Technology 石河子大学《数字电子技术》课程组 电 话:0993-2057237 电子邮箱:rl_mac@shzu.edu.cn

5.1锁存器 5.2触发器 5.3集成锁存器与触发器 5.4锁存器与触发器的VHDL描述 机电学院电气工程系 上一凤 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 5.2 触发器 5.3 集成锁存器与触发器 5.1 锁存器 5.4 锁存器与触发器的VHDL描述

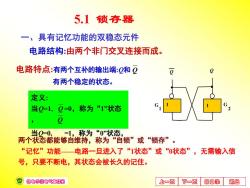

5.1 锁存器 一、具有记忆功能的双稳态元件 电路结构:由两个非门交叉连接而成。 电路特点:有两个互补的输出端:Q和Q 有两个稳定的状态。 定义: 当0=1,Q=0,氵 称为“1”状态 Q 当0=0, =1,称为“0状态, 两个状态都能够自维持,称为“自锁”或“锁存”。 “记忆”功能 电路一旦进入了“1状态”或“0状态”,无需输入信 号,只要不断电,其状态会被长久的记住。 机电学院电气工程系 上页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 5.1 锁存器 一、具有记忆功能的双稳态元件 电路结构:由两个非门交叉连接而成。 G G Q Q 2 1 1 1 电路特点:有两个互补的输出端:Q和 有两个稳定的状态。 Q 定义: 当Q=1, =0,称为“1”状态 , 当Q=0, =1,称为“0”状态, Q Q 两个状态都能够自维持,称为“自锁”或“锁存”。 “记忆”功能——电路一旦进入了“1状态”或“0状态”,无需输入信 号,只要不断电,其状态会被长久的记住

5.1锁存器 二、用与非门组成的RS锁存器 1.电路结构:增加两个输入端 R:置0输入端 S:置1输入端 逻辑符号 低电平有 置0端 置1端 效 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 二、 用与非门组成的RS锁存器 1. 电路结构: 增加两个输入端 R: 置0输入端 S: 置1输入端 置0端 置1端 低电平有 效 5.1锁存器 R G & G Q 2 Q & 1 S Q S Q R 逻辑符号

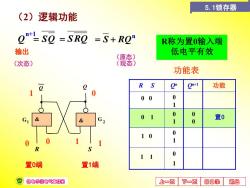

5.1锁存器 (2)逻辑功能 2"1s0 =SRO =S+RO R称为置0输入端 输出 低电平有效 (原态) (次态) (现态) 功能表 R S On O1 功能 00 0 1 1 0 置0 1 0 0 0 1 0 置0端 置1端 心,机电学院电气工狂系 上一页 下一页 回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (2)逻辑功能 R S Qn Qn+1 功能 功能表 0 1 1 1 0 0 置0 0 0 R称为置0输入端 低电平有效 0 1 0 1 1 0 0 1 1 1 0 1 0 0 0 1 Q = SQ = SRQ = S + RQ 输出 输出 (次态) n n+1 (原态) (现态) 置0端 置1端 0态 5.1锁存器 R G & G Q 2 Q & 1 S

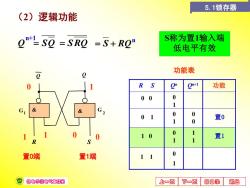

5.1锁存器 (2)逻辑功能 0"L s0 =SRO =5+Ro" S称为置1输入端 低电平有效 功能表 R S 功能 00 0 1 1 0 0 置0 1 0 0 10 置1 1 1 置0端 置1端 0 机电学院电气工程系 上一凤 下一贝 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 R S Qn Qn+1 功能 功能表 1 0 0 0 1 1 置1 1 1 S称为置1输入端 低电平有效 0 1 0 1 1 0 0 1 1 1 0 1 0 0 0 1 0 0 置0 Q = SQ = SRQ = S + RQ n n+1 置0端 置1端 1态 (2)逻辑功能 5.1锁存器 R G & G Q 2 Q & 1 S

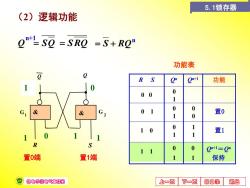

5.1锁存器 (2)逻辑功能 Q"1S0=SR0=5+R0" 功能表 O+1 功能 00 0 1 0 1 0 0 置0 1 0 0 0 置1 1 0*1=Q 置0端 置1端 保持 机电学院电气工程系 上一页 下一页 回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 R S Qn Qn+1 功能 功能表 0 1 置0 0 0 0 1 1 0 置1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 0 1 1 Qn+1=Qn 保持 0 0 0 1 Q = SQ = SRQ = S + RQ n n+1 置0端 置1端 (2)逻辑功能 5.1锁存器 R G & G Q 2 Q 1 & S

5.1锁存器 (2)逻辑功能 0"L so =SRO )=S+RQ” 功能表 R S Q+1 功能 00 0 × 不定 0 1 0 0 置0 1 0 10 0 1 1 置1 1 11 0 0 21=Qm 置0端 置1端 保持 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 R S Qn Qn+1 功能 功能表 0 1 置0 0 0 0 1 1 0 置1 1 1 0 1 1 1 0 0 1 1 1 1 0 1 1 0 1 1 Qn+1=Qn 保持 0 0 × 不定 × 0 1 ? ? Q = SQ = SRQ = S + RQ n n+1 置0端 置1端 (2)逻辑功能 5.1锁存器 R G & G Q 2 Q & 1 S

5.1锁存器 (3)波形分析 例5.1.1在用与非门组成的RS锁存器中,设初始状态为0,已 知输入R,S的波形图,画出两输出端的波形图。 机电学院电气工程系 上一页 下一页 回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 R S Q Q (3)波形分析 例5.1.1 在用与非门组成的RS锁存器中,设初始状态为0,已 知输入R、S的波形图,画出两输出端的波形图。 5.1锁存器

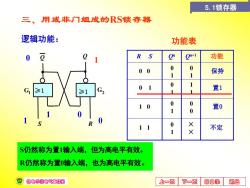

5.1锁存器 三、用或非门组成的RS锁存器 逻辑功能: 功能表 R O+1 功能 0 0 0 1 保持 0 1 置1 1 0 0 置0 0 0 不定 1 S仍然称为置1输入端,但为高电平有效。 R仍然称为置0输入端,也为高电平有效。 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 R S Qn Qn+1 功能 功能表 0 1 置1 1 1 0 1 1 0 置0 0 0 0 1 1 1 0 1 × × 不定 0 0 保持 0 1 0 1 逻辑功能: 1 0 0 0 1 1 三、用或非门组成的RS锁存器 S仍然称为置1输入端,但为高电平有效。 R仍然称为置0输入端,也为高电平有效。 5.1锁存器 Q S G1 G2 R ≥1 ≥1 Q

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第二章 分析与设计数字电路的工具.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第三章 逻辑门电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第一章 初识数字电路.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第9章 DSP Builder设计初步.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第10章 DSP Builder设计深入.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第8章 VHDL结构.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第7章 VHDL语句.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第6章 16位CISC CPU设计.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第5章 VHDL状态机.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第4章 Quartus II使用方法.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第3章 VHDL基础.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第2章 PLD硬件特性与编程技术.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第1章 概述.ppt

- 《数字电子技术》课程教学资源(自测题)第十一章 AD和DA转换器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第十章 脉冲产生和整形自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第七章 半导体存储器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第四章 组合逻辑电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第六章 时序逻辑电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第五章 触发器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第二章 逻辑门电路自测题和答案.doc

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第七章 脉冲单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第九章 数模与模数转换器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第八章 半导体存储器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第六章 时序逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第十章 可编程逻辑器件.ppt

- 内蒙古科技大学:《数字电子技术》课程教学大纲 Digital electric technology.doc

- 内蒙古科技大学:《数字电子技术》课程实验教学大纲 Electronic Techniques Experiments.doc

- 内蒙古科技大学:《数字电子技术》课程教学实验指导书(共八个实验).doc

- 内蒙古科技大学:《数字电子技术》课程设计指导书.doc

- 《数字电子技术》课程试卷习题(自我检测)第4章 触发器.doc

- 《数字电子技术》课程试卷习题(自我检测)第5章 时序逻辑电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第6章 脉冲产生和整形电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第1章 逻辑代数与EDA技术的基础知识.doc

- 《数字电子技术》课程试卷习题(自我检测)第2章 门电路.doc

- 《数字电子技术》课程试卷习题(自我检测)第3章 组合逻辑电路.doc

- 《数字电子技术》课程授课教案(讲义)第6章 脉冲产生与整形电路.doc

- 《数字电子技术》课程授课教案(讲义)第7章 DA与AD转换电路.doc

- 《数字电子技术》课程授课教案(讲义)第3章 组合逻辑电路.doc