《数字电子技术》课程教学资源(自测题)第四章 组合逻辑电路自测题和答案

第四章习 一、选择题 1、如果对键盘上108个符号进行二进制编码,则至少要()位二进 制数码。 (a)5b)6e)7 2、半加器逻辑符号如图所示,当A=“1”,B=“1”时,C和S分 别 (a)C=0S=0b)C=0S=1e)C=1S=0 A S B co -C 3、二进制编码表如下所示,指出它的逻辑式为 (a)B=273 4=Y1.Y3 b)B=y。·7 A=y2.73 @B=2了 4=YL.Y2 输■ 出 入 B A 0 0 0 5 0 4、编码器的逻辑功能是( (a)把某种二进制代码转换成某种输出状态 ⑥)将某种状态转换成相应的二进制代码 (©)把二进制数转换成十进制数 5、译码器的逻辑功能是( (@把某种二进制代码转换成某种输出状态 山)把某种状态转换成相应的二进制代码 (@)把十进制数转换成二进制数

第四章 习题 一、 选择题 1、 如果对键盘上 108 个符号进行二进制编码,则至少要( )位二进 制数码。 (a) 5 (b) 6 (c) 7 2、 半 加 器 逻 辑 符 号 如 图 所 示, 当 A=“1”,B=“1”时,C 和 S 分 别 为( )。 (a) C = 0 S = 0 (b) C = 0 S = 1 (c) C = 1 S = 0 ∑ CO A B C S 3、二 进 制 编 码 表 如 下 所 示, 指 出 它 的 逻 辑 式 为( )。 (a) B=Y2 Y3 A=Y1 Y3 (b) B=Yo Y1 A=Y2 Y3 (c) B=Y2 Y3 A= Y1 Y2 输 输 出 入 B A Y0 0 0 Y1 0 1 Y2 1 0 Y3 1 1 4、 编 码 器 的 逻 辑 功 能 是( ) 。 (a) 把 某 种 二 进 制 代 码 转 换 成 某 种 输 出 状 态 (b) 将某 种 状 态 转 换 成 相 应 的二 进 制 代 码 (c) 把 二 进 制 数 转 换 成 十进 制 数 5、译 码 器 的 逻 辑 功 能 是 ( )。 (a) 把 某 种 二 进 制 代 码 转 换 成 某 种 输 出 状 态 (b) 把 某 种 状 态 转 换 成 相 应 的二 进 制 代 码 (c) 把 十 进 制 数 转 换 成 二进 制 数

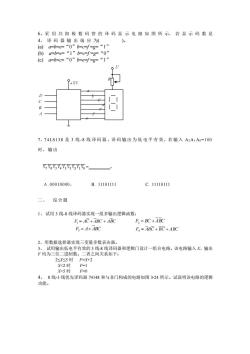

6、采用共阳极数码管的译码显示电路如图所示,若显示码数是 4,译码器输出端应为( =e=“0” fg“1” 间)be“1”b-g“0” (c)a=b=c=“0”b=ef=g=“1” 9+5V 7、74LS138是3线-8线译码器,译码输出为低电平有效,若输入AA1A0=100 时,输出 V,VGYsVaVYsYaVYo- A.00010000, B.11101111 C.11110111 二、 综合题 1、试用3线8线译码器实现一组多输出逻辑函数: F=AC+ABC+ABC F,=BC+ABC F=A+ABC F.=ABC+BC+ABC }用数据选择器实现变量多数表决器 器和逻辑门设计一组合电路。该电路输入X,输出 2X5时 y时 F=1 5时F=0 4、8线-3线优先译码器74148和与非门构成的电路如图324所示。试说明该电路的逻辑 功能

6、采 用 共 阳 极 数 码 管 的 译 码 显 示 电 路 如 图 所 示, 若 显 示 码 数 是 4, 译 码 器 输 出 端 应 为( )。 (a) a=b=e=“0”b=c=f =g=“1” (b) a=b=e=“1”b=c=f =g=“0” (c) a=b=c=“0”b=e=f =g=“1” A B C D R U a c d e g +5V • f b 7、7 4 LS13 8 是 3 线-8 线 译码 器 ,译 码 输出 为 低 电平 有 效,若 输入 A2A1 A0=1 00 时,输出 = 。 A.00010000, B. 11101111 C. 11110111 二、 综合题 1、试用 3 线-8 线译码器实现一组多输出逻辑函数: F1 = AC + ABC + ABC F2 = BC + ABC F3 = A+ ABC F4 = ABC + BC + ABC 2、用数据选择器实现三变量多数表决器。 3、 试用输出低电平有效的 3 线-8 线译码器和逻辑门设计一组合电路。该电路输入 X,输出 F 均为三位二进制数。二者之间关系如下: 2≤X≤5 时 F=X+2 X5 时 F=0 4、 8 线-3 线优先译码器 74148 和与非门构成的电路如图 3-24 所示。试说明该电路的逻辑 功能

图3.24编码电路 5、试分析图311所示逻辑图的功能。 DEMUX 令 F 415 74138 F7 图311逻辑图

图3-24 编码电路 S I0 I1 I2 I3 I4 I5 I6 I7 1 1 F F0 3 F2 F1 A2 A1 A0 I9 I8 & & 5、试分析图 3-11 所示逻辑图的功能。 “1” A2 A1 A0 A2 A1 A0 A2 A1 A0 S3 S2 D0 S1 D1 D2 D3 D4 D5 D6 D7 F0 F1 F2 F3 F4 F5 F6 F7 F G E 74151 MUX DEMUX 74138 图 3-11 逻辑图

第四章习题答案 一、选择题 将都为之和影式 F=AC+ABC+ABC=ABC+ABC+ABC+ABC=m+mm+m F BC+ABC=ABC+ABC+ABC=m+m F3=A+ABC ABC+ABC+ABC+ABC+ABC=m+m+ms+m+m F=ABC+BC+ABC ABC+ABC+ABC+ABC =m+m+m+m 令A=A,A=B,A0=C,则译码器中的m一m即为F中的m~m,把m~m变成 m-m。F=mmmm。=F·E·F-F E=mmm,=F万E =mmmm。m,=·万下F万 F=m。·m·m,·m,=F。·E·F·F F3 日8b。9 Fo F F2 Fs F4 Fs Fe F7 74138 S1 S2 S5 Ao AI A2 I 图3-12逻辑图 2、解:三变量多数表决器在例1中已分析,其逻辑表达式为 Y-AB+BC+AC =ABC+ABC+ABC+ABC =m+m+m 则有: D0=D1=D2=D4=0 D3=D5=D6=Dh=1

第四章 习题答案 一、选择题 ccaba ac 二综合题 1、 解: 将 F1~F4 化为最小项之和形式: F1 = AC + ABC + ABC = ABC + ABC + ABC + ABC = m4 +m6 +m3 +m5 F2 = BC + ABC = ABC + ABC + ABC = m3 +m7 +m1 F3 = A+ ABC = ABC + ABC + ABC + ABC + ABC = m7 +m6 +m5 +m4 +m3 F4 = ABC + BC + ABC = ABC + ABC + ABC + ABC = m2 + m0 +m4 + m7 令 A2=A,A1=B,A0=C,则译码器中的 m0~m7 即为 Fi 中的 m0~m7,把 m0~m7 变成 m0 − m7 。 F1 m3 m4 m5 m6 F3 F4 F5 F6 = = F2 m1 m3 m7 F1 F3 F7 = = F3 m3 m4 m5 m6 m7 F3 F4 F5 F6 F7 = = F4 m0 m2 m4 m7 F0 F2 F4 F7 = = 2、解:三变量多数表决器在例 1 中已分析, 其逻辑表达式为 Y=AB+BC+AC 则有: D0 = D1 = D2 = D4 = 0 D3 = D5 = D6 = D7 = 1 F0 F1 F2 F3 F4 F5 F6 F7 74138 S1 S2 S3 A0 A1 A2 5V C B A F1 图 3-12 逻辑图 F2 F3 F4 & & & & m3 m5 m6 m7 ABC ABC ABC ABC = + + + = + + +

画出逻辑图如图4,24所示 74LS151 D。D1DD3D4DD。D7 0 1 图4.24逻辑图 3、解:根据题意列出真值表3-12。由真值表312可直接画出逻辑图3-30。 表3-12题3-12真值表 的i指F万FF o 000 001 001 100 01 Fo F1 F2 F3 F4 FsFs F7 100 110 74138 101 111 110 000 11 000 图330逻辑图 解:74148的输出为输入信号下角标的二进制数的反码。例如,对'编码得 本A瓦,=000(11的反码),但是经非门取反后,便得到原码,例如对编码得FF=I1, 74148输入低电平有效,5=0时编码,5=1时不编码,输出4A4=111,17的优先级 最高,0的优先级最低。按照输出为原码的分析,可以得出对编码时,输出FFFF应 等于101:对编码时,输出F5F55,应等于100:由图看出,当,=0×时,F=, F.由于5=1,74148不编码,4瓦=111,使F=f=0.达到了FFFn等于1001 的要求.当,1,=×0时,F1,5=1,74148不编码,44五=1l,FwF:FFw100. 1,=11时,F0.5-0,74148编码。74148和与丰门构成了十线四线编码器。 5、解: E0时,八选一数据选择器74151、三态缓冲器G、3线8线译码器74138均处于“工作状 态”。当A2414和=000时,74151选择D作为输入数据通道。74138选择0作为输出通道。此

画出逻辑图如图 4.24 所示 图 4.24 逻辑图 3、解:根据题意列出真值表 3-12。由真值表 3-12 可直接画出逻辑图 3-30。 表 3-12 题 3-12 真值表 X2 X1 X0 F2 F1 F0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 1 0 0 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 0 0 0 4、 解:74148 的输出为输入信号下角标的二进制数的反码。例如,对 7 I 编码得 A2 A1A0 = 000 (111的反码)。但是经非门取反后,便得到原码。例如对 7 I 编码得F2F1F0=111。 74148 输入低电平有效, S =0 时编码, S =1 时不编码,输出 A2 A1A0 = 111, 7 I 的优先级 最高, 0 I 的优先级最低。按照输出为原码的分析,可以得出对 9 I 编码时,输出 F3F2F1F0 应 等于 1001;对 8 I 编码时,输出 F3F2F1F0 应等于 1000;由图看出,当 I 9 I 8 = 0 时,F3=1, F0=1。由于 S =1,74148 不编码, A2 A1A0 = 111 ,使 F2=F1=0。达到了 F3F2F1F0 等于 1001 的要求。当 I 9 I 8 = 0 时,F3=1, S =1,74148 不编码, A2 A1A0 = 111,F3F2F1F0=1000。 I 9 I 8 = 11 时,F3=0, S =0, 74148 编码。74148 和与非门构成了十线-四线编码器。 5、解: E =0 时,八选一数据选择器 74151、三态缓冲器 G、3 线-8 线译码器 74138 均处于“工作状 态”。当 A2A1A0=000 时,74151 选择 D0 作为输入数据通道。74138 选择 0 作为输出通道。此 E A0 A1 A2 D0 D1 D2 D3 D4 D5 D6 D7 Y 74LS151 A B C 1 0 F0 F1 F2 F3 F4 F5 F6 F7 74138 S1 S2 S3 A0 A1 A2 5V X0 X1 X2 图 3-30 逻辑图 F0 F2 F1 & & &

时,5,=F=D,.若D0,即74138的S0,74138译码,F-0, 与D状态相同。若Dl,即74138的5=,74138不译码,所有输出全为1,=,也与 D状态相同。可见,在A414=000时,F=D:AA0=001时,F=D::A2A40=111 时,F=D: 当E=1时,八选一数据选择器74151“不选择”、3线-8线译码器74138“不译码”、 三态缓冲器G输出为高阻态,将输入与输出隔离开,数据不能传输。 从上述分 新可见,74138在电路中起数据分配器的作用。74151和74138一起构成了八 路数据分时传输系统

时, S2 = F = D0 。若 D0=0,即 74138 的 S2 =0,74138 译码,F0=0, 与 D0 状态相同。若 D0=1,即 74138 的 S2 =1,74138 不译码,所有输出全为 1,F0=1,也与 D0 状态相同。可见,在 A2A1A0=000 时,F=D0;A2A1A0=001 时,F=D1;.;A2A1A0=111 时,F=D7; 当 E =1 时,八选一数据选择器 74151“不选择”、 3 线-8 线译码器 74138“不译码”、 三态缓冲器 G 输出为高阻态,将输入与输出隔离开,数据不能传输。 从上述分析可见,74138 在电路中起数据分配器的作用。74151 和 74138 一起构成了八 路数据分时传输系统

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学资源(自测题)第六章 时序逻辑电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第五章 触发器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第二章 逻辑门电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第三章 逻辑代数自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第一章 数值和码制自测题及答案.doc

- 《数字电子技术》课程教学资源(作业习题)第八章 AD和DA转换(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第九章 存储器(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第七章 时序逻辑电路(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第四章 触发器(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第六章 组合逻辑电路(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第五章 脉冲产生与整形(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第三章 TTL门电路(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第二章 逻辑代数基础(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第一章 数制与码制(含答案).doc

- 石河子大学:《数字电子技术》课程教学大纲 digital electronic technique foundation.doc

- 石河子大学:《数字电子技术》课程实验教学大纲.doc

- 石河子大学:《数字电子技术》课程设计大纲(电子技术课程设计 Course Project of Electronics).doc

- 石河子大学:《数字电子技术》课程授课教案(任课教师:任玲).doc

- 《信号与系统》课程教学课件(PPT讲稿)第十二章 系统的状态变量分析.ppt

- 《信号与系统》课程教学课件(PPT讲稿)幅度调制.ppt

- 《数字电子技术》课程教学资源(自测题)第七章 半导体存储器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第十章 脉冲产生和整形自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第十一章 AD和DA转换器自测题和答案.doc

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第1章 概述.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第2章 PLD硬件特性与编程技术.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第3章 VHDL基础.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第4章 Quartus II使用方法.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第5章 VHDL状态机.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第6章 16位CISC CPU设计.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第7章 VHDL语句.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第8章 VHDL结构.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第10章 DSP Builder设计深入.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第9章 DSP Builder设计初步.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第一章 初识数字电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第三章 逻辑门电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第二章 分析与设计数字电路的工具.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第五章 记忆单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第七章 脉冲单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第九章 数模与模数转换器.ppt