《数字电子技术》课程教学资源(自测题)第七章 半导体存储器自测题和答案

第八章习题 一、填空题 1、一个10位地址码、8位输出的ROM,其存储容量为或 2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的 ROM。该ROM有根地址线,有根数据读出线。 二、综合题 1、试写出图61所示阵列图的逻辑函数表达式和真值表,并说明其功能。 F。 F 图6-1例6-1逻辑图 2、试用256×4位的RAM扩展成1024×8位存储器。 3、下列RAM各有多少条地址线? )512×2位(2)1K×8位(3)2K×1位 (④16K×1位(⑤)256×4位(⑥)64K×1位 4、写出由ROM所实现的逻辑函数的表达式。 (8分)

第八章 习题 一、填空题 1、一个 10 位地址码、8 位输出的 ROM,其存储容量为 或 。 2、将一个包含有 32768 个基本存储单元的存储电路设计 16 位为一个字节的 ROM。该 ROM 有 根地址线,有 根数据读出线。 二、综合题 1、试写出图 6-1 所示阵列图的逻辑函数表达式和真值表,并说明其功能。 1 1 A B W0 W1 W2 W3 F0 F1 F2 F3 图6-1 例6-1逻辑图 2、试用 256×4 位的 RAM 扩展成 1024×8 位存储器。 3、下列 RAM 各有多少条地址线? ⑴ 512×2 位 ⑵ 1K×8 位 ⑶ 2K×1 位 ⑷ 16K×1 位 ⑸ 256×4 位 ⑹ 64K×1 位 4、写出由 ROM 所实现的逻辑函数的表达式。 (8 分) 1 1 1 A B C Y1 Y2

5、四片16×4RAM和逻辑门构成的电路如图6-7所示。试回答: A十 A房 16 图67多片RAM级联逻辑图 ()单片RAM的存储容量,扩展后的RAM总容量是多少? (2)图67所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? (3)当地址码为00010110时,RAM0RAM3,哪几片被选中? 6,用OM设计一个组合逻辑电路,用来产生下列一组逻辑函数。画出存储矩阵的点阵图 Y=7.B.C.D+A.B.C.D+4.B.C.D+A.B.C.D Y=A.B.C.D+A.B-C.D+A-B.C.D+A-B.C.D Y=4.B.D+B.C.D Y=B.D+B.D 7、画出实现下面双输出逻辑函数的PLD表示。 (A.B.C)=ABC+ABC+ABC f(A.B.C,D)=ABC D+ABCD+A BCD+ABC D 三、简答顺 1、可编程逻辑器件是如何进行分类的?

5、四片 16×4RAM 和逻辑门构成的电路如图 6-7 所示。试回答: A0 A1 A2A3 CS 16×4 RAM0 (I /O)×4 A0 A1 A2 A3 CS16×4 RAM1 (I /O)×4 A0 A1 A2 A3 CS 16×4 RAM2 (I /O)×4 A0 A1 A2A3 CS 16×4 RAM3 (I /O)×4 AB7 AB6 AB5 AB4 AB3 AB2 AB1 AB0 DB0 DB7 地 址 线 数 据 线 & & & 图6-7 多片RAM级联逻辑图 ⑴单片 RAM 的存储容量,扩展后的 RAM 总容量是多少? ⑵图 6-7 所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? ⑶当地址码为 00010110 时,RAM0~RAM3,哪几片被选中? 6.用 ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。画出存储矩阵的点阵图。 Y1 = A B C D + A BC D + A B C D + A BC D Y2 = A B C D + A BC D + A B C D + A BC D Y3 = A B D + B C D Y4 = B D + B D 7、画出实现下面双输出逻辑函数的 PLD 表示。 f A B C D A B C D ABCD A BCD ABC D f A B C A B C ABC ABC ( , , , ) ( , , ) 2 1 = + + + = + + 三、简答题 1、可编程逻辑器件是如何进行分类的?

2、GAL16V8的OLMC中4个数据选择器各有多少功能? 3、ROM和RAM有什么相同和不同之处?ROM写入信息有几种方式? 4、为什么用ROM可以实现逻辑函数式? 第八章习题答案 一、填空题 1、2138K 2、1116 一、综合题 1、解:根据与阵列的输出为B的最小项和阵列图中有实心点·为1,无·为0,可以写出 Fo=W,AB 表61 真伯表 F=W+W,+W=4B+AB+AB=A+B A B 而N F=AB+AB=A⊕B 00 0001 F=Wo+W+W,=4B+B+4B=4+B=AB 01 0111 10 0111 11 1100 值表如表6-1所示。 2、解: 片RAM不能满足存储容量需要时, 需要将若干片RAM组合起来,构成满足 的扩展分为位扩展和子打 用 就 实现位扩展的原则是: ①多个单片RAM的VO端并行输出,作为RAM的输出端一数据线或称位线。如两片 四位RAM的I/O端并行输出,得八位RAM: 对应接到 ④多个单片RA3M的R/而端接到一起,作为RAM的读/写控制端(RAM的R/而读写 控制端只能有 位的位数足够 现字扩展的原则是 ①多个单片RAM的1IVO端并接,作为RAM的IVO端(不需位扩展): ②多个单片RAM构成字扩展之后,每次访问只能选中一片,选中哪一片,由字扩展后 多出 线经 的译码器译码 接至 AM的端 一起,作为RAM的低位地址输入 ④多个单片RAM的R/W端接到一起,作为RAM的读/写控制端(RAM的R/W读写控制端 只能有一个) 1024×8位存储器需256X4位的芯片数 总存储容量 1024×8 C= 一片的存储容量256×41 8 个字航 译码器输入端,译码器的输出端对应接到2片256×4位RAM的C云端,连接方式如图6-3

2、GAL16V8 的 OLMC 中 4 个数据选择器各有多少功能? 3、ROM 和 RAM 有什么相同和不同之处?ROM 写入信息有几种方式? 4、为什么用 ROM 可以实现逻辑函数式? 第八章 习题答案 一、填空题 1、2 13 8K 2、11 16 二、综合题 1、解:根据与阵列的输出为 AB 的最小项和阵列图中有实心点·为 1,无·为 0,可以写出 F0 = W3 = AB F1 = W1 +W2 +W3 = AB + AB + AB = A + B F2 = AB + AB = A B F3 =W0 +W1 +W2 = AB + AB + AB = A + B = AB 从上述逻辑表达式可以看出,图 6-1 所示阵列图实现了输 入变量 A、B 的四种逻辑运算:与、或、异或和与非。列出真 值表如表 6-1 所示。 2、解:当一片 RAM 不能满足存储容量需要时,需要将若干片 RAM 组合起来,构成满足 存储容量要求的存储器。RAM 的扩展分为位扩展和字扩展两种。 如果一片 RAM 的字数满足要求,而位数不够时,应采用位扩展。字数满足要求,就是 地址线满足要求。只要将若干片 RAM 并接起来,所有芯片的位线加起来作为扩展后的位线, 便可以实现位扩展。 实现位扩展的原则是: ①多个单片 RAM 的 I/O 端并行输出,作为 RAM 的输出端—数据线或称位线。如两片 四位 RAM 的 I/O 端并行输出,得八位 RAM; ②多个单片 RAM 的 CS 端接到一起,作为 RAM 的片选端(多片 RAM 同时被选中); ③多个单片 RAM 的地址端对应接到一起,作为 RAM 的地址输入端。 ④多个单片 RA3M 的 R/W 端接到一起,作为 RAM 的读/写控制端(RAM 的 R/W 读写 控制端只能有一个); 在 RAM 的数据位的位数足够,而字数达不到要求时,需要进行字扩展。字数增加,地 址线数就得相应增加。如 256×8 位 RAM 的地址线数为 8 条,而 1024×8 位 RAM 的地址 线数为 10 条。 实现字扩展的原则是: ①多个单片 RAM 的 I/O 端并接,作为 RAM 的 I/O 端(不需位扩展); ②多个单片 RAM 构成字扩展之后,每次访问只能选中一片,选中哪一片,由字扩展后 多出的地址线决定。多出的地址线经输出低有效的译码器译码,接至各片 RAM 的 CS 端; ③多个单片 RAM 的地址端对应接到一起,作为 RAM 的低位地址输入端。 ④多个单片 RAM 的 R/W 端接到一起,作为 RAM 的读/写控制端(RAM 的 R/W 读写控制端 只能有一个); 1024×8 位存储器需 256×4 位的芯片数 8 256 4 1024 8 = = = 一片的存储容量 总存储容量 C 两片 256×4 位的 RAM 并联实现位扩展,达到 8 位的要求。根据 2 n=字数,求得 1024 个字的地址线数 n=10,256 字的存储器只有 8 条地址线,多余的两条地址线 A9A8 需要接 2-4 译码器输入端,译码器的输出端对应接到 2 片 256×4 位 RAM 的 CS 端,连接方式如图 6-3 A B F0 F1 F2 F3 0 0 0 0 0 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 1 0 0 表 6-1 真值表

所示。 译码器 ☐AA A Ao CSa 2564日 1025640 6x40 线A 数 线D, 图6-3256×4位RAM扩展成1024×8位存储器 3、解 )512×2位:512=2°,故有9个地址输入端。 (2)1Kx8位:1K=1024=210,故有10个地址输入岩」 (3)2K×1位:2K=2048=2",故有11个地址输入端。 (④)16K×1位:16K=24,故有14个地址输入端。 (⑤)256×4位:256=28,故有8个地址输入端。 (6)64K×1位:64K=216,故有16个地址输入瑞 4、Y=ABC+BC+ABC+ABC Y:=ABC ABC+ABC 5、解: )单片RAM的容量是16x4-64个存储单元,扩展后的RAM总容量为2xg256个存 储单元。 (②)图67所示电路为位、字都有的扩展。 (3)当地址码为0O010110时,RAM0-RAMB中的RAM2和RAMB片选端有效,因此被 +小B:CD+4B:C:D+成+形+那 Y A.B.C.D+4.B.C.D+A.B.C.D+A.B.C.D=W,+W+ws+Wis Y=A.B.D+B.C.D=A.B-C.D+4.B.C.D+4.B.C.D+4.B.C.D =W。+W4+W。+W2 Y B.D+BD=A.B.D+4.B.D+A-B.D+4.B.D =A.B.C.D+A-B.C.D+7.B.C.D+A.B.C.D+A.B.C.D+A.B.C.D +A.B.C.D+A.B.C.D =W,+W,、+W,+W。+W。+W。+W。+W 由此画出实现上述逻辑函数的逻辑图如图68所示

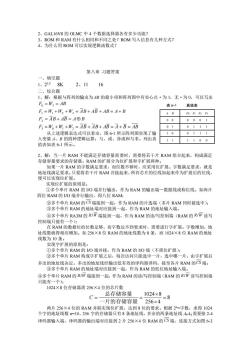

所示。 1 A0 CS8 8 A7 I/O 1 A0 CS6 6 A7 I/O 1 A0 CS4 4 A I/O 1 A0 CS2 2 256×4A7 I/O A0 CS1 1 A7 I/O A0 CS3 3 A7 I/O A0 CS5 5 A7 I/O A0 CS7 7 A7 I/O 译 码 器 A 9 A 8 A9A8 A9A8 A9A8 A9 A8 A0 A7 D0 D7 地 址 总 线 数 据 总 线 256×4 256×4 256×4 256×4 256×4 256×4 256×4 图6-3 256×4 位RAM扩展成1024×8位存储器 3、解: ⑴ 512×2 位:512=29,故有 9 个地址输入端。 ⑵ 1K×8 位:1K=1024=210,故有 10 个地址输入端。 ⑶ 2K×1 位:2K=2048=211,故有 11 个地址输入端。 ⑷ 16K×1 位:16K=214,故有 14 个地址输入端。 ⑸ 256×4 位:256=28,故有 8 个地址输入端。 ⑹ 64K×1 位:64K=216,故有 16 个地址输入端。 4、 5、解: ⑴ 单片 RAM 的容量是 16×4=64 个存储单元,扩展后的 RAM 总容量为 2 5×8=256 个存 储单元。 ⑵ 图 6-7 所示电路为位、字都有的扩展。 ⑶ 当地址码为 00010110 时,RAM0~RAM3 中的 RAM2 和 RAM3 片选端有效,因此被 选中。 6、解:由题中给定的逻辑函数知 Y1 A B C D A B C D A B C D A B C D = W0 +W5 +W1 0 +W1 5 = + + + Y2 A B C D A B C D A B C D A B C D = W2 +W7 +W8 +W1 3 = + + + 6 4 1 0 2 3 W W W W Y A B D B C D A B C D A B C D A B C D A B C D = + + + = + = + + + 1 5 1 3 7 5 1 0 8 2 0 4 W W W W W W W W A B C D A B C D A B C D A B C D A B C D A B C D A B C D A B C D Y B D BD A B D A B D A B D A B D = + + + + + + + + + = + + + + + = + = + + + 由此画出实现上述逻辑函数的逻辑图如图 6-8 所示。 Y1 = ABC + BC + ABC + ABC Y2 = ABC + ABC + ABC

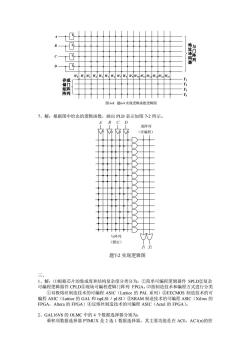

A B C-H 图6-8题69实现逻辑函数亚辑图 7、解:根据图中给出的逻辑函数,画出PLD表示如图7-2所示。 或阵列 题7-2实现逻辑图 芯片 D双极缩丝 造技术的可缩程A PAL系G EECMOS制造技 编程ASI aA制造技术的可编程 FPGA,Altera的FPGA)④反熔丝制造技术的可编程ASIC(Acd的FPGA。 2、GAL16V8的OLMC中的4个数据选择器分别为: 乘积项数据选择器PTMUX是2选1数据选择器,其主要功能是在ACO,ACI()的控

W0 W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12 W13 W14 W15 A B C D 与 门 阵 列 地 址 译 码 器 或 门 阵 列 存 储 矩 阵 Y1 Y2 Y3 Y4 1 1 1 1 图 6-8 题6-9 实现逻辑函数逻辑图 7、解:根据图中给出的逻辑函数,画出 PLD 表示如图 7-2 所示。 × × × × f1 f 2 A B C 或阵列 (可编程) 与阵列 (固定) × D × × 题7-2 实现逻辑图 三、 1、解:⑴根据芯片的集成度和结构复杂度分类分为:①简单可编程逻辑器件 SPLD②复杂 可编程逻辑器件 CPLD③现场可编程逻辑门阵列 FPGA。⑵按制造技术和编程方式进行分类 ①双极熔丝制造技术的可编程 ASIC(Lattice 的 PAL 系列)②EECMOS 制造技术的可 编程 ASIC(Lattice 的 GAL 和 ispLSI / pLSI)③SRAM 制造技术的可编程 ASIC(Xilinx 的 FPGA,Altera 的 FPGA)④反熔丝制造技术的可编程 ASIC(Actel 的 FPGA)。 2、GAL16V8 的 OLMC 中的 4 个数据选择器分别为: 乘积项数据选择器 PTMUX 是 2 选 1 数据选择器,其主要功能是在 AC0,AC1(n)的控

制下,用来决定第一与项是否成为或门的输入 输出多路开关OMUX是2选1数据选择器,OMUX的作用是在AC0和ACI()的控制 下,决定输出是组合电路还 选1数据选择器。它用来从Vcc、地电平、OE、第一与项 四路信号中选出一路信号作为输出三态缓冲器的三态控制信号。 器的瑞、本级输出、邻级 3、ROM和RAM都是存储器,可以用来写入二进制信总。不同之处是ROM写入之后不能 擦除(只能通过特殊方法擦除:RAM可以随机存取信息。ROM写入信息有以下几种方式: 固定ROM由厂家写入:可编程ROM由用户将熔丝通过大电流写入信息:可擦可编程ROM 可以多次写入和擦除信息,但需要经过专门的编程器,实现光和电擦除等。 4、ROM的存储矩阵由与阵列和或阵列组成。与阵列的输入为地址码,输出为地址译码器的 输出,包含了全部输入变量的最小项。或阵列的输出(数据输出)为最小项之和。这样,用 具有2”个译码输出和m位数据输出的ROM,可以得到一组最多为m个输出的n个变量的 罗辑函数

制下,用来决定第一与项是否成为或门的输入。 输出多路开关 OMUX 是 2 选 1 数据选择器,OMUX 的作用是在 AC0 和 AC1(n)的控制 下,决定输出是组合电路还是时序电路。 三态多路开关 TSMUX 是 4 选 1 数据选择器。它用来从 VCC、地电平、OE、第一与项 四路信号中选出一路信号作为输出三态缓冲器的三态控制信号。 反馈多路开关 FMUX 是 4 选 1 数据选择器。它用来从触发器的 Q 端、本级输出、邻级 输出、地电平这四路信号中选出一路作为反馈信号,反馈到与阵列。 3、ROM 和 RAM 都是存储器,可以用来写入二进制信息。不同之处是 ROM 写入之后不能 擦除(只能通过特殊方法擦除);RAM 可以随机存取信息。ROM 写入信息有以下几种方式: 固定 ROM 由厂家写入;可编程 ROM 由用户将熔丝通过大电流写入信息;可擦可编程 ROM 可以多次写入和擦除信息,但需要经过专门的编程器,实现光和电擦除等。 4、ROM 的存储矩阵由与阵列和或阵列组成。与阵列的输入为地址码,输出为地址译码器的 输出,包含了全部输入变量的最小项。或阵列的输出(数据输出)为最小项之和。这样,用 具有 2 n 个译码输出和 m 位数据输出的 ROM,可以得到一组最多为 m 个输出的 n 个变量的 逻辑函数

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学资源(自测题)第四章 组合逻辑电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第六章 时序逻辑电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第五章 触发器自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第二章 逻辑门电路自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第三章 逻辑代数自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第一章 数值和码制自测题及答案.doc

- 《数字电子技术》课程教学资源(作业习题)第八章 AD和DA转换(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第九章 存储器(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第七章 时序逻辑电路(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第四章 触发器(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第六章 组合逻辑电路(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第五章 脉冲产生与整形(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第三章 TTL门电路(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第二章 逻辑代数基础(含答案).doc

- 《数字电子技术》课程教学资源(作业习题)第一章 数制与码制(含答案).doc

- 石河子大学:《数字电子技术》课程教学大纲 digital electronic technique foundation.doc

- 石河子大学:《数字电子技术》课程实验教学大纲.doc

- 石河子大学:《数字电子技术》课程设计大纲(电子技术课程设计 Course Project of Electronics).doc

- 石河子大学:《数字电子技术》课程授课教案(任课教师:任玲).doc

- 《信号与系统》课程教学课件(PPT讲稿)第十二章 系统的状态变量分析.ppt

- 《数字电子技术》课程教学资源(自测题)第十章 脉冲产生和整形自测题和答案.doc

- 《数字电子技术》课程教学资源(自测题)第十一章 AD和DA转换器自测题和答案.doc

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第1章 概述.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第2章 PLD硬件特性与编程技术.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第3章 VHDL基础.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第4章 Quartus II使用方法.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第5章 VHDL状态机.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第6章 16位CISC CPU设计.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第7章 VHDL语句.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第8章 VHDL结构.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第10章 DSP Builder设计深入.ppt

- 《数字电子技术》课程PPT教学课件(EDA技术与VHDL)第9章 DSP Builder设计初步.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第一章 初识数字电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第三章 逻辑门电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第二章 分析与设计数字电路的工具.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第五章 记忆单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第七章 脉冲单元电路.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第九章 数模与模数转换器.ppt

- 石河子大学:《数字电子技术》课程教学资源(PPT课件)第八章 半导体存储器.ppt