《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH53 寄存器和读写存储器

5.3寄存器和读/写存储器 (Register and Random Access Memory) 5.3.1寄存器的主要特点和分类 一、概念和特点 1.概念 寄存:把二进制数据或代码暂时存储起来。 并行 寄存器:具有寄存功能的电路。101 .0输出 2.特点 串行 081 主要由触发 翰入1 器构成,一般不 FFo FF1.FFn-1 串行 对存储内容进 控制信号 输出 行处理。 10 1.。0 并行

5.3 寄存器和读/写存储器 (Register and Random Access Memory) 5.3.1 寄存器的主要特点和分类 一、 概念和特点 1. 概念 寄存:把二进制数据或代码暂时存储起来。 寄存器:具有寄存功能的电路。 2. 特点 主要由触发 器构成,一般不 对存储内容进 行处理。 并行 输入 并行 输出 FF0 FF1 FFn–1 D0 D1 Dn–1 Q0 Q1 Qn–1 控制信号 1 0 1 . 0 1 0 1 . 0 01 01 串行 输入 串行 输出

I 二、分类 基本寄存器 (并入并出) 1.按功能分 移位寄存器(并入并出、并入串出、 串入并出、串入串出) 2.按开关元件分 多位D型触发器 基本寄存器 锁存器 寄存器阵列 TTL寄存器 单向移位寄存器 移位寄存器 双向移位寄存器 CMOS寄存器 基本寄存器 (多位D型触发器 移位寄存器 (同TTL)

二、 分类 1. 按功能分 基本寄存器 移位寄存器 (并入并出) (并入并出、并入串出、 串入并出、串入串出) 2. 按开关元件分 TTL 寄存器 CMOS 寄存器 基本寄存器 移位寄存器 多位 D 型触发器 锁存器 寄存器阵列 单向移位寄存器 双向移位寄存器 基本寄存器 移位寄存器 (多位 D 型触发器) (同 TTL)

5.3.2基本寄存器 一个触发器可以存储1位二进制信号;寄存n位 二进制数码,需要n个触发器。 -、4边沿D触发器(74175、74LS175) do d h d 21_ 1 3 9FF38 Rp 1D D CP 特点: 保持 并入并出,结构简单,抗干扰能力强

5.3.2 基本寄存器 一个触发器可以存储 位二进制信号;寄存 n 位 二进制数码,需要 个触发器。 1 n 一、4 边沿 D 触发器 (74175、74LS175) C1 1D D0 Q0 Q0 RD C1 1D D1 Q1 Q1 C1 1D D2 Q2 Q2 C1 1D D3 Q3 Q3 RD RD RD FF0 FF1 FF2 FF3 1 1 CP CR 异步清零 0 0 0 0 0 同步送数 1 d0 d1 d2 d3 保 持 特点: 并入并出,结构简单,抗干扰能力强

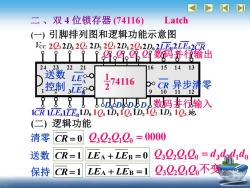

I 二、双4位锁存器(74116) Latch (一)引脚排列图和逻辑功能示意图 6c2Q2D32022D22012D1202D2E2LE2灭 1??「991公数码著荷输出 24 23 2221 16151413 送数 控制 3LE8O 74I6 bCR异步清零 9101 1112 。dD0DD5D6数妈考行输入 ICR 1LEAILER1Do 1201D11O 1D2IO 1Ds 10s (二) 逻辑功能 清零 CR=0 2322212=0000 送数 CR=1 LEA+LEB=0 0322020=l34241d0 保持 CR=1 LEA+LEB=1O322212不变

二 、双 4 位锁存器 (74116) Latch (一) 引脚排列图和逻辑功能示意图 74116 Q0 Q1 Q2 Q3 CR LEA D0 D1 D2 D3 LEB 2 1 异步清零 送数 控制 数码并行输入 数码并行输出 (二) 逻辑功能 清零 CR = 0 送数 Q3 Q2 Q1 Q0 = 0000 CR= 1 LEA + LEB = 0 Q3 Q2 Q1 Q0 = d3 d2 d1 d0 保持 CR= 1 LEA + LEB = 1 Q3 Q2 Q1 Q0 不变

I 三、4×4寄存器阵列(74170、74LS170) (一)引脚排列图和逻辑功能示意图 数码输出 Vcc Do Awo AwI ENwENR 2o2 00012203 999 988 161514131211109 74170 Awoo 74170 12345 67 8 ENwoO ENR D1D2D3AR1AR0Q322地 Do D D2 D3 并行数码输入 AW0、AwI一写入地址码 ENv一写入时钟脉冲 ARO、AR1一读出地址码 ENR 一读出时钟脉冲

三、 4 4 寄存器阵列 (74170、74LS170) (一) 引脚排列图和逻辑功能示意图 74170 Q0 Q1 Q2 Q3 ENR D0 D1 D2 D3 ENW AW0 AW1 AR0 AR1 并行数码输入 数 码 输 出 AW0、AW1 — 写入地址码 AR0、AR1 — 读出地址码 ENW — 写入时钟脉冲 ENR — 读出时钟脉冲 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 74170 VCC D0 AW0 AW1 ENWENR Q0 Q1 D1 D2 D3 AR1 AR0 Q3 Q2 地

☒-D冈I (二)逻辑功能 镜行籁wq构旅海阵 220~223Q30~03 0 0 0 X4wr 0 0 0 × XAwo 0 × 0 0 1 ENw 0 0 0 ENR 1 FF30 FF31 FF32 F FF3 特点:能同时进行读写;集电极开路输出

(二) 逻辑功能 16能存放个D锁存器 4个字: W构成存储矩阵 0、W1、W2、W3 Q0 Q1 Q2 Q3 ENR D0 D1 D2 D3 ENW AW0 AW1 AR0 AR1 FF00 FF01 FF02 FF0 3 FF10 FF11 FF12 FF1 3 FF20 FF21 FF22 FF2 3 FF30 FF31 FF32 FF3 3 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 0 1 0 1 0 0 1 0 0 0 1 0 0 1 1 0 0 0 1 0 0 0 1 × × 写 入 禁 止 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 0 0 1 1 0 0 0 1 × × 1 1 1 1 特点: 能同时进行读写; 集电极开路输出 每个字有4位: ' 33 ' 30 ' 23 ' 20 ' 13 ' 10 ' 03 ' 00 ~ ~ ~ ~ Q Q Q Q Q Q Q Q 、

5.3.3移位寄存器 一、单向移位寄存器 右移寄存器 FFo FF2 FF3 D C1 1 时钟方程 ( P=CP=CP2=CP=CP 驱动方程D=DD=Q、D2=外、D3=Q2 状态方程 21=D,211=26,22+1=2”,Q=

5.3.3 移位寄存器 一、单向移位寄存器 右移寄存器 Q0 Q1 Q2 Q3 C1 1D FF0 CP C1 1D FF1 C1 1D FF2 C1 1D FF3 时钟方程 CP0 = CP1 = CP2 = CP3 = CP 驱动方程 n n n D0 = Di 、D1 = Q0 、D2 = Q1 、D3 = Q2 状态方程 n n n n n n i n Q D Q Q Q Q Q Q2 1 1 3 1 0 2 1 1 1 0 = , = , = , = + + + + Di 0 0 0 0 00001011 1 0 0 0 0000011 1 1 0 0 000001 0 1 1 0 00001 1 0 1 1 0000 0 1 0 000 0 1 0 00 0 0 0 1 0 0 0 0 0

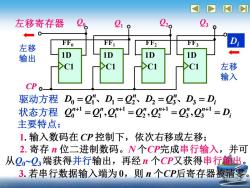

左移寄存器 10 02o 03 ←0 左移 FFo FF3 输出 >C1 左移 输入 CP 驱动方程D=2”、D1=2数、D2=Q、D3=D 状态方程21=2,21=2,21=2,21=D 主要特点: 1.输入数码在CP控制下,依次右移或左移; 2.寄存n位二进制数码。N个CP完成串行输入,并可 从Qo~Q3端获得并行输出,再经n个CP又获得串行输出。 3.若串行数据输入端为0,则n个CP后寄存器被清零

左移寄存器 Di 左移 输入 左移 输出 驱动方程 i n n n D0 = Q1 、D1 = Q2 、D2 = Q3 、D3 = D 状态方程 i n n n n n n n Q = Q Q = Q Q = Q Q = D + + + +1 3 3 1 2 2 1 1 1 1 0 , , , 主要特点: 1. 输入数码在 CP 控制下,依次右移或左移; 2. 寄存 n 位二进制数码。N 个CP完成串行输入,并可 从Q0Q3 端获得并行输出,再经n 个CP又获得串行输出。 3. 若串行数据输入端为 0,则 n 个CP后寄存器被清零。 Q3 CP Q0 Q1 Q2 C1 1D FF0 C1 1D FF1 C1 1D FF2 C1 1D FF3

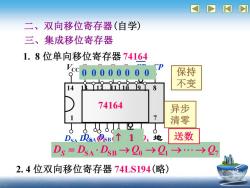

I 二、双向移位寄存器(自学) 三、集成移位寄存器 1.8位单向移位寄存器74164 Vcc CP 00000000 保持 14 8 不变 74164 异步 1 清零 DAD2ADsB↑1 )3地 送数 Ds=DsA·DsB→O→O 2.4位双向移位寄存器74LS194(略)

二、双向移位寄存器(自学) 三、集成移位寄存器 1. 8 位单向移位寄存器 74164 DSA DSB Q0 Q1 Q2 Q3 地 1 2 3 4 5 6 7 14 13 12 11 10 9 8 74164 VCC Q7 Q6 Q5 Q4 CR CP 74164 Q7Q6Q5Q4Q3Q2Q1Q0 DSA DSB CP CR 异步 清零 0 0 0 0 0 0 0 0 保持 不变 0 1 2. 4 位双向移位寄存器 74LS194(略) 1 DS DS A DS B Q0 Q1 → Q7 = → → → 送数

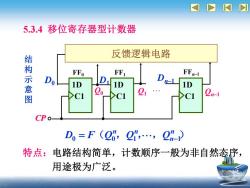

5.3.4移位寄存器型计数器 反馈逻辑电路 结构示意图 FFo FF FFn-1 Do 1D C 2m-1 CPo D=F(2,2,.,2% 特点:电路结构简单,计数顺序一般为非自然态序, 用途极为广泛

5.3.4 移位寄存器型计数器 结 构 示 意 图 C1 Q0 Q1 Qn–1 1D FF0 CP C1 1D FF1 C1 1D FFn–1 反馈逻辑电路 D Dn–1 0 D1 . D0 = F(Q0 n ,Q1 n ,,Qn n −1 ) 特点:电路结构简单,计数顺序一般为非自然态序, 用途极为广泛

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH52 计数器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH51 时序电路的基本分析和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH50 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 SUM4 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH45 触发器的VHDL描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH44 触发器的电气特性.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH43 边沿触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH42 同步触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH41 基本触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第四章 触发器 CH40 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 SUM3 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH38 组合逻辑电路的 VHDL 描述及其仿真.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH37 组合电路中的竞争冒险.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH36 只读存储器(ROM).ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH35 用MSI实现组合逻辑函数.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH34 数据选择器和分配器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH33 编码器和译码器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH32 加法器和数值比较器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH31 组合电路的分析方法和设计方法.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第三章 组合逻辑电路 CH30 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH54 顺序脉冲发生器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 CH55 时序逻辑电路.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第五章 时序逻辑电路 SUM5 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH60 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH61 施密特触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH62 单稳态触发器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 CH63 多谐振荡器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第六章 脉冲产生与整形电路 SUM6 小结.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH70 概述.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH71 D/A转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 CH72 A/D转换器.ppt

- 《数字电子技术》课程教学课件(PPT讲稿)第七章 数模与模数转换电路 SUM7 小结.ppt

- 西安邮电大学:《现代通信网》课程教学大纲 Modern Communication Network C.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第一章 绪论.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第二章 传送网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第三章 数据链路层.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第五章 同步网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第六章 电话网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第四章 No.7信令网.doc

- 西安邮电大学:《现代通信网》课程授课教案(讲稿)第八章 分组网.doc