《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2)

第五讲行为建模 西安邮电学院通信工程系 第五讲行为建模1 内容: 行为建模 。过程块语句 ?过程赋值 冬过程中的块语句 过程的时序控制 冬阻塞与非阻塞过程赋值 ”条件语句

第五讲 行为建模 西安邮电学院通信工程系 第 五讲 行为建模1 内容: ❖ 行为建模 ❖ 过程块语句 ❖ 过程赋值 ❖ 过程中的块语句 ❖ 过程的时序控制 ❖ 阻塞与非阻塞过程赋值 ❖ 条件语句

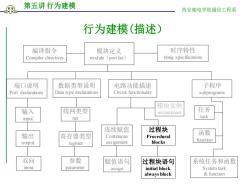

第五讲行为建模 西安邮电学院通信工程系 行为建模(描述) 编译指令 模块定义 时序特性 Compiler directives module (port list) timig specifications 端口说明 数据类型说明 电路功能描述 子程序 Port declarations Data type declarations Circuit functionality subprograms 模块实例 输入 线网类型 任务 instantiation input net task 连续赋值 过程块 输出 寄存器类型 函数 Continuous Procedural function output register assignment blocks 双向 参数 赋值语句 过程块语句 系统任务和函数 inout parameter assign initial block System task always block function

第五讲 行为建模 西安邮电学院通信工程系 行为建模(描述) 模块定义 module(port list) 时序特性 timig specifications 端口说明 Port declarations 输入 input 双向 inout 输出 output 数据类型说明 Data type declarations 线网类型 net 参数 parameter 寄存器类型 register 电路功能描述 Circuit functionality 子程序 subprograms 任务 task 函数 function 系统任务和函数 System task & function 编译指令 Compiler directives 连续赋值 Continuous assignment 赋值语句 assign 过程块 Procedural blocks 过程块语句 initial block always block 模块实例 instantiation

第五讲行为建模 西安邮电学院通信工程系 行为建模(描述) 行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系统的功能 而不是实现。 Verilog?有高级编程语言结构用于行为描述,包括:initial,always,@,wait, for,while,if else,case和forever等。 Veri1og的行为建模是用一系列以高级编程语言编写的并行的、动态的过程块来描 述系统的工作。 CIr D触发器行为 在每一个时钟上升沿, 若C1r不是低电平, 置Q为D值, Data 置Qb为D值的反 DFF Qb 无论何时C1r变低 置Q为0, Clk 置Qb为1

第五讲 行为建模 西安邮电学院通信工程系 行为建模(描述) ❖ 行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系统的功能 而不是实现。 ❖ Verilog有高级编程语言结构用于行为描述,包括:initial, always,@, wait, for, while, if else, case 和 forever 等。 ❖ Verilog的行为建模是用一系列以高级编程语言编写的并行的、动态的过程块来描 述系统的工作。 在每一个时钟上升沿, 若Clr不是低电平, 置Q为D值, 置Qb为D值的反 D触发器行为 无论何时Clr变低 置Q为0, 置Qb为1

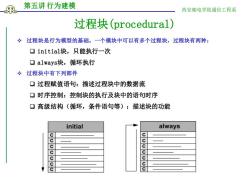

第五讲行为建模 西安邮电学院通信工程系 过程块(procedural) 过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种: ▣initial:块,只能执行一次 ▣always:块,循环执行 过程块中有下列部件 口过程赋值语句:描述过程块中的数据流 口时序控制:控制块的执行及块中的语句时序 口高级结构(循环,条件语句等):描述块的功能 initial always

第五讲 行为建模 西安邮电学院通信工程系 过程块(procedural) ❖ 过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种: ❑ initial块,只能执行一次 ❑ always块,循环执行 ❖ 过程块中有下列部件 ❑ 过程赋值语句:描述过程块中的数据流 ❑ 时序控制:控制块的执行及块中的语句时序 ❑ 高级结构(循环,条件语句等):描述块的功能

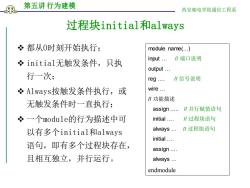

第五讲行为建模 000H 西安邮电学院通信工程系 过程块initial和always 冬都从0时刻开始执行; module name(.) input. ∥端口说明 initial无触发条件,只执 output . 行一次: reg . ∥信号说明 Always按触发条件执行,或 wire. ∥功能描述 无触发条件时一直执行; assign.∥并行赋值语句 冬一个module的行为描述中可 initial. ∥过程块语句 以有多个initial和always always.∥过程块语句 initial. 语句,即有多个过程块存在, assign. 且相互独立,并行运行。 always. endmodule

第五讲 行为建模 西安邮电学院通信工程系 过程块initial和always ❖ 都从0时刻开始执行; ❖ initial无触发条件,只执 行一次; ❖ Always按触发条件执行,或 无触发条件时一直执行; ❖ 一个module的行为描述中可 以有多个initial和always 语句,即有多个过程块存在, 且相互独立,并行运行。 module name(.) input . // 端口说明 output . reg . // 信号说明 wire . // 功能描述 assign . // 并行赋值语句 initial . // 过程块语句 always . // 过程块语句 initial . assign . always . endmodule

第五讲行为建模 西安邮电学院通信工程系 过程赋值(procedural assignment). 冬 在过程块中的赋值称为过程赋值。 在过程赋值语句中表达式左边的信号必须是寄存器类型(如reg类型) 在过程赋值语句等式右边可以是任何有效的表达式,数据类型也没有限制。 如果一个信号没有声明则缺省为wire类型。使用过程赋值语句给wire赋值会产生错 误。 module adder (out,a,b,cin), input a,b,cin; 时序控制 output [1:0]out wire a,b,cin; reg half sum; reg [1:0]out; always @a or b or cin) 顺序块语句 begin half sum a^b^cin ;/OK half carry a b I a !b cin I !a b cin /7 ERRORI out (half_carry,hahlfsumiry end 没有说明 endmodule

第五讲 行为建模 西安邮电学院通信工程系 过程赋值(procedural assignment) ❖ 在过程块中的赋值称为过程赋值。 ❖ 在过程赋值语句中表达式左边的信号必须是寄存器类型(如reg类型) ❖ 在过程赋值语句等式右边可以是任何有效的表达式,数据类型也没有限制。 ❖ 如果一个信号没有声明则缺省为wire类型。使用过程赋值语句给wire赋值会产生错 误。 module adder (out, a, b, cin); input a, b, cin; output [1:0] out; wire a, b, cin; reg half_sum; reg [1: 0] out; always @( a or b or cin) begin half_sum = a ^ b ^ cin ; // OK half_carry = a & b | a & !b & cin | !a & b & cin ; // ERROR! out = {half_carry, half_ sum} ; end endmodule half_carry 没有说明 时序控制 顺序块语句

第五讲行为建模 西安邮电学院通信工程系 过程中的块语句 冬块语句用来将多个语句组织在一起,使得他们在语法上如同一个语句。块 语句分为两类。 顺序块:语句置于关键字begin和end之间,块中的语句以顺序方式执行。 并行块:关键字fork和join之间的是并行块语句,块中的语句并行执行。 必 Fork和join语句常用于testbench描述。这是因为可以一起给出矢量及其 绝对时间,而不必描述所有先前事件的时间。 always always initial initial begin fork begin fork end join end join

第五讲 行为建模 西安邮电学院通信工程系 过程中的块语句 ❖ 块语句用来将多个语句组织在一起,使得他们在语法上如同一个语句。块 语句分为两类。 ❖ 顺序块:语句置于关键字begin和end之间,块中的语句以顺序方式执行。 ❖ 并行块:关键字fork和join之间的是并行块语句,块中的语句并行执行。 ❖ Fork和join语句常用于testbench描述。这是因为可以一起给出矢量及其 绝对时间,而不必描述所有先前事件的时间

第五讲行为建模 西安邮电学院通信工程系 有名块 有名块的块名作用: ?便于实现对块语句的有效控制 格式: 口用disable语句终止或提前结束有名块的执行过 begin:块名 程 ?允许在块内引入局部变量 ▣只在块内起作用的变量 end 口变量名可以和块外的其他变量名相同 或 口一定是寄存器类 ▣例:begin: SEQ BLK fork:块名 reg[3:0] sat sat mask data; Join ff =sat; end

第五讲 行为建模 西安邮电学院通信工程系 有名块 格式: begin: 块名 . end 或 fork:块名 . join 有名块的块名作用: ❖ 便于实现对块语句的有效控制 ❑ 用disable语句终止或提前结束有名块的执行过 程 ❖ 允许在块内引入局部变量 ❑ 只在块内起作用的变量 ❑ 变量名可以和块外的其他变量名相同 ❑ 一定是寄存器类 ❑ 例: begin: SEQ_BLK reg[3:0] sat sat = mask & data; ff = ^sat; end

第五讲行为建模 西安邮电学院通信工程系 过程的时序控制 在过程块中可以说明过程时序。过程时序控制有三类: 延时执行:#delay, 延迟指定时间步后执行语句 边沿敏感事件的时序控制:@() 口在信号发生翻转后执行语句。 口可以说明信号有效沿是上升沿(posedge)还是下降沿 (negedge). 口可以用关键字or指定多个参数。 电平敏感事件的时序控制:wait() 口直至expr值为真时(非零)才执行语句。 口若expr已经为真则立即执行语句

第五讲 行为建模 西安邮电学院通信工程系 过程的时序控制 在过程块中可以说明过程时序。过程时序控制有三类: ❖ 延时执行:#delay, 延迟指定时间步后执行语句 ❖ 边沿敏感事件的时序控制:@() ❑ 在信号发生翻转后执行语句。 ❑ 可以说明信号有效沿是上升沿(posedge)还是下降沿 (negedge)。 ❑ 可以用关键字or指定多个参数。 ❖ 电平敏感事件的时序控制:wait() ❑ 直至expr值为真时(非零)才执行语句。 ❑ 若expr已经为真则立即执行语句

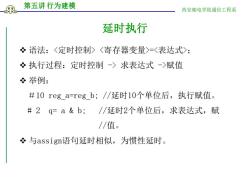

第五讲行为建模 西安邮电学院通信工程系 延时执行 语法:〈寄存器变量>=; 执行过程:定时控制->求表达式->赋值 举例: #l0rega=regb;/延时10个单位后,执行赋值。 #2q=a&b; //延时2个单位后,求表达式,赋 /值。 冬与assign语句延时相似,为惯性延时

第五讲 行为建模 西安邮电学院通信工程系 延时执行 ❖ 语法: =; ❖ 执行过程:定时控制 -> 求表达式 ->赋值 ❖ 举例: #10 reg_a=reg_b; //延时10个单位后,执行赋值。 # 2 q= a & b; //延时2个单位后,求表达式,赋 //值。 ❖ 与assign语句延时相似,为惯性延时

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第04讲 数据流建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第03讲 门级与结构建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第02讲 Verilog HDL语言基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第01讲 HDL语言概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(3/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(2/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(1/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 5Digital Transmission Through Bandlimited Channels.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multidimensional Signals).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multiamplitude Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Binary Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Pulse Amplitude Modulation、Pulse Code Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Preview、Measure of Information、Quantization).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Transmitters and Receivers.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Frequency Modulation、Phase Modulation).ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 7 Spread Spectrum Communication Systems.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(SSB – AM).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Conventional AM).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(AM,Amplitude Modulation).ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 1 Basic Matlab.doc

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt