《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2)

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 第三讲数字系统设计的基础知识2 本讲内容: 组合逻辑设计基础 冬时序逻辑设计基础 冬有限状态机设计 冬基于P的设计 本讲要点和实验要求

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 第三讲 数字系统设计的基础知识2 本讲内容: ❖ 组合逻辑设计基础 ❖ 时序逻辑设计基础 ❖ 有限状态机设计 ❖ 基于IP的设计 ❖ 本讲要点和实验要求

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 组合逻辑设计基础 在数字逻辑系统的设计中,从电路结构来看,基本 上可分为组合逻辑电路和时序逻辑电路两大类。 1.组合逻辑电路 冬组合逻辑电路的输出只与当时的输入信号有关,而与电 路过去的状态无关,也即它的输出完全由输入信号和输 出函数决定。 冬在手工设计电路时期,组合逻辑主要设计优化工具是卡 若图,在目前EDA时期则是综合工具软件;设计者只需 正确描述电路功能,具体电路的优化由综合工具完成。 最常用的组合逻辑电路有编码器、译码器、数据选择器、 加法器和相等比较器等

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 组合逻辑设计基础 在数字逻辑系统的设计中,从电路结构来看, 基本 上可分为组合逻辑电路和时序逻辑电路两大类。 1. 组合逻辑电路 ❖ 组合逻辑电路的输出只与当时的输入信号有关, 而与电 路过去的状态无关, 也即它的输出完全由输入信号和输 出函数决定。 ❖ 在手工设计电路时期,组合逻辑主要设计优化工具是卡 若图,在目前EDA时期则是综合工具软件;设计者只需 正确描述电路功能,具体电路的优化由综合工具完成。 ❖ 最常用的组合逻辑电路有编码器、 译码器、 数据选择器、 加法器和相等比较器等

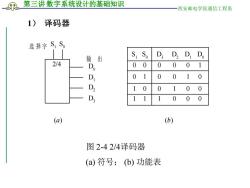

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 1)译码器 选择字S,S。 输 出 S:So D3D2DD。 2/4 D 0 0 0 001 01 0 0 10 10 0 100 D. 11 1 0 00 (a) (b) 图2-42/4译码器 (a)符号;(b)功能表

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-4 2/4译码器 (a) 符号; (b) 功能表 S1 S 选 择 字 0 输 出 D0 D1 D2 D3 (a) S1 S0 0 0 0 1 1 0 1 1 2/4 D3 0 0 0 1 D2 0 0 1 0 D1 0 1 0 0 D0 1 0 0 0 (b) 1) 译码器

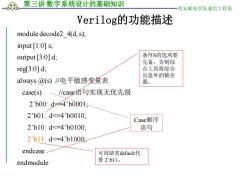

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module decode2 4(d,s); input [1:0]s, output [3:0]d; 条件S的选项要 完备,否则综 reg[3:0]d; 合工具将综合 出意外的锁存 always@(s)/电平敏感变量表 器。 case(s)/case语句实现无优先级 2b00:d<←4b0001; 2b01:d<=4b0010; Case顺序 2b10:d<=4b0100: 语句 2b11:d<=4b1000: endcase 可用缺省default代 endmodule 替2b11

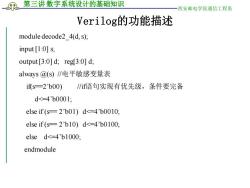

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module decode2_4(d, s); input [1:0] s; output [3:0] d; reg[3:0] d; always @(s) //电平敏感变量表 case(s) //case语句实现无优先级 2’b00: d<=4’b0001; 2’b01: d<=4’b0010; 2’b10: d<=4’b0100; 2’b11: d<=4’b1000; endcase endmodule Case顺序 语句 条件S的选项要 完备,否则综 合工具将综合 出意外的锁存 器。 可用缺省default代 替 2‘b11

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module decode2 4(d,s); input [1:0]s; output [3:0]d;reg[3:0]d; always@(s)∥电平敏感变量表 ifs==2'b00) /if语句实现有优先级,条件要完备 d<=4b0001; else if(s=2'b01)d<=4b0010: else if(s=2'b10)d<=4b0100; else d<=4'b1000: endmodule

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 Verilog的功能描述 module decode2_4(d, s); input [1:0] s; output [3:0] d; reg[3:0] d; always @(s) //电平敏感变量表 if(s==2’b00) //if语句实现有优先级,条件要完备 d<=4’b0001; else if (s== 2’b01) d<=4’b0010; else if (s== 2’b10) d<=4’b0100; else d<=4’b1000; endmodule

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 2)相等比较器 523 a,⊕b3 a2⊕b2 相等 -f No a1⊕b1 ao⊕bo 相 等 (a) (b) 图2-5相等比较器 (a)符号;(b)内部逻辑电路

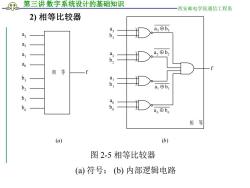

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-5 相等比较器 (a) 符号; (b) 内部逻辑电路 相 等 a3 a2 a1 a0 b 3 b2 b1 b0 f a3 b3 a 2 b2 a1 b1 a0 b0 f 3 3 a b 2 b2 a 1 1 a b 0 0 a b 相 等 (a) (b) 2) 相等比较器

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 3)多路复用器(多路选择器) 选择字 S So F S:So 0 0 Po 0 P 输 入 F输出 10 11 P (a) (b) 图2-64选1多路开关 (a)4选1开关操作;(b)功能表

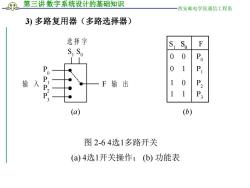

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-6 4选1多路开关 (a) 4选1开关操作; (b) 功能表 P0 P1 P2 P3 S1 S0 输 入 F 输 出 选 择 字 S1 S0 0 0 0 1 1 0 1 1 F P0 P1 P2 P3 S0 (a) (b) 3) 多路复用器(多路选择器)

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 多路复用器Verilogl的功能描述 module mux4 1(F,P,S); input [1:0]S; input [3:0]P; 条件赋值语句 output F; F=(条件)?A:B assign F=(S==2'b00)?P[O]: 功能:条件为真(1), A=>F,否则B=>F。 (S=2b01)?P[1]: (S==2b10)?P[2]P[3]; endmodule

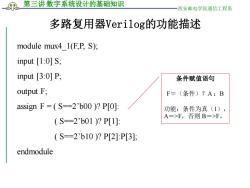

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 多路复用器Verilog的功能描述 module mux4_1(F,P, S); input [1:0] S; input [3:0] P; output F; assign F = ( S==2’b00 )? P[0]: ( S==2’b01 )? P[1]: ( S==2’b10 )? P[2]:P[3]; endmodule 条件赋值语句 F=(条件)?A :B 功能:条件为真(1), A=>F,否则 B=>F

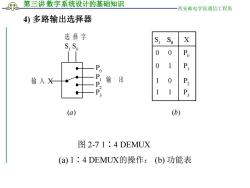

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 4)多路输出选择器 选择字 S X SSo 0 0 Po 0 P 输入X 输 出 10 1 P (a) (b) 图2-71:4 DEMUX (a)1:4 DEMUX的操作;(b)功能表

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 图 2-7 1∶4 DEMUX (a) 1∶4 DEMUX的操作; (b) 功能表 输 入 X 输 出 (a) (b) P0 P1 P2 P3 S0 S1 选择字 S1 S0 0 0 0 1 1 0 1 1 X P0 P1 P2 P3 S0 4) 多路输出选择器

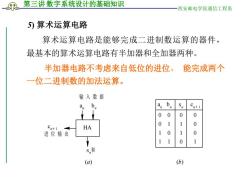

第三讲数字系统设计的基础知识 西安邮电学院通信工程系 5)算术运算电路 算术运算电路是能够完成二进制数运算的器件, 最基本的算术运算电路有半加器和全加器两种。 半加器电路不考虑来自低位的进位,能完成两个 一位二进制数的加法运算。 输入数据 a Sn Cn+1 0 0 0 0 0 1 1 0 Cn+1 HA 进位输出 1 0 1 0 1 0 1 S,和 (a) (b)

第三讲 数字系统设计的基础知识 西安邮电学院通信工程系 5) 算术运算电路 算术运算电路是能够完成二进制数运算的器件, 最基本的算术运算电路有半加器和全加器两种。 半加器电路不考虑来自低位的进位, 能完成两个 一位二进制数的加法运算。 HA 输入数据 an bn s n 和 cn+ 1 进位输出 0 0 0 1 1 0 1 1 0 1 1 0 (a) (b) a n b n s n c n+ 1 0 0 0 1

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第04讲 数据流建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第03讲 门级与结构建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)Verilog HDL数字系统设计与综合实验指导书(HDL语言硬件设计实验指导书).doc

- 《通信原理实验》课程教学资源(实验指导)基于System Generator的通信系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)嵌入式系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)数字系统与FPGA设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)高级软件无线电系统实验指导书.doc

- 《信号与系统》课程教学大纲 signals and systems.pdf

- 《电工学》课程教学大纲 Electrical Engineering.pdf

- 《电工学》课程教学大纲(电工技术 The teaching outline of Electrical Technology).pdf