《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 第六讲数字系统设计原则与设计实例 冬硬件原则 。面积和速度的平衡与互换原则 冬同步设计原则 同步系统时钟与复位规划 冬自顶向下设计原则 设计实例 本讲要点与实验要求

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 第六讲 数字系统设计原则与设计实例 ❖ 硬件原则 ❖ 面积和速度的平衡与互换原则 ❖ 同步设计原则 ❖ 同步系统时钟与复位规划 ❖ 自顶向下设计原则 ❖ 设计实例 ❖ 本讲要点与实验要求

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 硬件原则 硬件原则主要是针对DL设计代码编写而言,特别是具有软件编程 经验的初学者,片面追求代码的简短、整洁,如大量使用or循环, 而对HDL描述要实现的电路不胜了解。HDL仿真代码不受硬件原则 约束。硬件原则主要是指: 硬件描述语言(HDL),如verilog,本质上是硬件的抽象描述。 HDL描述的最终目标是生成芯片内部的实际电路。 HDL描述与软件语言,如C语言,有本质的区别。因C语言编译后, 基本上是在设计好的硬件电路(CPU)中按顺序运行的,而HDL描 述的是硬件电路本身。 评价一个HDL描述的质量,主要看该HDL是否能够与综合工具配合, 按设计者的构想合理地生成硬件电路

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 硬件原则 ❖ 硬件原则主要是针对HDL设计代码编写而言,特别是具有软件编程 经验的初学者,片面追求代码的简短、整洁,如大量使用for循环, 而对HDL描述要实现的电路不胜了解。HDL仿真代码不受硬件原则 约束。硬件原则主要是指: ▪ 硬件描述语言(HDL),如verilog,本质上是硬件的抽象描述。 ▪ HDL描述的最终目标是生成芯片内部的实际电路。 ▪ HDL描述与软件语言,如C语言,有本质的区别。因C语言编译后, 基本上是在设计好的硬件电路(CPU)中按顺序运行的,而HDL描 述的是硬件电路本身。 ▪ 评价一个HDL描述的质量,主要看该HDL是否能够与综合工具配合, 按设计者的构想合理地生成硬件电路

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 硬件原则 冬按硬件原则,DL的正确编写方法是: 设计者要对所设计的硬件电路功能十分清楚。 合理安排电路的数据流和控制逻辑,构思RTL级电路体系结构。 ■ 掌握综合工具要求和性能。 用适当的、综合工具能理解的HDL语言描述出来。 冬目前纯行为级的综合还不成熟,RTL级综合仍是主流。 在目前主流综合工具中,部分行为描述语句可以综合,如c<=a*b 的乘法语句,quartus22内嵌综合工具会综合成LPM乘法宏模块。 冬那些行为描述可以综合,决定于具体的综合工具,可参考综合工 具的使用手册

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 硬件原则 ❖ 按硬件原则,HDL的正确编写方法是: ▪ 设计者要对所设计的硬件电路功能十分清楚。 ▪ 合理安排电路的数据流和控制逻辑,构思RTL级电路体系结构。 ▪ 掌握综合工具要求和性能。 ▪ 用适当的、综合工具能理解的HDL语言描述出来。 ❖ 目前纯行为级的综合还不成熟,RTL级综合仍是主流。 ❖ 在目前主流综合工具中,部分行为描述语句可以综合,如c<=a*b 的乘法语句,quartus2内嵌综合工具会综合成LPM乘法宏模块。 ❖ 那些行为描述可以综合,决定于具体的综合工具,可参考综合工 具的使用手册

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 面积和速度的平衡与互换原则 ,面积是指一个设计消耗的逻辑资源数量,对FPGA可以用触发器和组合逻 辑单元来度量。速度指设计在芯片上稳定运行时能够达到的最高频率。 必 面积和速度是一对矛盾的需求。要求一个设计同时具有设计面积最小, 运行速度最高是不现实的。 冬平衡的设计目标是:在满足设计工作速度要求的前提下,占用最小的芯 片面积:或芯片面积一定的情况下,使设计的工作速度最高。对应的综 合工具有相关的综合策略,如面积优先、速度优先或平衡方式。 文 面积和速度的互换是IC设计的重要思想。如果一个设计时序余量较大, 即工作速度远高于设计要求,就可以考虑采用串行方式复用部分逻辑, 用速度换面积:反之工作速度不够时,可采用并行处理提高工作速度, 即用面积换速度。 。当面积和速度设计要求不能同时满足时,采用速度优先原则

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 面积和速度的平衡与互换原则 ❖ 面积是指一个设计消耗的逻辑资源数量,对FPGA可以用触发器和组合逻 辑单元来度量。速度指设计在芯片上稳定运行时能够达到的最高频率。 ❖ 面积和速度是一对矛盾的需求。要求一个设计同时具有设计面积最小, 运行速度最高是不现实的。 ❖ 平衡的设计目标是:在满足设计工作速度要求的前提下,占用最小的芯 片面积;或芯片面积一定的情况下,使设计的工作速度最高。对应的综 合工具有相关的综合策略,如面积优先、速度优先或平衡方式。 ❖ 面积和速度的互换是IC设计的重要思想。如果一个设计时序余量较大, 即工作速度远高于设计要求,就可以考虑采用串行方式复用部分逻辑, 用速度换面积;反之工作速度不够时,可采用并行处理提高工作速度, 即用面积换速度。 ❖ 当面积和速度设计要求不能同时满足时,采用速度优先原则

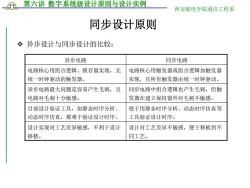

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步设计原则 。异步设计与同步设计的比较: 异步电路 同步电路 电路核心用组合逻辑、锁存器实现,无 电路核心用触发器或组合逻辑加触发器 统一时钟驱动的触发器。 实现,且所有触发器由统一时钟驱动。 异步电最大问题是容易产生毛刺,且 同步电路中组合逻辑也产生毛刺,但触 电路对毛刺十分敏感。 发器在建立保持窗外对毛刺不敏感。 目前设计验证工具,如静态时序分析、 便于用静态时序分析、动态时序仿真等 动态时序仿真,都难于验证设计时序。 工具验证设计时序。 设计实现对工艺差异敏感,不利于设计 设计对工艺差异不敏感,便于移植到不 移植。 同工艺

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步设计原则 ❖ 异步设计与同步设计的比较: 异步电路 同步电路 电路核心用组合逻辑、锁存器实现,无 统一时钟驱动的触发器。 电路核心用触发器或组合逻辑加触发器 实现,且所有触发器由统一时钟驱动。 异步电路最大问题是容易产生毛刺,且 电路对毛刺十分敏感。 同步电路中组合逻辑也产生毛刺,但触 发器在建立保持窗外对毛刺不敏感。 目前设计验证工具,如静态时序分析、 动态时序仿真,都难于验证设计时序。 便于用静态时序分析、动态时序仿真等 工具验证设计时序。 设计实现对工艺差异敏感,不利于设计 移植。 设计对工艺差异不敏感,便于移植到不 同工艺

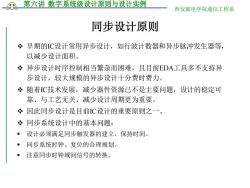

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步设计原则 早期的C设计常用异步设计,如行波计数器和异步脉冲发生器等, 以减少设计面积。 ?异步设计时序控制相当繁杂而困难,且目前EDA工具多不支持异 步设计,较大规模的异步设计十分费时费力。 随着C技术发展,减少器件资源已不是主要问题,设计的稳定可 靠、与工艺无关,减少设计周期更为重要。 。因此同步设计是目前C设计的重要原则之一。 冬同步系统设计中的基本问题: 设计必须满足同步触发器的建立、保持时间。 同步系统时钟、复位的合理规划。 ·注意同步时钟域间信号的转换

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步设计原则 ❖ 早期的IC设计常用异步设计,如行波计数器和异步脉冲发生器等, 以减少设计面积。 ❖ 异步设计时序控制相当繁杂而困难,且目前EDA工具多不支持异 步设计,较大规模的异步设计十分费时费力。 ❖ 随着IC技术发展,减少器件资源已不是主要问题,设计的稳定可 靠、与工艺无关,减少设计周期更为重要。 ❖ 因此同步设计是目前IC设计的重要原则之一。 ❖ 同步系统设计中的基本问题: ▪ 设计必须满足同步触发器的建立、保持时间。 ▪ 同步系统时钟、复位的合理规划。 ▪ 注意同步时钟域间信号的转换

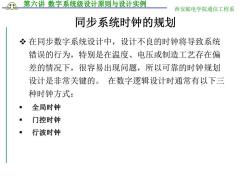

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步系统时钟的规划 。在同步数字系统设计中,设计不良的时钟将导致系统 错误的行为,特别是在温度、电压或制造工艺存在偏 差的情况下,很容易出现问题,所以可靠的时钟规划 设计是非常关键的。在数字逻辑设计时通常有以下三 种时钟方式: 全局时钟 门控时钟 行波时钟

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 同步系统时钟的规划 ❖ 在同步数字系统设计中,设计不良的时钟将导致系统 错误的行为,特别是在温度、电压或制造工艺存在偏 差的情况下,很容易出现问题,所以可靠的时钟规划 设计是非常关键的。 在数字逻辑设计时通常有以下三 种时钟方式: ▪ 全局时钟 ▪ 门控时钟 ▪ 行波时钟

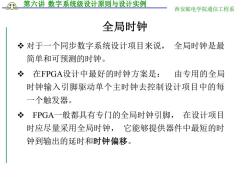

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 全局时钟 冬对于一个同步数字系统设计项目来说,全局时钟是最 简单和可预测的时钟。 文 在FPGA设计中最好的时钟方案是: 由专用的全局 时钟输入引脚驱动单个主时钟去控制设计项目中的每 一个触发器。 FPGA一般都具有专门的全局时钟引脚,在设计项目 时应尽量采用全局时钟,它能够提供器件中最短的时 钟到输出的延时和时钟偏移

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 全局时钟 ❖ 对于一个同步数字系统设计项目来说, 全局时钟是最 简单和可预测的时钟。 ❖ 在FPGA设计中最好的时钟方案是: 由专用的全局 时钟输入引脚驱动单个主时钟去控制设计项目中的每 一个触发器。 ❖ FPGA一般都具有专门的全局时钟引脚, 在设计项目 时应尽量采用全局时钟, 它能够提供器件中最短的时 钟到输出的延时和时钟偏移

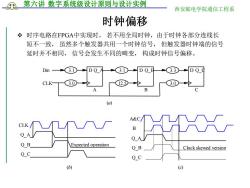

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 时钟偏移 冬时序电路在FPGA中实现时,若不用全局时钟,由于时钟各部分连线长 短不一致,虽然多个触发器共用一个时钟信号, 但触发器时钟端的信号 延时并不相同,信号会发生不同的畸变,构成时钟信号偏移。 Din CLK A B (a) A&C CLK B QB Expected operation Clock skewed version Q C (b) (c)

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 时钟偏移 ❖ 时序电路在FPGA中实现时, 若不用全局时钟,由于时钟各部分连线长 短不一致, 虽然多个触发器共用一个时钟信号, 但触发器时钟端的信号 延时并不相同, 信号会发生不同的畸变, 构成时钟信号偏移。 D Q_A A 3.0 3.1 CLK Din D Q_B B 12.5 3.1 D Q_C C 3.0 3.3 (a) Expected operation CLK Q_A Q_B Q_C (b) Clock skewed version A&C Q_A Q_B Q_C (c) B

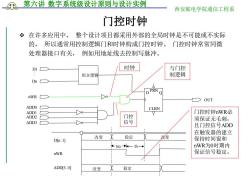

第六讲数字系统级设计原则与设计实例 西安邮电学院通信工程系 门控时钟 在许多应用中, 整个设计项目都采用外部的全局时钟是不可能或不实际 的,所以通常用控制逻辑门和时钟构成门控时钟。门控时钟常常同微 处理器接口有关,例如用地址线去控制写脉冲。 DI 时钟 与门控 组合逻辑 制逻辑 Dn D PRN Q nWR OUT ADDO CLRN ADDI 门控时钟nWR必 ADD2 门控 须保证无毛刺, ADD3 信号 且门控信号ADD 在触发器的建立 改变 稳定 改变 D(n.1] 保持时间窗和 +su一h+ nWR为0时期内 nWR 保证信号稳定。 ADD[3.0] 改变 稳定

第六讲 数字系统级设计原则与设计实例 西安邮电学院通信工程系 门控时钟 ❖ 在许多应用中, 整个设计项目都采用外部的全局时钟是不可能或不实际 的, 所以通常用控制逻辑门和时钟构成门控时钟。 门控时钟常常同微 处理器接口有关, 例如用地址线去控制写脉冲。 改变 稳定 改变 改变 稳定 D[n.1] nWR ADD[3.0] tsu th D Q PRN CLRN 组合逻辑 D1 . Dn OUT nWR ADD0 ADD1 ADD2 ADD3 门控时钟nWR必 须保证无毛刺, 且门控信号ADD 在触发器的建立 保持时间窗和 nWR为0时期内 保证信号稳定。 时钟 门控 信号 与门控 制逻辑

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)Verilog HDL数字系统设计与综合实验指导书(HDL语言硬件设计实验指导书).doc

- 《通信原理实验》课程教学资源(实验指导)基于System Generator的通信系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)嵌入式系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)数字系统与FPGA设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)高级软件无线电系统实验指导书.doc

- 《信号与系统》课程教学大纲 signals and systems.pdf

- 《电工学》课程教学大纲 Electrical Engineering.pdf

- 《电工学》课程教学大纲(电工技术 The teaching outline of Electrical Technology).pdf

- 《电工学》课程授课教案(讲义)可编程控制器(PLC)实验——入门篇.doc

- 《电工学》课程授课教案(讲义)可编程控制器及其应用(关于西门子S7-200可编程控制器).doc

- 《电工学》课程教学资源(PPT课件)第04章 非正弦周期信号电路.ppt