《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4)

第5章目录 口1.简介 ▣10.UART0 ▣2.引脚配置 ▣11.UART1 ▣3.存储器寻址 ▣12.2C接▣ 口4.系统控制模块 ▣13.SPI接口 ▣5.存储器加速模块 ▣14.定时器0/1 口6.外部存储器控制器 ▣15.脉宽调制器(PWM) ▣7.引脚连接模块 ▣16.AD转换器 口8.向量中断控制器 ▣17.实时时钟 ▣9.GPIO ▣18.看门狗

第5章 目录 ❑1.简介 ❑2.引脚配置 ❑3.存储器寻址 ❑4.系统控制模块 ❑5.存储器加速模块 ❑6.外部存储器控制器 ❑7.引脚连接模块 ❑8. 向量中断控制器 ❑9.GPIO ❑10.UART0 ❑11.UART1 ❑12.I2C接口 ❑13.SPI接口 ❑14.定时器0/1 ❑15.脉宽调制器(PWM) ❑16.A/D转换器 ❑17.实时时钟 ❑18.看门狗

5.5存储器加速模块(MAM) ·概述 LPC2114/2124/2210/2212/2214微控制器的 ARM内核工作在最高频率60MHz时,执行一条指 令约为17ns。而Flash存储器的访问周期需要50n5, 即最高频率20MHz。所以如果将代码存放在Flash 中,将影响ARM内核发辉最大效能。为了能将指 令从内部Flash存储器更高效快速地提取到ARM内 核,而设计产生了一个存储器加速模块(MAM)

5.5 存储器加速模块(MAM) • 概述 LPC2114/2124/2210/2212/2214微控制器的 ARM内核工作在最高频率60MHz时,执行一条指 令约为17ns。而Flash存储器的访问周期需要50ns, 即最高频率20MHz。所以如果将代码存放在Flash 中,将影响ARM内核发挥最大效能。为了能将指 令从内部Flash存储器更高效快速地提取到ARM内 核,而设计产生了一个存储器加速模块(MAM)

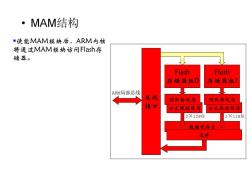

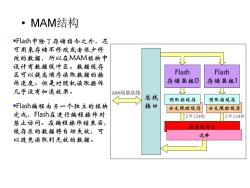

·MAM结构 ■使能MAM模块后,ARM内核 将通过MAM模块访问Flash存 储器。 Flash Flash 存储器组0 存储器组1 ARM局部总线 总线 预取指缓存 预取指缓存 接口 分支跟踪缓存 分支跟踪缓存 2X128位 2×128位 数据缓存国 选择

分支跟踪缓存 分支跟踪缓存 总线 接口 Flash 存储器组0 Flash 存储器组1 预取指缓存 预取指缓存 数据缓存区 选择 ARM局部总线 2×128位 2×128位 • MAM结构 ▪使能MAM模块后,ARM内核 将通过MAM模块访问Flash存 储器。 Flash 存储器组0 Flash 存储器组1 分支跟踪缓存 分支跟踪缓存 预取指缓存 预取指缓存 数据缓存区 选择 总线 接口

·MAM结构 ■使能MAM模块后,ARM内核 将通过MAM模块访问Flash存 储器。 MAM模块中的数据总线宽度 Flash Flash 为128位,所以一次读取操作可 存储器组0 存储器组1] 以读出4条ARM指令或8条 Thumb指令o ARM局部总线 线 预取指缓存 预取指缓存 ■Flash存储器被分为两组,当 分支跟踪缓存 分支跟踪缓存 CPU执行其中一组Flash内的指 2×128位 2X128位 令时,另一组进行读取缓存操 数据缓存区 作。 ■每个Flash组包会预取指缓存和 分支跟踪缓存

• MAM结构 ▪Flash存储器被分为两组,当 CPU执行其中一组Flash内的指 令时,另一组进行读取缓存操 作。 ▪使能MAM模块后,ARM内核 将通过MAM模块访问Flash存 储器。 ▪每个Flash组包含预取指缓存和 分支跟踪缓存。 分支跟踪缓存 分支跟踪缓存 总线 接口 Flash 存储器组0 Flash 存储器组1 预取指缓存 预取指缓存 数据缓存区 选择 ARM局部总线 2×128位 2×128位 ▪MAM模块中的数据总线宽度 为128位,所以一次读取操作可 以读出4条ARM指令或8条 Thumb指令。 分支跟踪缓存 预取指缓存 分支跟踪缓存 Flash 存储器组1 预取指缓存 分支跟踪缓存 预取指缓存 Flash 存储器组0 分支跟踪缓存 预取指缓存 预取指缓存

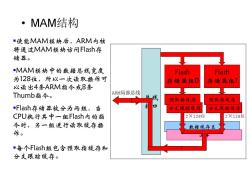

·MAM结构 ■预取指缓存区保存有将要执行 的指令。而分支跟踪缓存区保 存有程序跳转后可能执行到的 指令。 Flash Flash ■当程序向前跳转时,尝试从预 存储器组0 存储器组1 取指缓存区取指。 ARM局部总线 ■当程序向后跳转时,尝试从分 总线 预取指缓存 预取指缓存 支跟踪缓存区取指。 接口 分支跟踪缓存 分支跟踪缓存 2×128位 2X128位 ■如果程序跳转出缓存的范围, 数据缓存区 CPU将要停止,等待若干个周 选择 期,直到正确的指令从Flash中 被读出

分支跟踪缓存 分支跟踪缓存 • MAM结构 总线 接口 Flash 存储器组0 Flash 存储器组1 预取指缓存 预取指缓存 数据缓存区 选择 ARM局部总线 ▪当程序向前跳转时,尝试从预 取指缓存区取指。 2×128位 2×128位 ▪如果程序跳转出缓存的范围, CPU将要停止,等待若干个周 期,直到正确的指令从Flash中 被读出。 ▪当程序向后跳转时,尝试从分 支跟踪缓存区取指。 ▪预取指缓存区保存有将要执行 的指令。而分支跟踪缓存区保 存有程序跳转后可能执行到的 指令

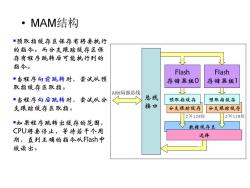

·MAM结构 Flash中除了存储指令之外,还 可用来存储不修改或者很少修 改的数据,所以在MAM模块中 设计有数据缓冲区。数据缓存 区可以提高顺序读取数据的操 Flash Flash 作速度。但是对随机读取操作 存储器组0 存储器组1 几乎没有加速效果。 ARM局部总线 总线 预取指缓存 预取指缓存 Flash编程由另一个独立的模块 接口 分支跟踪缓存 分支跟踪缓存 完成,Flash在进行编程操作时 2X128位 2×128位 禁止访问。在编程操作结束后, 数据缓存国 缓存区的数据将自动失效,可 选择 以避免读取到无效的数据

分支跟踪缓存 分支跟踪缓存 • MAM结构 总线 接口 Flash 存储器组0 Flash 存储器组1 预取指缓存 预取指缓存 数据缓存区 ARM局部总线 2×128位 2×128位 ▪Flash中除了存储指令之外,还 可用来存储不修改或者很少修 改的数据,所以在MAM模块中 设计有数据缓冲区。数据缓存 区可以提高顺序读取数据的操 作速度。但是对随机读取操作 几乎没有加速效果。 数据缓存区 ▪Flash编程由另一个独立的模块 完成,Flash在进行编程操作时 禁止访问。在编程操作结束后, 缓存区的数据将自动失效,可 以避免读取到无效的数据。 选择

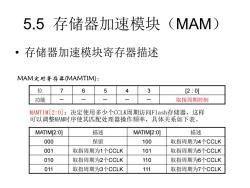

5.5存储器加速模块(MAM) ·存储器加速模块寄存器描述 MAM控制寄存器(MAMCR): 位 7 6 5 4 3 2 [1:0] 功能 模式控制 MAMCR[1:O]:用于MAM的模式控制,具体关系如下表。 MAMCR[1:0] 描述 00 禁止MAM功能 01 部分使能MAM功能 10 完全使能MAM功能 11 保留

5.5 存储器加速模块(MAM) • 存储器加速模块寄存器描述 MAM控制寄存器(MAMCR): MAMCR[1:0]:用于MAM的模式控制,具体关系如下表。 位 7 6 5 4 3 2 [1 : 0] 功能 - - - - - - 模式控制 MAMCR[1:0] 描述 00 禁止MAM功能 01 部分使能MAM功能 10 完全使能MAM功能 11 保留

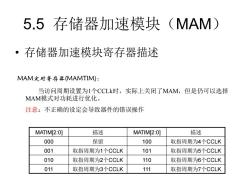

5.5存储器加速模块(MAM) ·存储器加速模块寄存器描述 MAM定时寺存器(AAMTIM): 位 7 6 5 4 3 [2:0] 功能 取指周期控制 MAMTIM[2:O]:决定使用多少个CCLK周期访问Flash存储器,这样 可以调整MAM时序使其匹配处理器操作频率,具体关系如下表。 MATIM[2:0] 描述 MATIM[2:0] 描述 000 保留 100 取指周期为4个CCLK 001 取指周期为1个CCLK 101 取指周期为5个CCLK 010 取指周期为2个CCLK 110 取指周期为6个CCLK 011 取指周期为3个CCLK 111 取指周期为7个CCLK

5.5 存储器加速模块(MAM) • 存储器加速模块寄存器描述 MAM定时寄存器(MAMTIM): MAMTIM[2:0]:决定使用多少个CCLK周期访问Flash存储器,这样 可以调整MAM时序使其匹配处理器操作频率,具体关系如下表。 位 7 6 5 4 3 [2 : 0] 功能 - - - - - 取指周期控制 MATIM[2:0] 描述 MATIM[2:0] 描述 000 保留 100 取指周期为4个CCLK 001 取指周期为1个CCLK 101 取指周期为5个CCLK 010 取指周期为2个CCLK 110 取指周期为6个CCLK 011 取指周期为3个CCLK 111 取指周期为7个CCLK

5.5存储器加速模块(MAM) ·存储器加速模块寄存器描述 MAM定时寺存器(MAMTIM): 当访问周期设置为1个CCLk时,实际上关闭了MAM,但是仍可以选择 MAM模式对功耗进行优化。 注意:不正确的设定会导致器件的错误操作 MATIM[2:0] 描述 MATIM[2:0] 描述 000 保留 100 取指周期为4个CCLK 001 取指周期为1个CCLK 101 取指周期为5个CCLK 010 取指周期为2个CCLK 110 取指周期为6个CCLK 011 取指周期为3个CCLK 111 取指周期为7个CCLK

5.5 存储器加速模块(MAM) • 存储器加速模块寄存器描述 MAM定时寄存器(MAMTIM): MATIM[2:0] 描述 MATIM[2:0] 描述 000 保留 100 取指周期为4个CCLK 001 取指周期为1个CCLK 101 取指周期为5个CCLK 010 取指周期为2个CCLK 110 取指周期为6个CCLK 011 取指周期为3个CCLK 111 取指周期为7个CCLK 当访问周期设置为1个CCLk时,实际上关闭了MAM,但是仍可以选择 MAM模式对功耗进行优化。 注意:不正确的设定会导致器件的错误操作

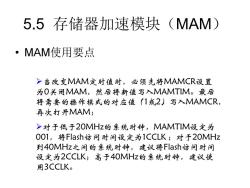

5.5存储器加速模块(MAM) ·MAM使用要点 >当改变MAM定时值时,必须先将MAMCR设置 为O关闭MAM,然后将新值写入MAMTIM。最后 将需要的操作模式的对应值(1或2)写入MAMCR, 再次打开MAM; >对于低于20MHz的条统时钟,MAMTIM.设定为 001,将Flash访问时间设定为1CCLK;对于20MHz 到40MHz之间的系统时钟,建议将Flash访问时间 设定为2CCLK;高于40MHz的系统时钟,建议使 用3CCLK

5.5 存储器加速模块(MAM) • MAM使用要点 ➢当改变MAM定时值时,必须先将MAMCR设置 为0关闭MAM,然后将新值写入MAMTIM。最后 将需要的操作模式的对应值(1或2)写入MAMCR, 再次打开MAM; ➢对于低于20MHz的系统时钟,MAMTIM设定为 001,将Flash访问时间设定为1CCLK ;对于20MHz 到40MHz之间的系统时钟,建议将Flash访问时间 设定为2CCLK;高于40MHz的系统时钟,建议使 用3CCLK

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第04讲 数据流建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第03讲 门级与结构建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第02讲 Verilog HDL语言基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第01讲 HDL语言概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(3/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(2/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(1/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 5Digital Transmission Through Bandlimited Channels.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multidimensional Signals).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multiamplitude Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)Verilog HDL数字系统设计与综合实验指导书(HDL语言硬件设计实验指导书).doc

- 《通信原理实验》课程教学资源(实验指导)基于System Generator的通信系统设计实验指导书.doc