《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 第五讲数字系统设计的实现与验证 什么是逻辑综合 Verilog HDL的综合要求 逻辑综合流程、工艺库和设计约束 基于quartus2的逻辑综合与实现 冬静态时序分析验证 冬辅助设计工具简介 冬动态时序仿真验证 编程与配置

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 第五讲 数字系统设计的实现与验证 ❖ 什么是逻辑综合 ❖ Verilog HDL的综合要求 ❖ 逻辑综合流程、工艺库和设计约束 ❖ 基于quartus2的逻辑综合与实现 ❖ 静态时序分析验证 ❖ 辅助设计工具简介 ❖ 动态时序仿真验证 ❖ 编程与配置

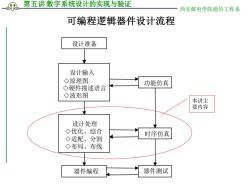

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 可编程逻辑器件设计流程 设计准备 设计输入 ◇原理图 功能仿真 ◇硬件描述语言 ◇波形图 本讲主 要内容 设计处理 ◇优化、综合 时序仿真 ◇适配、分割 ◇布局、布线 器件编程 器件测试

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 可编程逻辑器件设计流程 设计准备 设计输入 ◇原理图 ◇硬件描述语言 ◇波形图 设计处理 ◇优化、综合 ◇适配、分割 ◇布局、布线 器件编程 器件测试 时序仿真 功能仿真 本讲主 要内容

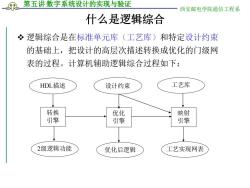

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 什么是逻辑综合 ?逻辑综合是在标准单元库(工艺库)和特定设计约束 的基础上,把设计的高层次描述转换成优化的门级网 表的过程。计算机辅助逻辑综合过程如下: HDL描述 设计约束 工艺库 转换 优化 映射 引擎 引擎 引擎 2级逻辑功能 优化后逻辑 工艺实现网表

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 什么是逻辑综合 ❖ 逻辑综合是在标准单元库(工艺库)和特定设计约束 的基础上,把设计的高层次描述转换成优化的门级网 表的过程。计算机辅助逻辑综合过程如下: HDL描述 转换 引擎 2级逻辑功能 优化后逻辑 工艺实现网表 工艺库 优化 引擎 映射 引擎 设计约束

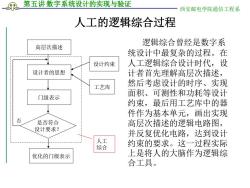

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 人工的逻辑综合过程 逻辑综合曾经是数字系 高层次描述 统设计中最复杂的过程。在 设计约束 人工逻辑综合设计时代,设 设计者的思想 计者首先理解高层次描述, 工艺库 然后考虑设计的时序、实现 面积、可测性和功耗等设计 门级表示 约束,最后用工艺库中的器 件作为基本单元,画出实现 是否符合 高层次描述的逻辑电路图, 设计要求? 并反复优化电路,达到设计 人 综合 约束的要求。这一过程实际 优化的门级表示 上是将人的大脑作为逻辑综 合工具

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 人工的逻辑综合过程 逻辑综合曾经是数字系 统设计中最复杂的过程。在 人工逻辑综合设计时代,设 计者首先理解高层次描述, 然后考虑设计的时序、实现 面积、可测性和功耗等设计 约束,最后用工艺库中的器 件作为基本单元,画出实现 高层次描述的逻辑电路图, 并反复优化电路,达到设计 约束的要求。这一过程实际 上是将人的大脑作为逻辑综 合工具。 高层次描述 设计者的思想 门级表示 优化的门级表示 设计约束 工艺库 是否符合 设计要求? 人工 综合 否

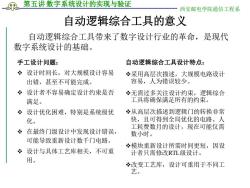

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 自动逻辑综合工具的意义 自动逻辑综合工具带来了数字设计行业的革命,是现代 数字系统设计的基础。 手工设计问题: 自动逻辑综合工具设计特点: 冬设计时间长,对大规模设计容易 采用高层次描述,大规模电路设计 出错,甚至不可能完成。 容易,人为错误较少。 设计者不容易确定设计约束是否 ?无需过多关注设计约束,逻辑综合 满足。 工具将确保满足所有的约束。 设计优化困难,特别是系统级优 ~从高层次描述到逻辑门的转换非常 化。 快,且可得到全局优化的电路。人 工耗费数月的设计,现在可能仅需 。 在最终门级设计中发现设计错误, 数小时。 可能导致重新设计数千门电路。 冬模块重新设计所需时间更短,因设 设计与具体工艺库相关,不可重 计者只需修改RTL级设计。 用。 改变工艺库,设计可重用于不同工 艺

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 自动逻辑综合工具的意义 手工设计问题: ❖ 设计时间长,对大规模设计容易 出错,甚至不可能完成。 ❖ 设计者不容易确定设计约束是否 满足。 ❖ 设计优化困难,特别是系统级优 化。 ❖ 在最终门级设计中发现设计错误, 可能导致重新设计数千门电路。 ❖ 设计与具体工艺库相关,不可重 用。 自动逻辑综合工具带来了数字设计行业的革命,是现代 数字系统设计的基础。 自动逻辑综合工具设计特点: ❖采用高层次描述,大规模电路设计 容易,人为错误较少。 ❖无需过多关注设计约束,逻辑综合 工具将确保满足所有的约束。 ❖从高层次描述到逻辑门的转换非常 快,且可得到全局优化的电路。人 工耗费数月的设计,现在可能仅需 数小时。 ❖模块重新设计所需时间更短,因设 计者只需修改RTL级设计。 ❖改变工艺库,设计可重用于不同工 艺

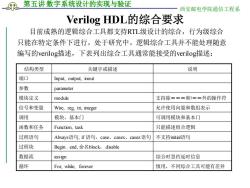

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 Verilog HDL的综合要求 目前成熟的逻辑综合工具都支持RTL级设计的综合,行为级综合 只能在特定条件下进行,处于研究中。逻辑综合工具并不能处理随意 编写的verilog描述,下表列出综合工具通常能接受的verilog描述: 结构类型 关键字或描述 说明 端口 Input,output,inout 参数 parameter 模块定义 module 支持除===和!==外的操作符 信号和变量 Wire,reg,tri,integer 允许使用向量和数组表示 调用 模块,基本门 可调用模块和基本门 函数和任务 Function,task 只能描述组合逻辑 过程语句 Always语句,f语句,case、casex、casez语句 不支持initiali语句 过程块 Begin.end,命名block,disable 数据流 assign 综合时忽约延时信息 循环 For,while,forever 慎用,不同综合工具可能有差异

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 Verilog HDL的综合要求 目前成熟的逻辑综合工具都支持RTL级设计的综合,行为级综合 只能在特定条件下进行,处于研究中。逻辑综合工具并不能处理随意 编写的verilog描述,下表列出综合工具通常能接受的verilog描述: 结构类型 关键字或描述 说明 端口 Input, output, inout 参数 parameter 模块定义 module 支持除===和!==外的操作符 信号和变量 Wire, reg, tri, integer 允许使用向量和数组表示 调用 模块,基本门 可调用模块和基本门 函数和任务 Function, task 只能描述组合逻辑 过程语句 Always语句, if 语句,case、casex、casez 语句 不支持initial语句 过程块 Begin. end, 命名block,disable 数据流 assign 综合时忽约延时信息 循环 For, while, forever 慎用,不同综合工具可能有差异

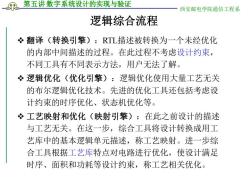

第五讲数字系统设计的实现与验证 -0001 西安邮电学院通信工程系 逻辑综合流程 。翻译(转换引擎):RTL描述被转换为一个未经优化 的内部中间描述的过程。在此过程不考虑设计约束, 不同工具有不同表示方法,用户无法了解。 冬逻辑优化(优化引擎):逻辑优化使用大量工艺无关 的布尔逻辑优化技术。先进的优化工具还包括考虑设 计约束的时序优化、状态机优化等。 冬工艺映射和优化(映射引擎):在此之前设计的描述 与工艺无关。在这一步,综合工具将设计转换成用工 艺库中的基本逻辑单元描述,称工艺映射。进一步综 合工具根据工艺库特点对电路进行优化,使设计满足 时序、面积和功耗等设计约束,称工艺相关优化

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 逻辑综合流程 ❖ 翻译(转换引擎):RTL描述被转换为一个未经优化 的内部中间描述的过程。在此过程不考虑设计约束, 不同工具有不同表示方法,用户无法了解。 ❖ 逻辑优化(优化引擎):逻辑优化使用大量工艺无关 的布尔逻辑优化技术。先进的优化工具还包括考虑设 计约束的时序优化、状态机优化等。 ❖ 工艺映射和优化(映射引擎):在此之前设计的描述 与工艺无关。在这一步,综合工具将设计转换成用工 艺库中的基本逻辑单元描述,称工艺映射。进一步综 合工具根据工艺库特点对电路进行优化,使设计满足 时序、面积和功耗等设计约束,称工艺相关优化

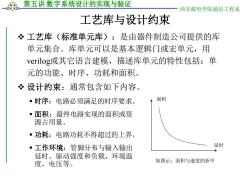

第五讲数字系统设计的实现与验证 -000 西安邮电学院通信工程系 工艺库与设计约束 工艺库(标准单元库):是由器件制造公司提供的库 单元集合。库单元可以是基本逻辑门或宏单元,用 verilog或其它语言建模,描述库单元的特性包括:单 元的功能、时序、功耗和面积。 冬设计约束:通常包含如下内容。 ■时序:电路必须满足的时序要求。 面积 面积:最终电路实现的面积或资 源占用量。 ·功耗:电路功耗不得超过的上界。 ·工作环境:管脚分布与输入输出 延时 延时、驱动强度和负载,环境温 度,电压等。 如图示:面积与速度的折中

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 工艺库与设计约束 ❖ 工艺库(标准单元库):是由器件制造公司提供的库 单元集合。库单元可以是基本逻辑门或宏单元,用 verilog或其它语言建模,描述库单元的特性包括:单 元的功能、时序、功耗和面积。 ❖ 设计约束:通常包含如下内容。 ▪ 时序:电路必须满足的时序要求。 ▪ 面积:最终电路实现的面积或资 源占用量。 ▪ 功耗:电路功耗不得超过的上界。 ▪ 工作环境:管脚分布与输入输出 延时、驱动强度和负载,环境温 度,电压等。 延时 面积 如图示:面积与速度的折中

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 基于quartus2的逻辑综合与实现 常用的FPGA设计综合工具有Synplify、LeonardoSpectrum、FPGA Compiler等。Quartus.2软件自身也集成有综合工具,虽不如上述工具功 能强大,但也有自身的优点。 在使用综合工具时,一般不能直接修改综合的网表,只能通过修改 HDL设计或设计约束间接控制综合的结果。本讲以4bt串行乘法器设计 为例,介绍quartus.2的综合工具与实现设置,包括如下内容: 分配芯片管脚、时序约束输入。 综合工具设置。 冬综合网表的优化。 冬时序驱动的分配设置

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 基于quartus2的逻辑综合与实现 常用的FPGA设计综合工具有Synplify、LeonardoSpectrum、FPGA Compiler等。Quartus2软件自身也集成有综合工具,虽不如上述工具功 能强大,但也有自身的优点。 在使用综合工具时,一般不能直接修改综合的网表,只能通过修改 HDL设计或设计约束间接控制综合的结果。本讲以4bit串行乘法器设计 为例,介绍quartus2的综合工具与实现设置,包括如下内容: ❖分配芯片管脚、时序约束输入。 ❖综合工具设置。 ❖综合网表的优化。 ❖时序驱动的分配设置

第五讲数字系统设计的实现与验证 西安邮电学院通信工程系 分配芯片管脚 Quartus II-D:/FPGA讲义/ULI/U皿T-夏ULT File Edit yiew Project Assignments Processing Ioo1s置indow Help Y卫evice. 可效’g必必 Status Lins Module Prog. Timing Settings. 2EDA Tool Settings. Settings. Ctrl+Shift+E Timing置izard., g Assignment Editor Ctrl+Shift+A 毯Tinr1 anner Ctrl+Shi ft+N 且emove Assignments.,. AN店R 吕Be地te Assigmments Project Navigatorx Back-Annotate Assignments. Entity △Cyclone:EP1C3T Import Assignments. ART 由-意y-nlt4 Export Assignments.,· Assignment (Time)Groups. Timing Closure Eloorplan 打开管脚 LogicLock Regions Window Alt+L 编辑器 Design Partitions Window Alt+D

第五讲 数字系统设计的实现与验证 西安邮电学院通信工程系 分配芯片管脚 打开管脚 编辑器

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)Verilog HDL数字系统设计与综合实验指导书(HDL语言硬件设计实验指导书).doc

- 《通信原理实验》课程教学资源(实验指导)基于System Generator的通信系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)嵌入式系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)数字系统与FPGA设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)高级软件无线电系统实验指导书.doc

- 《信号与系统》课程教学大纲 signals and systems.pdf

- 《电工学》课程教学大纲 Electrical Engineering.pdf

- 《电工学》课程教学大纲(电工技术 The teaching outline of Electrical Technology).pdf

- 《电工学》课程授课教案(讲义)可编程控制器(PLC)实验——入门篇.doc

- 《电工学》课程授课教案(讲义)可编程控制器及其应用(关于西门子S7-200可编程控制器).doc