《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2)

第3章目录 口1.简介 口9.异常 ▣2.ARM7TDMI ▣10.中断延迟 ▣3.ARM7TDMI的模块和 ▣11.复位 内部框图 口12.存储器及存储器映射 口4.体系结构直接支持的 I/O 数据类型 ▣13.寻址方式简介 ▣5.处理器状态 口14.ARM7指令简介 ▣6处理器模式 口15.协处理器接口 口7.内部寄存器 口16.调试接口简介 口8.程序状态寄存器 ▣17ETM接口简介

第3章 目录 ❑1.简介 ❑2.ARM7TDMI ❑3.ARM7TDMI的模块和 内部框图 ❑4.体系结构直接支持的 数据类型 ❑5.处理器状态 ❑6.处理器模式 ❑7.内部寄存器 ❑8. 程序状态寄存器 ❑9.异常 ❑10.中断延迟 ❑11.复位 ❑12.存储器及存储器映射 I/O ❑13.寻址方式简介 ❑14.ARM7指令简介 ❑15.协处理器接口 ❑16.调试接口简介 ❑17.ETM接口简介

3.9异常 ·简介 只要正常的程序流被暂时中止,处理器就进入 异常模式。例如响应一个来自外设的中断。在处理 异常之前,ARM7TDMI内核保存当前的处理器状 态,这样当处理程序结束时可以恢复执行原来的程 序。 如果同时发生两个或更多异常,那么将按照固 定的顺序来处理异常,详见“异常优先级”部分

3.9 异常 • 简介 只要正常的程序流被暂时中止,处理器就进入 异常模式。例如响应一个来自外设的中断。在处理 异常之前,ARM7TDMI内核保存当前的处理器状 态,这样当处理程序结束时可以恢复执行原来的程 序。 如果同时发生两个或更多异常,那么将按照固 定的顺序来处理异常,详见“异常优先级”部分

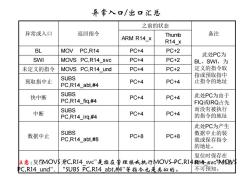

异常入口/出口汇总 之前的状态 异常或入口 返回指令 Thumb 备注 ARM R14_x R14_x BL MOV PC,R14 PC+4 PC+2 此处PC为 SWI MOVS PC,R14_svc PC+4 PC+2 BL,SWI,为 未定义的指令 MOVS PC,R14 und PC+4 PC+2 定义的指令取 指或预取指中 预取指中止 SUBS PC,R14 abt,#4 PC+4 PC+4 止指令的地址 快中断 SUBS PC,R14 fiq,#4 PC+4 PC+4 此处PC为由于 FIQ或RQ占先 而没有被执行 中断 SUBS PC,R14 irg,#4 PC+4 PC+4 的指令的地址 此处PC为产生 数据中止 SUBS 数据中止的装 PC,R14_abt,#8 PC+8 PC+8 载或保存指令 的地址。 复位时保存在 往意:复MOV5尤C,R145vc”是指在雀理模式执行MOVS PC,R14④6vcM@ PC,R14und、“SUBS PC,R14abt,4”等指令也是类似的。 不可预知

异常入口/出口汇总 异常或入口 返回指令 之前的状态 备注 ARM R14_x Thumb R14_x BL MOV PC,R14 PC+4 PC+2 此处PC为 BL,SWI,为 定义的指令取 指或预取指中 止指令的地址 SWI MOVS PC,R14_svc PC+4 PC+2 未定义的指令 MOVS PC,R14_und PC+4 PC+2 预取指中止 SUBS PC,R14_abt,#4 PC+4 PC+4 快中断 SUBS PC,R14_fiq,#4 PC+4 PC+4 此处PC为由于 FIQ或IRQ占先 而没有被执行 中断 的指令的地址 SUBS PC,R14_irq,#4 PC+4 PC+4 数据中止 SUBS PC,R14_abt,#8 PC+8 PC+8 此处PC为产生 数据中止的装 载或保存指令 的地址。 复位 无 — — 复位时保存在 R14_svc中的值 不可预知。 注意: “MOVS PC,R14_svc”是指在管理模式执行MOVS PC,R14指令。“MOVS PC,R14_und”、“SUBS PC,R14_abt,#4”等指令也是类似的

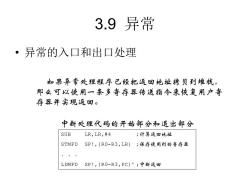

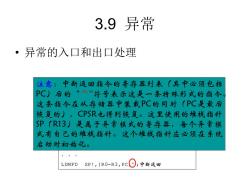

3.9异常 ·异常的入口和出口处理 如果异常处理程序已经把返回地址拷贝到堆栈, 那么可以使用一条多寄存器传送指令来恢复用户寄 存器并实现返回。 中断处理代码的开始部分和退出部分 SUB LR,LR,#4 ;计算返回地址 STMED SP!,{R0-R3,LR};保存使用到的寄存器 LDMFD SP!,{R0-R3,PC}N;中断返回

3.9 异常 • 异常的入口和出口处理 如果异常处理程序已经把返回地址拷贝到堆栈, 那么可以使用一条多寄存器传送指令来恢复用户寄 存器并实现返回。 SUB LR,LR,#4 ;计算返回地址 STMFD SP!,{R0-R3,LR} ;保存使用到的寄存器 . . . LDMFD SP!,{R0-R3,PC}^ ;中断返回 中断处理代码的开始部分和退出部分

3.9异常 ·异常的入口和出口处理 注意:中新返回指令的寺存器列表(其中必须包括 PC)后的 “人”特号表示这是一条特殊形式的指令。 这条指令在从存储器中装载PC的同时(PC是最后 恢复的),CPSR也得到恢复。这里使用的堆栈指针 SP(R13)是属于异常模式的寺存器,每个异常模 式有自己的堆栈指针。这个堆栈指针应必须在系统 启动时初始化。 LDMFD SP!,(RO-R3,PC 中断返回

如果异常处理程序已经把返回地址拷贝到堆栈, 那么可以使用一条多寄存器传送指令来恢复用户寄 存器并实现返回。 中断处理代码的开始部分和退出部分 3.9 异常 • 异常的入口和出口处理 SUB LR,LR,#4 ;计算返回地址 STMFD SP!,{R0-R3,LR} ;保存使用到的寄存器 . . . LDMFD SP!,{R0-R3,PC}^ ;中断返回 注意:中断返回指令的寄存器列表(其中必须包括 PC)后的“^”符号表示这是一条特殊形式的指令。 这条指令在从存储器中装载PC的同时(PC是最后 恢复的),CPSR也得到恢复。这里使用的堆栈指针 SP(R13)是属于异常模式的寄存器,每个异常模 式有自己的堆栈指针。这个堆栈指针应必须在系统 启动时初始化

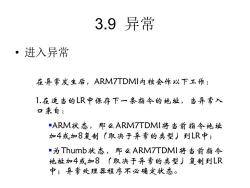

3.9异常 ·进入异常 在异常发生后,ARM7TDMI内核会作以下工作: 1.在适当的LR中保存下一条指令的地址,当异常入 口来自: ■ARM状态,那么ARM7TDMl将当前指令地址 加4或加8复制(取决于异常的类型)到LR中; ·为Thumb状态,那么,ARM7TDMl将当前指令 地址加4或加8(取决于异常的类型)复制到LR 中;异常处理器程序不必确定状态

3.9 异常 • 进入异常 在异常发生后,ARM7TDMI内核会作以下工作: 1.在适当的LR中保存下一条指令的地址,当异常入 口来自: ▪ARM状态,那么ARM7TDMI将当前指令地址 加4或加8复制(取决于异常的类型)到LR中; ▪为Thumb状态,那么ARM7TDMI将当前指令 地址加4或加8 (取决于异常的类型)复制到LR 中;异常处理器程序不必确定状态

3.9异常 ·进入异常 在异常发生后,ARM7TDMI内核会作以下工作: 2.将CPSR复制到适当的SPS中; 3.将CPSR模式位强制设置为与异常类型相对应的值; 4.强制PC从相关的异常向量处取指

3.9 异常 • 进入异常 在异常发生后,ARM7TDMI内核会作以下工作: 2.将CPSR复制到适当的SPSR中; 3. 将CPSR模式位强制设置为与异常类型相对应的值; 4.强制PC从相关的异常向量处取指

3.9异常 ·进入异常 ARM7TDMI内核在中断异常时置位中断禁止标 志,这样可以防止不受控制的异常嵌套。 注:异常总是在ARM状态中进行处理。当处理器处 于Thumb状态时发生了异常,在异常向量地址装入 PC时,会自动切换到ARM状态

ARM7TDMI内核在中断异常时置位中断禁止标 志,这样可以防止不受控制的异常嵌套。 注:异常总是在ARM状态中进行处理。当处理器处 于Thumb状态时发生了异常,在异常向量地址装入 PC时,会自动切换到ARM状态。 3.9 异常 • 进入异常

3.9异常 ·退出异常 当异常结束时,异常处理程序必须: 1.将LR中的值减去偏移量后存入PC,偏移量根据异 常的类型而有所不同; 2.将SPSR的值复制回CPSR; 3.清零在入口置位的中断禁止标志。 注:恢复CPSR的动作会将T、F和l位自动恢复为异 常发生前的值

当异常结束时,异常处理程序必须: 1.将LR中的值减去偏移量后存入PC,偏移量根据异 常的类型而有所不同; 2.将SPSR的值复制回CPSR; 3.清零在入口置位的中断禁止标志。 注:恢复CPSR的动作会将T、F和I位自动恢复为异 常发生前的值。 3.9 异常 • 退出异常

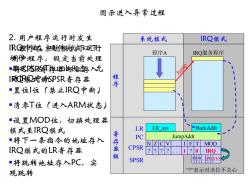

图示进入异常过程 2.用户程序运行时发生 系统模式 IRQ模式 IRG⑤序触运行 程序A RQ服务程序 确作程序,假定当前处理 ■粥状态?闲熔族入允 Jump I奶视式都PSR寄存器 ■置位l位(禁止IRQ中断) ■清零T位(进入ARM状态) ■设置M○D位,切换处理器 模式至IRQ模式 LR LR sys BackAddr ■将下一条指令的地址存入 寄存器 PC JumpAddr N ZC V MOD IRQ模式的LR寄存器 CPSR ???? .1?0 IRQ ■将跳转地址存入PC,实 SPSR PsYs 现跳转 ?”表示对该位不关心

程序A IRQ服务程序 系统模式 IRQ模式 程 序 寄 存 器 组 图示进入异常过程 1. 程序在系统模式下运行 用户程序,假定当前处理 器状态为Thumb状态、允 许IRQ中断; 2. 用户程序运行时发生 IRQ中断,硬件完成以下 动作: LR_sys SPSR_irq LR LR_irq PC CPSR SPSR ? ? ? ? . . . 0 ? 1 SYS N Z C V . . . I F T MOD ▪置位I位(禁止IRQ中断) ▪清零T位(进入ARM状态) ▪设置MOD位,切换处理器 模式至IRQ模式 ▪将下一条指令的地址存入 IRQ模式的LR寄存器 ▪将CPSR寄存器内容存入 IRQ模式的SPSR寄存器 ▪将跳转地址存入PC,实 现跳转 ? ? ? ? . . . 1 ? 0 IRQ BackAddr JumpAddr ????. . .0?1SYS “?”表示对该位不关心

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第04讲 数据流建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第03讲 门级与结构建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第02讲 Verilog HDL语言基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第01讲 HDL语言概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(3/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(2/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(1/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 5Digital Transmission Through Bandlimited Channels.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multidimensional Signals).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multiamplitude Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Binary Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Pulse Amplitude Modulation、Pulse Code Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Preview、Measure of Information、Quantization).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc