《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第02讲 Verilog HDL语言基础

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 第二讲Verilog HDL语言基础 内容: 语言基本词法 冬主要数据类型 ·参数 ”常用系统任务和函数 冬常用编译指令 冬表达式与运算符 。模块与端口

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 第 二讲 Verilog HDL语言基础 内容: ❖ 语言基本词法 ❖ 主要数据类型 ❖ 参数 ❖ 常用系统任务和函数 ❖ 常用编译指令 ❖ 表达式与运算符 ❖ 模块与端口

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 语言基本词法 Verilog中的基本词法约定与C语言类似。包含注释、分隔符、数字、 字符串、标识符和关键字。 Verilog是自由格式,即语句可以在一行内编写,也可跨行编写,用 分号分隔。由空格(b)、制表符(t)和换行符组成空白符,在文本 中起一个分隔符的作用,在编译时被忽略。例: initial begin Top=3'b001;#2 Top 3'b0l1;end 和下面的程序一样: initial begin //单行注释,与C语言一致 Top=3'b001; #2Top=3'b011 /*多行注释, 与C语言一致*/ end

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 语言基本词法 ❖ Verilog中的基本词法约定与C语言类似。包含注释、分隔符、数字、 字符串、标识符和关键字。 ❖ Verilog是自由格式,即语句可以在一行内编写,也可跨行编写,用 分号分隔。由空格(\b)、制表符(\t)和换行符组成空白符,在文本 中起一个分隔符的作用,在编译时被忽略。例: initial begin Top = 3'b001; #2 Top = 3'b011; end 和下面的程序一样: initial begin // 单行注释,与C 语言一致 Top = 3'b001; #2 Top = 3'b011 /* 多行注释, 与C 语言一致 */ end

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 标识符 冬标识符必须以英语字母(a-z,A-Z)起头,或者用下 横线符()起头。其中可以包含数字、$符和下横 线符。 标识符最长可以达到1023个字符。 冬模块名、端口名和实例名都是标识符。 Verilog语言是大小写敏感的,因此sel和SEL是两 个不同的标识符

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 标识符 ❖ 标识符必须以英语字母(a-z, A-Z)起头,或者用下 横线符( _ )起头。其中可以包含数字、$符和下横 线符。 ❖ 标识符最长可以达到1023个字符。 ❖ 模块名、端口名和实例名都是标识符。 ❖ Verilog语言是大小写敏感的,因此sel 和 SEL 是两 个不同的标识符

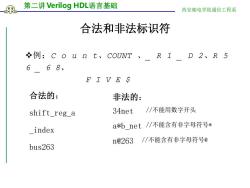

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 合法和非法标识符 例:cou n t、COUNT、_R1-D2、R5 668、 F I VE S 合法的: 非法的: shift reg a 34net /不能用数字开头 index a*bnet/不能含有非字母符号* n@263/不能含有非字母符号@ bus263

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 合法和非法标识符 合法的: shift_reg_a _index bus263 非法的: 34net //不能用数字开头 a*b_net //不能含有非字母符号* n@263 //不能含有非字母符号@ ❖例:C o u n t、COUNT 、_ R 1 _ D 2、R 5 6 _ 6 8、 F I V E $

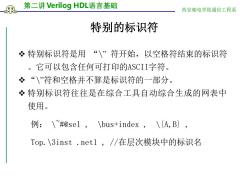

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 特别的标识符 冬特别标识符是用“”符开始,以空格符结束的标识符 。它可以包含任何可打印的ASCII字符。 冬“”符和空格并不算是标识符的一部分。 冬特别标识符往往是在综合工具自动综合生成的网表中 使用。 例:1#@sel,bus+index,\{A,B}, Top.3inst.net1,/在层次模块中的标识名

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 特别的标识符 ❖ 特别标识符是用 “\” 符开始,以空格符结束的标识符 。它可以包含任何可打印的ASCII字符。 ❖ “\”符和空格并不算是标识符的一部分。 ❖ 特别标识符往往是在综合工具自动综合生成的网表中 使用。 例: \~#@sel , \bus+index , \{A,B} , Top.\3inst .net1 , //在层次模块中的标识名

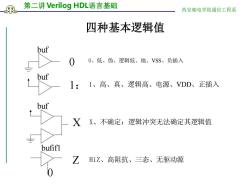

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 四种基本逻辑值 buf 0、低、伪、逻辑低、地、VSS、负插入 1:1、高、真、逻辑高、电源、VDD、正插入 XX、不确定:逻辑冲突无法确定其逻辑值 bufifl Z HZ、高阻抗、三态、无驱动源

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 四种基本逻辑值 0、低、伪、逻辑低、地、VSS、负插入 0 1: X Z 0 buf buf buf bufif1 1、高、真、逻辑高、电源、VDD、正插入 X、不确定:逻辑冲突无法确定其逻辑值 HiZ、高阻抗、三态、无驱动源

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 常量 Verilog HDL中有三类常量: 1)整型 2)实数型 3)字符串型 冬下划线符号()可以随意用在整数或实数中, 它们就数量本身没有意义。它们能用来提高易读 性

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 常量 ❖ Verilog HDL中有三类常量: 1) 整型 2) 实数型 3) 字符串型 ❖ 下划线符号( _)可以随意用在整数或实数中, 它们就数量本身没有意义。它们能用来提高易读 性

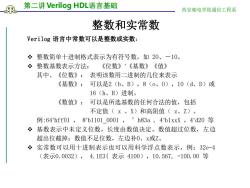

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 整数和实常数 Verilog语言中常数可以是整数或实数: 整数简单十进制格式表示为有符号数,如20、一10。 冬整数基数表示方法: 《位数》’《基数》《值》 其中、《位数》: 表明该数用二进制的几位来表示 《基数》:可以是2(b、B),8(o、0),10(d、D)或 16(h、H)进制。 《数值》: 可以是所选基数的任何合法的值,包括 不定值(x、X)和高阻值(z、Z)。 例:64hff01,8b11010001,’h83a,4b1xxX,4d20等 基数表示中未定义位数,长度由数值决定。数值超过位数,左边 超出位截掉;数值不足位数,左边补0、x或Z。 。实常数可以用十进制表示也可以用科学浮点数表示,例:32-4 (表示0.0032),4.1E3(表示4100),10.567,-100.00等

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 整数和实常数 Verilog 语言中常数可以是整数或实数: ❖ 整数简单十进制格式表示为有符号数,如 20、-10。 ❖ 整数基数表示方法: 《位数》’《基数》《值》 其中、《位数》: 表明该数用二进制的几位来表示 《基数》: 可以是2(b、B),8(o、O),10(d、D)或 16(h、H)进制。 《数值》: 可以是所选基数的任何合法的值,包括 不定值( x 、X)和高阻值( z、Z)。 例:64’hff01 , 8’b1101_0001 , ’h83a , 4’b1xxX ,4’d20 等 ❖ 基数表示中未定义位数,长度由数值决定。数值超过位数,左边 超出位截掉;数值不足位数,左边补0、x或Z。 ❖ 实常数可以用十进制表示也可以用科学浮点数表示,例:32e-4 (表示0.0032), 4.1E3( 表示 4100),10.567, -100.00 等

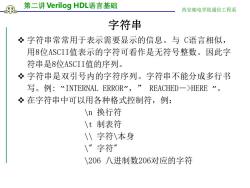

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 字符串 必字符串常常用于表示需要显示的信息。与C语言相似, 用8位ASCII值表示的字符可看作是无符号整数。因此字 符串是8位ASCII值的序列。 冬字符串是双引号内的字符序列。字符串不能分成多行书 写。例:INTERNAL ERROR",”REACHED一>HERE"。 在字符串中可以用各种格式控制符,例: n换行符 \t制表符 字符1本身 \”字符 1206八进制数206对应的字符

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 字符串 ❖ 字符串常常用于表示需要显示的信息。与 C语言相似, 用8位ASCII值表示的字符可看作是无符号整数。因此字 符串是8位ASCII值的序列。 ❖ 字符串是双引号内的字符序列。字符串不能分成多行书 写。例: “INTERNAL ERROR” , ” REACHED->HERE ” 。 ❖ 在字符串中可以用各种格式控制符,例: \n 换行符 \t 制表符 \\ 字符\本身 \" 字符" \206 八进制数206对应的字符

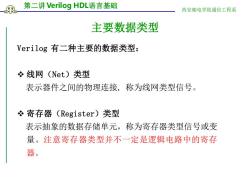

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 主要数据类型 Verilog有二种主要的数据类型: 线网(Net)类型 表示器件之间的物理连接,称为线网类型信号。 寄存器(Register)类型 表示抽象的数据存储单元,称为寄存器类型信号或变 量。注意寄存器类型并不一定是逻辑电路中的寄存 器

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 主要数据类型 Verilog 有二种主要的数据类型: ❖ 线网(Net)类型 表示器件之间的物理连接, 称为线网类型信号。 ❖ 寄存器(Register)类型 表示抽象的数据存储单元,称为寄存器类型信号或变 量。注意寄存器类型并不一定是逻辑电路中的寄存 器

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第01讲 HDL语言概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(3/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(2/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 6 Binary Modulated Bandpass Signaling(1/3).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 5Digital Transmission Through Bandlimited Channels.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multidimensional Signals).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Multiamplitude Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 4 Baseband Digital Transmission(Binary Signal Transmission).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Pulse Amplitude Modulation、Pulse Code Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Preview、Measure of Information、Quantization).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Transmitters and Receivers.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Frequency Modulation、Phase Modulation).ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 7 Spread Spectrum Communication Systems.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(SSB – AM).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Conventional AM).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(AM,Amplitude Modulation).ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 1 Basic Matlab.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第1章 matlab基础知识.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第3章 图形处理与simulink仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第2章 matlab语言入门.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第03讲 门级与结构建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第04讲 数据流建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt