《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 数字系统设计与FPGA应用

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 数字系统设计与FPGA应用

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 第一讲数字系统与FPGA设计概述 内容: 。数字系统概述 可编程逻辑器件概述 ·数字系统设计方法 冬FPGA设计流程

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 第 一讲 数字系统与FPGA设计概述 内容: ❖ 数字系统概述 ❖ 可编程逻辑器件概述 ❖ 数字系统设计方法 ❖ FPGA设计流程

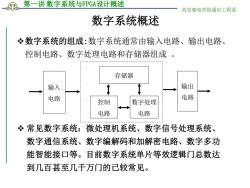

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 数字系统概述 数字系统的组成:数字系统通常由输入电路、输出电路、 控制电路、数字处理电路和存储器组成。 存储器 输入 输出 电路 电路 控制 数字处理 电路 电路 冬常见数字系统:微处理机系统、 数字信号处理系统、 数字通信系统、数字编解码和加解密电路、数字多功 能智能接口等。目前数字系统单片等效逻辑门总数达 到几百甚至几千万门的已较常见

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 数字系统概述 ❖ 常见数字系统:微处理机系统、数字信号处理系统、 数字通信系统、数字编解码和加解密电路、数字多功 能智能接口等。目前数字系统单片等效逻辑门总数达 到几百甚至几千万门的已较常见。 存储器 ❖数字系统的组成:数字系统通常由输入电路、输出电路、 控制电路、数字处理电路和存储器组成 。 控制 电路 数字处理 电路 输入 电路 输出 电路

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 数字系统实现方法 必 通用集成电路。如:74系列,4000系列等,电路体积 大、重量大、功耗大、可靠性低。(70、80年代主流) 必 专用集成电路ASIC(Application Specific Integrated Circuits),如:Modem,MP3 decoder等。(90年代盛 行,现在大规模产品中继续使用) 必 可编程逻辑阵列(Programmable Logic Device)。如: Xilinx的spartan.系列,Alteral的Cyclone系列。(现在 逐步蚕食ASIC的低端市场,并将成为一种主流方法) 通用微处理器、DSP。如8051单片机、ARM32位MCU, TMS320C5x系列DSP等。(80年代,现在仍为一种主 流方法) 混合使用各种器件,发挥各自的优势。(发展趋势)

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 数字系统实现方法 ❖ 通用集成电路。 如:74 系列 ,4000系列等,电路体积 大、重量大、功耗大、可靠性低。(70、80年代主流) ❖ 专用集成电路ASIC(Application Specific Integrated Circuits),如:Modem , MP3 decoder等。(90年代盛 行,现在大规模产品中继续使用) ❖ 可编程逻辑阵列( Programmable Logic Device)。如: Xilinx的spartan系列,Altera的Cyclone系列。(现在 逐步蚕食ASIC的低端市场,并将成为一种主流方法) ❖ 通用微处理器、DSP 。如 8051单片机、ARM32位MCU, TMS320C5x系列DSP等。 (80年代,现在仍为一种主 流方法) ❖ 混合使用各种器件,发挥各自的优势。(发展趋势)

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑实验数字系统 r层实的区 出用 Mars-EDA-S实验主板 013a0

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑实验数字系统

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑器件的发展概况 当今社会是数字化社会,数字集成电路应用非常广泛, 其发展从电子管、晶体管、SSI、MSI、LSI、VLSI到 ULSI,其规模几乎平均每18个月翻一番(摩尔定律)。 冬ASIC是专门为某一应用领域或某一专门用户需要而设 计制造的集成电路。特点:量产成本低,但开发周期长, 投入大,风险大,特别是到0.18微米后,投片费大增。 冬可编程逻辑器件PLD(Programmable Logic Device)是 从可编程逻辑阵列和ASIC中发展出来的新器件。特点: 开发周期短,设计修改灵活,无投片费,量产成本较高

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 ❖ 当今社会是数字化社会, 数字集成电路应用非常广泛, 其发展从电子管、 晶体管、SSI、 MSI、 LSI、VLSI到 ULSI, 其规模几乎平均每18个月翻一番(摩尔定律)。 ❖ ASIC 是专门为某一应用领域或某一专门用户需要而设 计制造的集成电路。特点:量产成本低,但开发周期长, 投入大,风险大,特别是到0.18微米后,投片费大增。 ❖ 可编程逻辑器件PLD(Programmable Logic Device)是 从可编程逻辑阵列和ASIC中发展出来的新器件。特点: 开发周期短,设计修改灵活,无投片费,量产成本较高。 可编程逻辑器件的发展概况

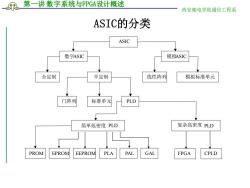

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 ASIC的分类 ASIC 数字ASIC 模ASIC 全定制 半定制 线性阵列 模拟标准单元 门阵列 标准单元 PLD 简单低密度PLD 复杂高密度PLD PROM EPROM EEPROM PLA PAL GAL FPGA CPLD

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 ASIC的分类 PROM EPROM EEPROM PLA PAL GAL FPGA CPLD 简单低密度 PLD 复杂高密度 PLD 门阵列 标准单元 PLD 全定制 半定制 线性阵列 模拟标准单元 数字ASIC 模拟ASIC ASIC

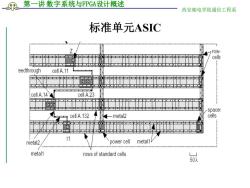

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 标准单元ASIC roW- cells eedthrough cell A.11 ☒☒ cell A.14 cell A.23 ☒☒ spacer cell A.132 metal2 cells 11 metal2 power cell metal14 metal1 rows of standard cells L 501

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 标准单元ASIC

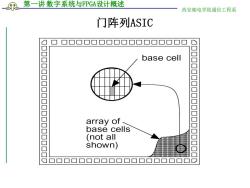

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 门阵列ASIC 口口口口口口口口口口口口□□口口□ base cell 口 ▣ array of base cells (not all shown)

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 门阵列ASIC

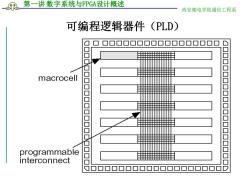

第一讲数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑器件(PLD) macrocell 口口 programmable 口口 interconnect 口口 ▣口▣▣口▣口▣▣口▣口▣口口▣口口口口)

第一讲 数字系统与FPGA设计概述 西安邮电学院通信工程系 可编程逻辑器件(PLD)

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(1/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第4章 ARM7TDMI(-S)指令系统.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第3章 ARM7体系结构(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第2章 嵌入式系统工程设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第1章 嵌入式系统概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第08讲 可综合设计.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第07讲 综合建模与仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第06讲 行为建模(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第05讲 行为建模(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第04讲 数据流建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第03讲 门级与结构建模.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第02讲 Verilog HDL语言基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)Verilog HDL数字系统设计与综合实验——第01讲 HDL语言概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)Verilog HDL数字系统设计与综合实验指导书(HDL语言硬件设计实验指导书).doc

- 《通信原理实验》课程教学资源(实验指导)基于System Generator的通信系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)嵌入式系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)数字系统与FPGA设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)高级软件无线电系统实验指导书.doc

- 《信号与系统》课程教学大纲 signals and systems.pdf