《通信原理实验》课程教学资源(实验指导)基于System Generator的通信系统设计实验指导书

西安邮电大学通信基础实验教学中心 现代通信综合实验系统 实验指导书 一一System Generator for DSP 1/45

西安邮电大学 通信基础实验教学中心 1 / 45 现代通信综合实验系统 实验指导书 ——System Generator for DSP

西安邮电大学通信基础实验教学中心 目录 第一章、 AD、DA转换芯片介绍 .3 1.1 AD芯片的型号及时序 3 1.2 DA芯片的型号及时序 .6 第二章、 系统详细设计.。 10 2.1 工程文件的建立.。 10 2.2 基本单元一一System Generator参数设置. 10 2.3 主要模块设计 13 2.3.1 AD时序设计. 13 2.3.2 DA时序设计 19 2.3.3 信源与载波设计 23 2.3.4 低通滤波器设计. 26 2.4 详细设计流程.。 30 2.4.1 调制部分. 30 2.4.2 解调部分. 36 2.4.3 系统仿真. 38 2.4.4 生成下载文件. .39 2.4.5 板上验证 40 2.4.6 Fash配置 41 2.4.7 引脚约束。 42 附录管脚配置. .44 2/45

西安邮电大学 通信基础实验教学中心 2 / 45 目录 第一章、 AD、DA 转换芯片介绍. 3 1.1 AD 芯片的型号及时序. 3 1.2 DA 芯片的型号及时序. 6 第二章、 系统详细设计. 10 2.1 工程文件的建立. 10 2.2 基本单元——System Generator 参数设置. 10 2.3 主要模块设计. 13 2.3.1 AD 时序设计. 13 2.3.2 DA 时序设计. 19 2.3.3 信源与载波设计. 23 2.3.4 低通滤波器设计. 26 2.4 详细设计流程. 30 2.4.1 调制部分. 30 2.4.2 解调部分. 36 2.4.3 系统仿真. 38 2.4.4 生成下载文件. 39 2.4.5 板上验证. 40 2.4.6 Flash 配置 . 41 2.4.7 引脚约束. 42 附录 管脚配置. 44

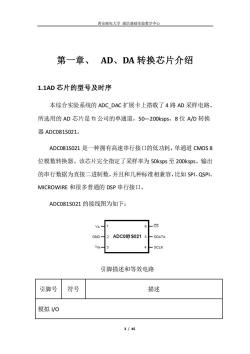

西安邮电大学通信基础实验教学中心 第一章、AD、DA转换芯片介绍 1.1AD芯片的型号及时序 本综合实验系统的ADC DAC扩展卡上搭载了4路AD采样电路。 所选用的AD芯片是TI公司的单通道,50-200ksps,8位A/D转换 器ADC081S021。 ADC081S021是一种拥有高速串行接口的低功耗,单通道CMOS8 位模数转换器。该芯片完全指定了采样率为50ksps至200ksps。输出 的串行数据为直接二进制数,并且和几种标准相兼容,比如SPL、QSPL、 MICROWIRE和很多普通的DSP串行接口。 ADC081S021的接线图为如下: VA -cs GND- 2 ADC081S021 5 SDATA VIN SCLK 引脚描述和等效电路 引脚号 符号 描述 模拟/o 3/45

西安邮电大学 通信基础实验教学中心 3 / 45 第一章、 AD、DA 转换芯片介绍 1.1AD 芯片的型号及时序 本综合实验系统的 ADC_DAC 扩展卡上搭载了 4 路 AD 采样电路。 所选用的 AD 芯片是 TI 公司的单通道,50—200ksps,8 位 A/D 转换 器 ADC081S021。 ADC081S021 是一种拥有高速串行接口的低功耗,单通道 CMOS 8 位模数转换器。该芯片完全指定了采样率为 50ksps 至 200ksps。输出 的串行数据为直接二进制数,并且和几种标准相兼容,比如 SPI、QSPI、 MICROWIRE 和很多普通的 DSP 串行接口。 ADC081S021 的接线图为如下: 引脚描述和等效电路 引脚号 符号 描述 模拟 I/O

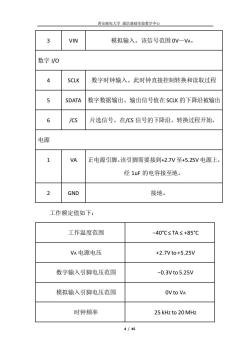

西安邮电大学通信基础实验教学中心 3 VIN 模拟输入。该信号范围OV一VA。 数字/o 4 SCLK 数字时钟输入。此时钟直接控制转换和读取过程 5 SDATA 数字数据输出。输出信号值在SCLK的下降沿被输出 6 /cs 片选信号。在/CS信号的下降沿,转换过程开始。 电源 1 VA 正电源引脚。该引脚需要接到+2.7V至+5.25V电源上, 经1uF的电容接至地。 2 GND 接地。 工作额定值如下: 工作温度范围 -40°C≤TA≤+85C VA电源电压 +2.7Vto+5.25V 数字输入引脚电压范围 -0.3Vto5.25V 模拟输入引脚电压范围 OV to VA 时钟频率 25 kHz to 20 MHz 4/45

西安邮电大学 通信基础实验教学中心 4 / 45 3 VIN 模拟输入。该信号范围 0V—VA。 数字 I/O 4 SCLK 数字时钟输入。此时钟直接控制转换和读取过程 5 SDATA 数字数据输出。输出信号值在 SCLK 的下降沿被输出 6 /CS 片选信号。在/CS 信号的下降沿,转换过程开始。 电源 1 VA 正电源引脚。该引脚需要接到+2.7V 至+5.25V 电源上, 经 1uF 的电容接至地。 2 GND 接地。 工作额定值如下: 工作温度范围 −40°C ≤ TA ≤ +85°C VA 电源电压 +2.7V to +5.25V 数字输入引脚电压范围 −0.3V to 5.25V 模拟输入引脚电压范围 0V to VA 时钟频率 25 kHz to 20 MHz

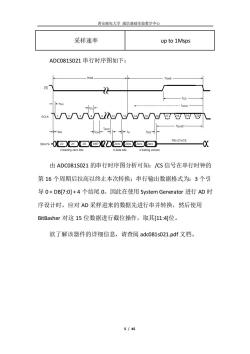

西安邮电大学通信基础实验教学中心 采样速率 up to 1Msps ADC081S021串行时序图如下: Hold Track cs tcs thntonhpi SDATA2z2DoQ《2@⊙o《2e⊙2@o TRI-STATE X 3 leading zero bits 8 data bits 4 trailing zeroes 由ADC081S021的串行时序图分析可知:/CS信号在串行时钟的 第16个周期后拉高以终止本次转换:串行输出数据格式为:3个引 导0+DB[7:0]+4个结尾0。因此在使用System Generator进行AD时 序设计时,应对AD采样进来的数据先进行串并转换,然后使用 BitBasher对这15位数据进行截位操作,取其[11:4位。 欲了解该器件的详细信息,请查阅adc081s021.pdf文档。 5/45

西安邮电大学 通信基础实验教学中心 5 / 45 采样速率 up to 1Msps ADC081S021 串行时序图如下: 由 ADC081S021 的串行时序图分析可知:/CS 信号在串行时钟的 第 16 个周期后拉高以终止本次转换;串行输出数据格式为:3 个引 导 0 + DB[7:0] + 4 个结尾 0。因此在使用 System Generator 进行 AD 时 序设计时,应对 AD 采样进来的数据先进行串并转换,然后使用 BitBasher 对这 15 位数据进行截位操作,取其[11:4]位。 欲了解该器件的详细信息,请查阅 adc081s021.pdf 文档

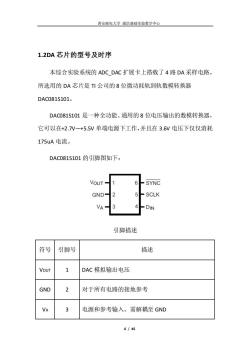

西安邮电大学通信基础实验教学中心 1.2DA芯片的型号及时序 本综合实验系统的ADC DAC扩展卡上搭载了4路DA采样电路。 所选用的DA芯片是T1公司的8位微功耗轨到轨数模转换器 DAC081S101。 DAC081S101是一种全功能、通用的8位电压输出的数模转换器, 它可以在+2.7V一+5.5V单端电源下工作,并且在3.6V电压下仅仅消耗 175uA电流。 DAC081S101的引脚图如下: VOUT SYNC GND- 2 5 SCLK VA- 3 -DIN 引脚描述 符号 引脚号 描述 VOUT 1 DAC模拟输出电压 GND 2 对于所有电路的接地参考 VA 3 电源和参考输入。需解耦至GND 6145

西安邮电大学 通信基础实验教学中心 6 / 45 1.2DA 芯片的型号及时序 本综合实验系统的 ADC_DAC 扩展卡上搭载了 4 路 DA 采样电路。 所选用的 DA 芯片是 TI 公司的 8 位微功耗轨到轨数模转换器 DAC081S101。 DAC081S101 是一种全功能、通用的 8 位电压输出的数模转换器, 它可以在+2.7V—+5.5V 单端电源下工作,并且在 3.6V 电压下仅仅消耗 175uA 电流。 DAC081S101 的引脚图如下: 引脚描述 符号 引脚号 描述 VOUT 1 DAC 模拟输出电压 GND 2 对于所有电路的接地参考 VA 3 电源和参考输入。需解耦至 GND

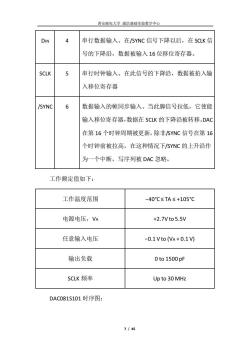

西安邮电大学通信基础实验教学中心 DIN 4 串行数据输入。在/SYNC信号下降以后,在SCLK信 号的下降沿,数据被输入16位移位寄存器。 SCLK 5 串行时钟输入。在此信号的下降沿,数据被拍入输 入移位寄存器 /SYNC 6 数据输入的帧同步输入。当此脚信号拉低,它使能 输入移位寄存器,数据在SCK的下降沿被转移。DAC 在第16个时钟周期被更新,除非/SYNC信号在第16 个时钟前被拉高,在这种情况下/SYNC的上升沿作 为一个中断,写序列被DAC忽略。 工作额定值如下: 工作温度范围 -40C≤TA≤+105C 电源电压,Va +2.7Vto5.5V 任意输入电压 -0.1Vto(VA+0.1V) 输出负载 0 to 1500 pF SCLK频率 Up to 30 MHz DAC081S101时序图: 7/45

西安邮电大学 通信基础实验教学中心 7 / 45 DIN 4 串行数据输入。在/SYNC 信号下降以后,在 SCLK 信 号的下降沿,数据被输入 16 位移位寄存器。 SCLK 5 串行时钟输入。在此信号的下降沿,数据被拍入输 入移位寄存器 /SYNC 6 数据输入的帧同步输入。当此脚信号拉低,它使能 输入移位寄存器,数据在 SCLK 的下降沿被转移。DAC 在第 16 个时钟周期被更新,除非/SYNC 信号在第 16 个时钟前被拉高,在这种情况下/SYNC 的上升沿作 为一个中断,写序列被 DAC 忽略。 工作额定值如下: 工作温度范围 −40°C ≤ TA ≤ +105°C 电源电压,VA +2.7V to 5.5V 任意输入电压 −0.1 V to (VA + 0.1 V) 输出负载 0 to 1500 pF SCLK 频率 Up to 30 MHz DAC081S101 时序图:

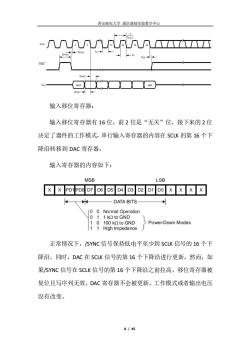

西安邮电大学通信基础实验教学中心 SYNC DN 输入移位寄存器: 输入移位寄存器有16位。前2位是“无关”位,接下来的2位 决定了器件的工作模式,串行输入寄存器的内容在SCLK的第16个下 降沿转移到DAC寄存器。 输入寄存器的内容如下: MSB LSB xX PD1PD0 D7 D6 D5 D4 2D1 DATA BITS 00 Normal Operation 0 1 1 ko to GND 1 0 100 k to GND Power-Down Modes 1 1 High Impedance 正常情况下,/SYNC信号保持低电平至少到SCLK信号的16个下 降沿,同时,DAC在SCK信号的第16个下降沿进行更新。然而,如 果/SYNC信号在SCLK信号的第16个下降沿之前拉高,移位寄存器被 复位且写序列无效。DAC寄存器不会被更新,工作模式或者输出电压 没有改变。 8/45

西安邮电大学 通信基础实验教学中心 8 / 45 输入移位寄存器: 输入移位寄存器有 16 位。前 2 位是“无关”位,接下来的 2 位 决定了器件的工作模式,串行输入寄存器的内容在 SCLK 的第 16 个下 降沿转移到 DAC 寄存器。 输入寄存器的内容如下: 正常情况下,/SYNC 信号保持低电平至少到 SCLK 信号的 16 个下 降沿,同时,DAC 在 SCLK 信号的第 16 个下降沿进行更新。然而,如 果/SYNC 信号在 SCLK 信号的第 16 个下降沿之前拉高,移位寄存器被 复位且写序列无效。DAC 寄存器不会被更新,工作模式或者输出电压 没有改变

西安邮电大学通信基础实验教学中心 在System Generator的设计中,为了满足信号输出时经过并串转 换后的时序要求,对DA部分的DN信号采取了组数操作,即在并串 转换前的8位数据高位添加4位0,低位添加20位0,同时/SYNC信 号保持低电平到SCLK信号的第32个下降沿。 欲了解该器件的详细信息,请查阅dac081s101.pdf文档。 9/45

西安邮电大学 通信基础实验教学中心 9 / 45 在 System Generator 的设计中,为了满足信号输出时经过并串转 换后的时序要求,对 DA 部分的 DIN 信号采取了组数操作,即在并串 转换前的 8 位数据高位添加 4 位 0,低位添加 20 位 0,同时/SYNC 信 号保持低电平到 SCLK 信号的第 32 个下降沿。 欲了解该器件的详细信息,请查阅 dac081s101.pdf 文档

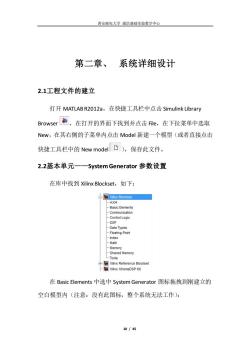

西安邮电大学通信基础实验教学中心 第二章、系统详细设计 2.1工程文件的建立 打开MATLAB R2012a,在快捷工具栏中点击Simulink Library Browser 在打开的界面下找到并点击File,在下拉菜单中选取 New,在其右侧的子菜单内点击Model新建一个模型(或者直接点击 快捷工具栏中的New model),保存此文件。 2.2基本单元一一System Generator参数设置 在库中找到Xilinx Blockset,如下: 白-Xilinx Blockset -AX04 -Basic Elements -Communication -Control Logic DSP -Data Types Floating-Point -Index -Math -Memory Shared Memory LTools Xilinx Reference Blockset Xilinx XtremeDSP Kit 在Basic Elements中选中System Generator图标拖拽到刚建立的 空白模型内(注意:没有此图标,整个系统无法工作): 10/45

西安邮电大学 通信基础实验教学中心 10 / 45 第二章、 系统详细设计 2.1工程文件的建立 打开 MATLAB R2012a,在快捷工具栏中点击 Simulink Library Browser ,在打开的界面下找到并点击 File,在下拉菜单中选取 New,在其右侧的子菜单内点击 Model 新建一个模型(或者直接点击 快捷工具栏中的 New model ),保存此文件。 2.2基本单元——System Generator 参数设置 在库中找到 Xilinx Blockset,如下: 在 Basic Elements 中选中 System Generator 图标拖拽到刚建立的 空白模型内(注意:没有此图标,整个系统无法工作):

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程教学资源(实验指导)Verilog HDL数字系统设计与综合实验指导书(HDL语言硬件设计实验指导书).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)MATLAB与通信仿真实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)CDMA移动通信系统实验指导书.doc

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案(非通工专业).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)通信原理实验电子教案.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器TDS1&2000使用.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)示波器原理及其使用——示波器应用基本知识(以泰克示波器基本功能为基础).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第06讲 数字系统设计原则与设计实例.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第05讲 数字系统设计的实现与验证.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第04讲 同步数字系统设计基础.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第03讲 数字系统设计的基础知识(2/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第02讲 数字系统设计的基础知识(1/2).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)数字系统设计与FPGA应用实验——第01讲 数字系统与FPGA设计概述.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第8章 嵌入式系统开发平台、数据队列、串口驱动、MODEM接口模块、I2C总线模块、SPI总线模块.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第7章 μC/OS-II简介、移植规划、移植μC/OS-II、移植代码应用到LPC2000.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第6章 最小系统、片内外设、总线接口、其它外设.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(4/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(3/4).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)嵌入式系统设计实验——第5章 LPC2000系列ARM(2/4).ppt

- 《通信原理实验》课程教学资源(实验指导)嵌入式系统设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)数字系统与FPGA设计实验指导书.doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(上).doc

- 《通信原理实验》课程教学资源(实验指导)通信原理实验指导书(下).doc

- 《通信原理实验》课程教学资源(实验指导)高级软件无线电系统实验指导书.doc

- 《信号与系统》课程教学大纲 signals and systems.pdf

- 《电工学》课程教学大纲 Electrical Engineering.pdf

- 《电工学》课程教学大纲(电工技术 The teaching outline of Electrical Technology).pdf

- 《电工学》课程授课教案(讲义)可编程控制器(PLC)实验——入门篇.doc

- 《电工学》课程授课教案(讲义)可编程控制器及其应用(关于西门子S7-200可编程控制器).doc

- 《电工学》课程教学资源(PPT课件)第04章 非正弦周期信号电路.ppt

- 《电工学》课程教学资源(PPT课件)第01章 直流电路.ppt

- 《电工学》课程教学资源(PPT课件)第02章 电路的暂态分析.ppt

- 《电工学》课程教学资源(PPT课件)第03章 单相交流电路.ppt

- 《电工学》课程教学资源(PPT课件)第08章 低压电器及继电接触器控制.ppt

- 《电工学》课程教学资源(PPT课件)第06章 磁路与变压器.ppt

- 《电工学》课程教学资源(PPT课件)第05章 三相交流电路.ppt

- 《电工学》课程教学资源(PPT课件)第07章 电动机.ppt

- 《电工学》课程教学资源(PPT课件)第09章 可编程控制器及其应用.ppt

- 《电工学》课程PPT教学课件(电子技术)第03章 场效应晶体管及其放大电路.ppt