江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.2 编码器与译码器 1 编码器

编码器(Encoder)的概念与分类 编码:赋予二进制代码特定含义的过程称为编码。 如:8421BCD码中用1000表示数字8 编码器:具有编码功能的逻辑电路。 编码器的逻辑功能:能将每一组输入信息变换为相 应二进制的代码输出。 •如4线-2线编码器:将输入的4个状态分别编成 4个2位二进制数码输出; •如8-3编码器:将输入的8个状态分别编成8个 3位二进制数码输出; 如BCD编码器:将10个输入分别编成10个4位 8421BCD码输出

编码器 (Encoder)的概念与分类 编码:赋予二进制代码特定含义的过程称为编码。 如:8421BCD码中用1000表示数字8 编码器:具有编码功能的逻辑电路。 编码器的逻辑功能:能将每一组输入信息变换为相 应二进制的代码输出。 •如4线-2线编码器:将输入的4个状态分别编成 4个2位二进制数码输出; •如8-3编码器:将输入的8个状态分别编成8个 3位二进制数码输出; •如BCD编码器:将10个输入分别编成10个4位 8421BCD码输出

编码器(Encoder)的概念与分类 编码器的分类: 普通编码器 优先编码器 普通编码器:任何时候只允许一个编码输入信号有 效,否则输出就会发生混乱。 优先编码器:允许同时输入两个以上的有效编码信 号。当同时输入几个有效编码信号时,优先编码器 能按预先设定的优先级别,只对其中优先权最高的 一个进行编码

编码器的分类: 普通编码器:任何时候只允许一个编码输入信号有 效,否则输出就会发生混乱。 优先编码器:允许同时输入两个以上的有效编码信 号。当同时输入几个有效编码信号时,优先编码器 能按预先设定的优先级别,只对其中优先权最高的 一个进行编码。 编码器 (Encoder)的概念与分类 普通编码器 优先编码器

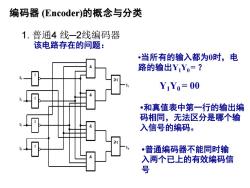

编码器(Encoder)的概念与分类 1.普通4线-2线编码器 该电路存在的问题: 当所有的输入都为0时,电 路的输出YYo=? Y1Yo=00 呵 ·和真值表中第一行的输出编 码相同,无法区分是哪个输 入信号的编码。 •普通编码器不能同时输 入两个已上的有效编码信 号

该电路存在的问题: •当所有的输入都为0时,电 路的输出Y1Y0 = ? Y1Y0 = 00 •和真值表中第一行的输出编 码相同,无法区分是哪个输 入信号的编码。 I0 I1 I2 I3 1 1 1 1 & & & ≥1 ≥1 Y0 Y1 & •普通编码器不能同时输 入两个已上的有效编码信 号 1. 普通4 线─2线编码器 编码器 (Encoder)的概念与分类

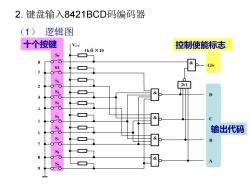

2.键盘输入8421BCD码编码器 (1) 逻辑图 十个按键 控制使能标志 1k2×10 C 输出代码

2 3 4 5 6 7 8 9 0 1 S0 S1 S2 S3 S4 S5 S6 S7 S8 S9 VCC 1kΩ×10 & & & & ≥1 & GS D C B A 十个按键 输出代码 控制使能标志 2. 键盘输入8421BCD码编码器 (1) 逻辑图

2.键盘输入8421BCD码编码器 (2)功能表 输入 输出 SS S2 S3 S S3SS SsS A B C D GS 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 1 1 0 1 1 0 1 0 1 0 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 0 0 该编码器为输入低电平有效

(2)功能表 输 入 输 出 S0 S1 S2 S3 S4 S5 S6 S7 S8 S9 A B C D GS 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 1 0 0 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 1 1 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 1 1 0 0 0 0 1 该编码器为输入低电平有效 2. 键盘输入8421BCD码编码器

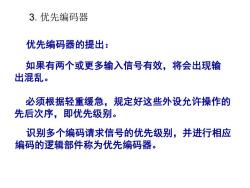

3.优先编码器 优先编码器的提出: 如果有两个或更多输入信号有效,将会出现输 出混乱。 必须根据轻重缓急,规定好这些外设允许操作的 先后次序,即优先级别。 识别多个编码请求信号的优先级别,并进行相应 编码的逻辑部件称为优先编码器

3. 优先编码器 优先编码器的提出: 如果有两个或更多输入信号有效,将会出现输 出混乱。 必须根据轻重缓急,规定好这些外设允许操作的 先后次序,即优先级别。 识别多个编码请求信号的优先级别,并进行相应 编码的逻辑部件称为优先编码器

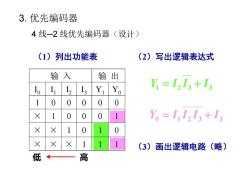

3.优先编码器 4线一2线优先编码器(设计) (1)列出功能表 (2)写出逻辑表达式 输入 输出 I Y Yo Y=I2I3+3 1 0 0 0 0 0 X 1 0 Y=I1213+I3 × × (3)画出逻辑电路(略) 低 高

4 线─2 线优先编码器(设计) (1)列出功能表 输 入 输 出 I 0 I 1 I 2 I 3 Y1 Y0 1 0 0 0 0 0 × 1 0 0 0 1 × × 1 0 1 0 × × × 1 1 1 0 1 2 3 3 Y = I I I + I 1 2 3 3 Y = I I + I 低 高 (2)写出逻辑表达式 (3)画出逻辑电路(略) 3. 优先编码器

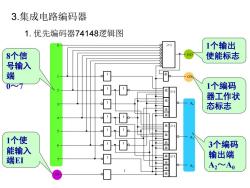

3.集成电路编码器 1.优先编码器74148逻辑图 1个输出 8个信 使能标志 号输入 0≈7 巴 1个编码 & 器工作状 & 态标志 & & & 1个使 & 能输入 & 3个编码 端EI 输出端 A2≈A0

1. 优先编码器74148逻辑图 2345671 EI 1111111 11111 ≥1 &&&&&&&&&&&&& ≥1 ≥1 ≥1 A2 A1 A0 GS EO 0 8个信 号输入 端0~7 1个使 能输入 端EI 3个编码 输出端 A2~A0 1个编码 器工作状 态标志 1个输出 使能标志 3.集成电路编码器

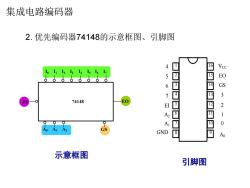

集成电路编码器 2.优先编码器74148的示意框图、引脚图 4 cc 5 6 E GS 7 74148 EI 2 A2 ● 0 GND A 示意框图 引脚图

I0 I1 I2 I3 I4 I5 I6 I7 EI 74148 EO A0 A1 A2 GS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 4 16 5 6 7 EI A2 A1 GND VCC EO GS 3 2 1 0 A0 引脚图 示意框图 2. 优先编码器74148的示意框图、引脚图 集成电路编码器

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.1 半加器与全加器 2 全加器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.1 半加器与全加器 1 半加器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.2 组合逻辑电路的设计4.2.2 特殊问题的逻辑设计.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.2 组合逻辑电路的设计 4.2 组合逻辑设计.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路 4.1 组合逻辑分析.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.7 包含无关项的逻辑函数的化简.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.4 逻辑函数的卡诺图表示法.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.3 卡诺图的结构.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.2 最小项.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.1 卡诺图化简原理.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.2 逻辑函数的代数法化简 3.2.3 化简的意义.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.2 逻辑函数的代数法化简 3.2.1 代数法化简.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.1 基本公式与规则 3.1.3 基本公式的应用(逻辑函数不同形式的转换).ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.1 基本公式与规则 3.1.2 基本规则.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.1 基本公式与规则 3.1.1 基本公式.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第一章 数制与代码——1.4常用代码(字符码).ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第一章 数制与代码——1.4常用代码(奇偶校验码).ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第一章 数制与代码——1.4常用代码(格雷码).ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第一章 数制与代码——1.4常用代码(BCD).ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第一章 数制与代码——1.4常用代码(8421).ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.2 编码器与译码器 2 译码器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.3 数据选择器及多路分配器 1 数据选择器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.3 数据选择器及多路分配器 2 数据选择器的应用.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.3.4 数值比较器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4 .1 竞争现象 竞争示意图.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4 .2 组合逻辑中的竞争冒险.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4.3 冒险现象的判别.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 卡诺图的冒险情况.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4.4 冒险现象的消除.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第五章 触发器——5.1 基本触发器 5.1.1 与非门实现的基本RS触发器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第五章 触发器——5.1 基本触发器 5.1.4 T触发器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.1 特点.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.2 分类.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.4 状态图与时序图.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.2 同步时序电路分析与设计 6.2.1 同步时序电路分析.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.2 同步时序电路分析与设计 6.2.3 同步时序电路设计与举例.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.1 计数器分类.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.1 二进制同步加计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.2 二进制同步减计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 二进制异步加计数器.ppt