江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.4 状态图与时序图

时序电路的逻辑功能描述方法 时序电路的逻辑功能可以用状态方程、状态图、状态表、 时序图四种方法来表示,这几种表示方法是等价的,并且可以 相互转换。 1.状态方程-表明时序电路中触发器状态转换条件的代数表示 方式 例如有两个触发器F1,F2,其中F2的状态方程为 Q2+1=XQ1+XQ2Ql 则表明当X=1、Q1=0或X=0、Q2Q1=11时,F2的次态 Q2n+1=1 因此状态方程是说明使次态为1时外输入和内部状态的条件。 它在形式上与触发器的特征方程相似,所不同的是根据外部输 入变量和电路中各触发器的现态值来确定次态条件

时序电路的逻辑功能可以用状态方程、状态图、状态表、 时序图四种方法来表示,这几种表示方法是等价的,并且可以 相互转换。 1.状态方程-表明时序电路中触发器状态转换条件的代数表示 方式 例如有两个触发器F1、F2,其中F2的状态方程为 Q2 n+1=XQ1+XQ2Q1 则表明当X=1、Q1=0或X=0、Q2Q1=11时,F2的次态 Q2 n+1=1 因此状态方程是说明使次态为1时外输入和内部状态的条件。 它在形式上与触发器的特征方程相似,所不同的是根据外部输 入变量和电路中各触发器的现态值来确定次态条件 时序电路的逻辑功能描述方法

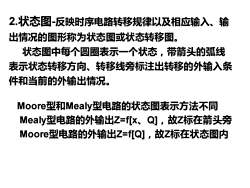

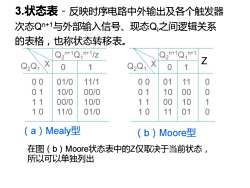

2状态图-反映时序电路转移规律以及相应输入、输 出情况的图形称为状态图或状态转移图。 状态图中每个圆圈表示一个状态,带箭头的弧线 表示状态转移方向、转移线旁标注出转移的外输入条 件和当前的外输出情况。 Moore型和Meay型电路的状态图表示方法不同 Mealy型电路的外输出Z=fx、Q],故Z标在箭头旁 Moore型电路的外输出Z=f[Q],故Z标在状态图内

2.状态图-反映时序电路转移规律以及相应输入、输 出情况的图形称为状态图或状态转移图。 状态图中每个圆圈表示一个状态,带箭头的弧线 表示状态转移方向、转移线旁标注出转移的外输入条 件和当前的外输出情况。 Moore型和Mealy型电路的状态图表示方法不同 Mealy型电路的外输出Z=f[x、Q],故Z标在箭头旁 Moore型电路的外输出Z=f[Q],故Z标在状态图内

Mealy型状态图 0/0 1/0 0/0 00 X/Z 0/0 0.1/0 1/1 1/0 10 11 (图a) 箭头旁标注的是外输入X和外输出Z

00 01 10 11 0/0 1/0 0/0 1/1 0.1/0 1/0 0/0 (图a) 箭头旁标注的是外输入X和外输出Z Mealy型状态图 X/Z

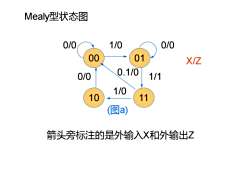

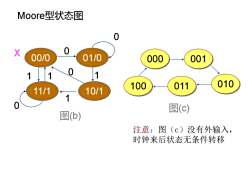

Moore型状态图 X 0 00/0 01/0 000 001 0 010 11/1 10/1 100 011 图(c) 图b) 注意:图(c)没有外输入, 时钟来后状态无条件转移

Moore型状态图 00/0 01/0 11/1 10/1 X 0 1 1 0 1 1 0 0 000 001 100 011 010 图(b) 图(c) 注意:图(c)没有外输入, 时钟来后状态无条件转移

3.状态表-反映时序电路中外输出及各个触发器 次态Q+1与外部输入信号、现态Q之间逻辑关系 的表格,也称状态转移表。 Q2n+1Qn+1/z 2+1Q1+1 Q2Qj 0 1 Q2Qj 0 00 01/0 11/1 00 01 11 0 01 10/0 00/0 01 10 00 0 11 00/0 10/0 11 00 10 1 10 11/0 01/0 10 11 01 0 (a)Mealy?型 (b)Moore型 在图(b)Moore状态表中的Z仅取决于当前状态, 所以可以单独列出

3.状态表-反映时序电路中外输出及各个触发器 次态Qn+1与外部输入信号、现态Qi之间逻辑关系 的表格,也称状态转移表。 Q2 n+1Q1 n+1/z Q X 2Q1 0 0 0 1 1 1 1 0 0 1 01/0 10/0 00/0 11/0 11/1 00/0 10/0 01/0 (a)Mealy型 Q2 n+1Q1 n+1 Q X 2Q1 0 0 0 1 1 1 1 0 0 1 01 10 00 11 11 00 10 01 Z 0 0 1 0 (b)Moore型 在图(b)Moore状态表中的Z仅取决于当前状态, 所以可以单独列出

Q2QQo Q2+1Q+1Q0+1 000 0 0 0 cp Q2QQo 001 0 0 1 1 000 010 0 1 0 2 001 011 0 1 1 3 010 100 7 0 0 4 011 101 1 0 1 5 100 110 1 1 0 111 1 (d)Moore?型态序表 (c)Moore?型 图(c)是没有外输入X和外输出Z的状态表。 图(d)仅表示主循环的状态变化

Q2Q1Q0 Q2 n+1Q1 n+1Q0 n+1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 (c)Moore型 cp Q2Q1Q0 1 2 3 4 5 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 (d)Moore型态序表 图(c)是没有外输入X和外输出Z的状态表。 图(d)仅表示主循环的状态变化

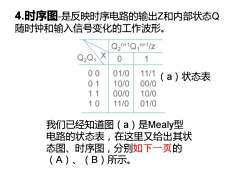

4.时序图是反映时序电路的输出Z和内部状态Q 随时钟和输入信号变化的工作波形。 Q2n+1Q+1/Z Q2Q 0 1 00 01/0 11/1 (a)状态表 01 10/0 00/0 11 00/0 10/0 10 11/0 01/0 我们已经知道图(a)是Mealy型 电路的状态表,在这里又给出其状 态图、时序图,分别如下一页的 (A)、(B)所示

4.时序图-是反映时序电路的输出Z和内部状态Q 随时钟和输入信号变化的工作波形。 Q2 n+1Q1 n+1/z Q X 2Q1 0 0 0 1 1 1 1 0 0 1 01/0 10/0 00/0 11/0 11/1 00/0 10/0 01/0 (a)状态表 我们已经知道图(a)是Mealy型 电路的状态表,在这里又给出其状 态图、时序图,分别如下一页的 (A)、(B)所示

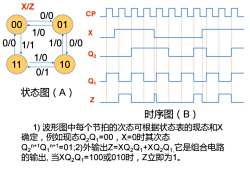

X/Z 0/0 CP 01 1/0 X 0/0 1/1 1/0 0/0 1/0 Q2 10 0/1 状态图(A) 时序图(B) )波形图中每个节拍的次态可根据状态表的现态和X 确定,例如现态Q,Q=00,X=0时其次态 Q2+1Q,+1=01;2)外输出Z=XQ2Q1+XQ2Q1,它是组合电路 的输出,当XQ2Q=100或010时,Z立即为1

00 01 11 10 0/0 0/0 1/0 1/0 1/0 0/0 0/1 1/1 状态图(A) CP X Q2 Q1 Z 时序图(B) X/Z 1) 波形图中每个节拍的次态可根据状态表的现态和X 确定,例如现态Q2Q1=00,X=0时其次态 Q2 n+1Q1 n+1=01;2)外输出Z=XQ2Q1+XQ2Q1,它是组合电路 的输出, 当XQ2Q1=100或010时,Z立即为1

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.2 分类.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.1 特点.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第五章 触发器——5.1 基本触发器 5.1.4 T触发器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第五章 触发器——5.1 基本触发器 5.1.1 与非门实现的基本RS触发器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4.4 冒险现象的消除.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 卡诺图的冒险情况.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4.3 冒险现象的判别.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4 .2 组合逻辑中的竞争冒险.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4 .1 竞争现象 竞争示意图.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.3.4 数值比较器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.3 数据选择器及多路分配器 2 数据选择器的应用.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.3 数据选择器及多路分配器 1 数据选择器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.2 编码器与译码器 2 译码器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.2 编码器与译码器 1 编码器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.1 半加器与全加器 2 全加器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.1 半加器与全加器 1 半加器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.2 组合逻辑电路的设计4.2.2 特殊问题的逻辑设计.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.2 组合逻辑电路的设计 4.2 组合逻辑设计.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路 4.1 组合逻辑分析.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.7 包含无关项的逻辑函数的化简.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.2 同步时序电路分析与设计 6.2.1 同步时序电路分析.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.2 同步时序电路分析与设计 6.2.3 同步时序电路设计与举例.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.1 计数器分类.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.1 二进制同步加计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.2 二进制同步减计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 二进制异步加计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 74HCT161.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 74LS290.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 集成计数器74161.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 74LS193.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.1 寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.1.1 锁存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.1.2 基本寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.2 移位寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.3.2 锁存器、寄存器和移位寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第八章 数/模与模/数转换——8.1 DAC 8.1.2 倒T型电阻网络DAC.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第八章 数/模与模/数转换——8.1 DAC 8.1.4 集成DA转换器及应用.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第八章 数/模与模/数转换——8.2 ADC 8.2.1 AD转换基本原理.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第八章 数/模与模/数转换——8.2 ADC 8.2.2 AD转换器工作原理.ppt

- 私立华联学院:《汽车电工电子技术》课程教学资源(教学大纲).pdf