江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第五章 触发器——5.1 基本触发器 5.1.1 与非门实现的基本RS触发器

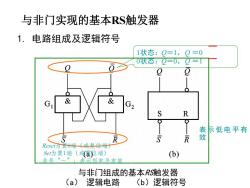

与非门实现的基本RS触发器 1.电路组成及逻辑符号 1状态:Q=1、0=0 0状态:Q=0、Q=1 Q & R 表示低电平有 R Reset为置0端(或复住端) Set为置1端(或(拉端) (b) 非号“一”·表示低电平有效 与非门组成的基本S触发器 (a 0 逻辑电路 (b)逻辑符号

与非门组成的基本RS触发器 (a) 逻辑电路 (b)逻辑符号 1状态:Q=1、Q =0 0状态:Q=0、Q =1 Reset为置0端(或复位端) Set为置1端(或置位端) 非号“-”:表示低电平有效 表 示 低电 平有 效 1. 电路组成及逻辑符号 与非门实现的基本RS触发器

2.功能表 与非门组成的基本S触发器的功能表 s R OnH Ort 状态(功能) 1 Q Q” 保持 1 0 0 1 置0 0 1 0 置1 0 1 1 不定

与非门组成的基本RS触发器的功能表 2. 功能表

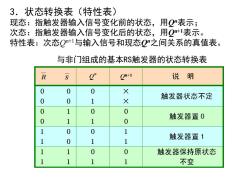

3.状态转换表(特性表) 现态:指触发器输入信号变化前的状态,用Q表示; 次态:指触发器输入信号变化后的状态,用Q+1表示。 特性表:次态Q1与输入信号和现态Q之间关系的真值表。 与非门组成的基本RS触发器的状态转换表 R S On+1 说明 0 0 0 × 触发器状态不定 0 0 1 X 0 1 0 0 触发器置0 0 1 1 0 0 0 1 触发器置1 0 1 1 1 0 0 触发器保持原状态 1 1 1 不变

3.状态转换表(特性表) 现态:指触发器输入信号变化前的状态,用Qn表示; 次态:指触发器输入信号变化后的状态,用Qn+1表示。 特性表:次态Qn+1与输入信号和现态Qn之间关系的真值表。 与非门组成的基本RS触发器的状态转换表

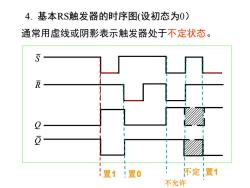

4.基本RS触发器的时序图(设初态为0) 通常用虚线或阴影表示触发器处于不定状态。 R 豆 置1!置0 不定置1 不允许

通常用虚线或阴影表示触发器处于不定状态。 置1 置0 不允许 不定 置1 4. 基本RS触发器的时序图(设初态为0)

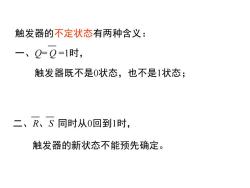

触发器的不定状态有两种含义: 一、Q=Q=1时, 触发器既不是0状态,也不是1状态; 二、R、S同时从0回到1时, 触发器的新状态不能预先确定

触发器的不定状态有两种含义: 一、Q= Q =1时, 触发器既不是0状态,也不是1状态; 二、R、S 同时从0回到1时, 触发器的新状态不能预先确定

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4.4 冒险现象的消除.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 卡诺图的冒险情况.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4.3 冒险现象的判别.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4 .2 组合逻辑中的竞争冒险.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.4 .1 竞争现象 竞争示意图.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.4 组合逻辑电路中的竞争与冒险 4.3.4 数值比较器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.3 数据选择器及多路分配器 2 数据选择器的应用.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.3 数据选择器及多路分配器 1 数据选择器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.2 编码器与译码器 2 译码器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.2 编码器与译码器 1 编码器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.1 半加器与全加器 2 全加器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.3 常用中规模组合逻辑部件的原理和应用 4.3.1 半加器与全加器 1 半加器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.2 组合逻辑电路的设计4.2.2 特殊问题的逻辑设计.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路——4.2 组合逻辑电路的设计 4.2 组合逻辑设计.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第四章 组合逻辑电路 4.1 组合逻辑分析.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.7 包含无关项的逻辑函数的化简.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.4 逻辑函数的卡诺图表示法.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.3 卡诺图的结构.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.2 最小项.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第三章 布尔代数与逻辑函数化简——3.3 卡诺图 3.3.1 卡诺图化简原理.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第五章 触发器——5.1 基本触发器 5.1.4 T触发器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.1 特点.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.2 分类.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.1 时序逻辑电路概述 6.1.4 状态图与时序图.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.2 同步时序电路分析与设计 6.2.1 同步时序电路分析.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.2 同步时序电路分析与设计 6.2.3 同步时序电路设计与举例.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.1 计数器分类.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.1 二进制同步加计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.2 二进制同步减计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 二进制异步加计数器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 74HCT161.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 74LS290.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 集成计数器74161.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.3 计数器 6.3.3 集成计数器功能分析及其应用 74LS193.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.1 寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.1.1 锁存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.1.2 基本寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.2 移位寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第六章 时序逻辑电路——6.4 寄存器与移位寄存器 6.4.3.2 锁存器、寄存器和移位寄存器.ppt

- 江西农业大学:《数字逻辑》课程教学资源(PPT讲稿)第八章 数/模与模/数转换——8.1 DAC 8.1.2 倒T型电阻网络DAC.ppt