电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第2章 电路测试基础

DFT技术与各章的关系--知识脉络图 超大规模 集成电路测试 4出 理论 实战 2020/9/4 集成电路可测性设计 2

DFT技术与各章的关系---知识脉络图 2020/9/4 集成电路可测性设计 2 理论 实战

第二章电路测试基础 重点:故障建模的基础知识 子料技女学 /966 University of Electronic Science and Technology of China

第二章 电路测试基础 重点:故障建模的基础知识

本章要点 。在电路测试设计和分析之前,掌握5方 面的基础知识 测试和设计环节的关系 >第一章已经有所涉及 >补充一点内容 物理缺陷的建模 基于故障的测试生成 基本概念 是后面研究的基础 -故障简化 2020/9/4 集成电路可测性设计 4

2020/9/4 集成电路可测性设计 4 本章要点 在电路测试设计和分析之前,掌握5方 面的基础知识 测试和设计环节的关系 第一章已经有所涉及 补充一点内容 物理缺陷的建模 基于故障的测试生成 故障简化 基本概念 是后面研究的基础

2.1设计、验证和测试 设计描述 行为域 系统级 结构域 寄存器级 映射 (Mapping) 门级 物理域 电路级 目前验证已经占据整个设计工作的 40%至70% 2020/9/4 集成电路可测性设计 5

2020/9/4 集成电路可测性设计 5 2.1 设计、验证和测试 设计描述 系统级 寄存器级 门级 电路级 行为域 物理域 结构域 映射 (Mapping) 目前验证已经占据整个设计工作的 40%至70%

验证与生产测试的区别 设计验证 产品 (Verification) (Product) (EDA) 设计工具 (Develop Tools) 仿真环境 (BIST) 内建自测试 (ATE) 自动测试设备 功能模拟 时间模拟 仿真 测试 (Simulation) (Emulation (Testing) 2020/9/4 集成电路可测性设计 6

2020/9/4 集成电路可测性设计 6 验证与生产测试的区别 设计验证 (Verification) 设计工具 (EDA) 仿真环境 (Develop Tools) 功能模拟 时间模拟 产品 (Product) 内建自测试 (BIST) 自动测试设备 (ATE) 仿真 (Emulation) (Simulation) 测试 (Testing)

Synopsys?验证平台 Debug,Planning Coverage Virtual Static Simulation Emulation Prototyping Prototyping Formal VIP Models Databases 2020/9/4 集成电路可测性设计 7

Synopsys验证平台 2020/9/4 集成电路可测性设计 7

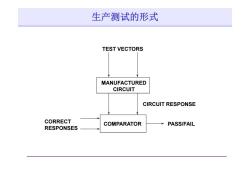

生产测试的形式 TEST VECTORS MANUFACTURED CIRCUIT CIRCUIT RESPONSE CORRECT COMPARATOR PASS/FAIL RESPONSES

TEST VECTORS MANUFACTURED CIRCUIT COMPARATOR CIRCUIT RESPONSE PASS/FAIL CORRECT RESPONSES 生产测试的形式

ATE 功能 1ΠΠΠΠΠΠ DC/AC参数 E CPU I/0 AS-DSP 控制器 内核 ATE 通道 测试头 解码器 测试访问机制 > UDL 存储器 控制器TAM 存储器 专用IP 内嵌 SRAM 2020/9/4 集成电路可测性设计 9

2020/9/4 集成电路可测性设计 9 ATE SOC 解 码 器 测试访问机制 控制器TAM CPU I/O 控制器 AS-DSP 内核 存储器 内嵌 SRAM 专用IP UDL 测 试 头 ATE 通道 存储器 功能 DC/AC 参数

测试是过滤过程 好芯片 Prob(通过测试)=高 大多数 好 Prob(好)=y Prob(未通 测试)=低 芯片 制造的 芯片 Prob(通过 测试)=低 有缺陷的芯片 大多数 坏 Prob(坏)=1-y Prob(未通过测试)=高 芯片 2020/914 集成电路可测性设计 10

2020/9/4 集成电路可测性设计 10 测试是过滤过程 制造的 芯片 好芯片 有缺陷的芯片 Prob(好) = y Prob(坏) = 1- y Prob(通过测试) = 高 Prob(未通过测试) =高 大多数 好 芯片 大多数 坏 芯片

测试和质量 Shipped Parts ASIC Fabrication Yield: Testing Quality: Fraction of Defective parts good parts per million(DPM) Rejects Quality of shipped part is a function of yield Y and the test (fault)coverage T

ASIC Fabrication Testing Yield: Fraction of good parts Rejects Shipped Parts Quality: Defective parts per million (DPM) * Quality of shipped part is a function of yield Y and the test (fault) coverage T. 测试和质量

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——测试的基本知识.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——研究意义(王忆文).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 15 数字强度缩减 Numerical Strength Reduction.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 14 冗余运算 Redundant Arithmetic.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 13 位级运算 Bit-Level Arithmetic Architectures.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 11 缩放噪声 Scaling and Roundoff Noise.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 09 算法强度缩减 Algorithmic strength reduction in filters and transforms.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 08 快速卷积 Fast Convolution.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 10 递归滤波器 Pipelined and Parallel Recursive and Adaptive Filters.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 07 脉动阵列 Systolic Architecture.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 06 折叠 Folding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 05 展开 Unfolding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 04 重定时 Retiming.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 03 流水与并行 Pipelining and Parallel Processing.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 02 迭代界 Iteration Bound.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 01 导论 Introduction to Digital Signal Processing Systems.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 00 简介 Introduction to VLSI(凌翔).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(教学大纲,凌翔).pdf

- 电子科技大学:《电子无源元件工艺实验》课程实验课件讲稿 Electronic Passive Components Process Experiment Course(主讲:戴丽萍).pdf

- 电子科技大学:《半导体封装测试与可靠性 Packaging,Testing and Reliability of Semiconductor》课程教学资源(课件讲稿,思政版).pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第3章 验证、模拟和仿真.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第4章 自动测试生成.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第10章 电流测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第11章 存储器测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(1/2).pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第5章 专用可测性设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第6章 扫描设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第7章 边界扫描.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第8、9章 内建自测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(2/2)IEEE P1500 嵌入式核可测性标准.pdf

- 《现代编码理论与技术》课程教学资源(学习资料)Turbo码启示录——从默默无闻到广泛应用.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第三章 线性分码组.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第五章 循环码(陆以勤).doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第四章 多项式环与有限域.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第六章 循环码的译码.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第一章 纠错码的基本概念.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第二章 代数初步(陆以勤).ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第三章 线性分码组.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第四章 多项式环与有限域.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第五章 循环码.ppt