电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第11章 存储器测试

●●● ●● ●●●● ●●● 第十一章存储器测试 子料战女学 /966 University of Electronic Science and Technology of China

2021/8/18 集成电路可测性设计 2 第十一章 存储器测试

●●● ●● ●●●● 内容提要 ●●0● ●●o● ① 概述 ② 存储器模型 ③ 失效机制和故障模型 ④ 存储器的测试算法 2021/8/18 集成电路可测性设计 3

2021/8/18 集成电路可测性设计 3 内容提要 ① 概述 ② 存储器模型 ③ 失效机制和故障模型 ④ 存储器的测试算法

●●●● 0●●●● ●●●● ●●●● ●●0● ●●0● ●● 11.1概述 2021/8/18 集成电路可测性设计 4

2021/8/18 集成电路可测性设计 4 11.1 概述

● ●● 11.1概述 ●●●● ●●● o Memories (esp.RAM)are at the forefront of commercial electronic designs DRAMs are the technology driver for the semiconductor industry Memories are the most numerous IPs used in SOC designs (hundreds and >90%of an SoC in 2010) 2021/8/18 集成电路可测性设计 5

2021/8/18 集成电路可测性设计 5 11.1 概述 Memories (esp. RAM) are at the forefront of commercial electronic designs DRAMs are the technology driver for the semiconductor industry Memories are the most numerous IPs used in SOC designs (hundreds ! and >90% of an SoC in 2010)

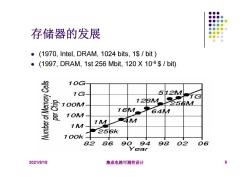

●● ●● 存储器的发展 ●● ●● ●● ●(1970,Intel,.DRAM,1024bits,1$/bit) ●(1997,DRAM,1st256Mbit,120X10-6$/bit) 邑 10G 1G 512M G 123nH 1O0M 5 16M ⑧ 64i 1OM 1M 4几A i几i 255k 1ook 82 36 994 02 06 Year 2021/8/18 集成电路可测性设计 6

2021/8/18 集成电路可测性设计 6 (1970, Intel, DRAM, 1024 bits, 1$ / bit ) (1997, DRAM, 1st 256 Mbit, 120 X 10-6 $ / bit) 存储器的发展

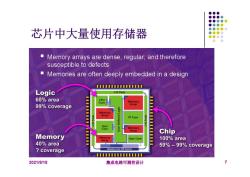

● ● 芯片中大量使用存储器 ●0 ●●●● ●●●● ■ Memory arrays are dense,regular,and therefore susceptible to defects Memories are often deeply embedded in a design Logic I/O Pads 60%area CPU Core Memory 99%coverage Array : Memory Array IP Core sped User Core Memory Array Chip Memory Memory User Core Array 100%area 40%area 59%-99%coverage coverage 2021/8/18 集成电路可测性设计 7

2021/8/18 集成电路可测性设计 7 芯片中大量使用存储器

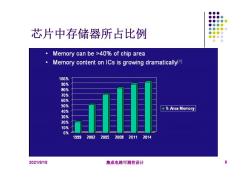

●0 ● ●●0 芯片中存储器所占比例 ●●●● ●●●● Memory can be >40%of chip area Memory content on ICs is growing dramatically[1] 100% 第1】1破040第14第第1假 ■%ea Memory 199920022005200820112014 2021/8/18 集成电路可测性设计 8

2021/8/18 集成电路可测性设计 8 芯片中存储器所占比例

●0 ● ●●0 存储器的测试越来越难 ●●● ●●●● Memories are: Often deeply embedded 3 in a design Dense,regular structures rlue Logic Susceptible to defects ontro Lend themselves to algorithm- based testing CORE 2021/8/18 集成电路可测性设计 9

2021/8/18 集成电路可测性设计 9 存储器的测试越来越难

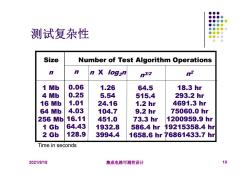

● ●0 测试复杂性 ●●●● ●●● Size Number of Test Algorithm Operations X log2n m32 2 1Mb 0.06 1.26 64.5 18.3hr 4 Mb 0.25 5.54 515.4 293.2hr 16 Mb 1.01 24.16 1.2hr 4691.3hr 64 Mb 4.03 104.7 9.2hr 75060.0hr 256Mb 16.11 451.0 73.3hr 1200959.9hr 1Gb 64.43 1932.8 586.4hr 19215358.4hr 2 Gb 128.9 3994.4 1658.6hr76861433.7 hr Time in seconds 2021/8/18 集成电路可测性设计 10

2021/8/18 集成电路可测性设计 10 n 1 Mb 4 Mb 16 Mb 64 Mb 256 Mb 1 Gb 2 Gb n 0.06 0.25 1.01 4.03 16.11 64.43 128.9 n X log2n 1.26 5.54 24.16 104.7 451.0 1932.8 3994.4 n3/2 64.5 515.4 1.2 hr 9.2 hr 73.3 hr 586.4 hr 1658.6 hr n2 18.3 hr 293.2 hr 4691.3 hr 75060.0 hr 1200959.9 hr 19215358.4 hr 76861433.7 hr Size Number of Test Algorithm Operations 测试复杂性 Time in seconds

●● ●●● ●●● ●●●0 存储器种类 ●●●● ■ SRAM DRAM High-speed read and write ·Read and write ·Volatile ·High density ■Register file 。 Volatile ·ide and shallow Flash ·Less dense ·Read and write ·Volatile Non-volatile ROM ·Read only Non-volatile 2021/8/18 集成电路可测性设计 11

2021/8/18 集成电路可测性设计 11 存储器种类

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第10章 电流测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第4章 自动测试生成.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第3章 验证、模拟和仿真.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第2章 电路测试基础.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——测试的基本知识.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——研究意义(王忆文).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 15 数字强度缩减 Numerical Strength Reduction.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 14 冗余运算 Redundant Arithmetic.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 13 位级运算 Bit-Level Arithmetic Architectures.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 11 缩放噪声 Scaling and Roundoff Noise.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 09 算法强度缩减 Algorithmic strength reduction in filters and transforms.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 08 快速卷积 Fast Convolution.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 10 递归滤波器 Pipelined and Parallel Recursive and Adaptive Filters.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 07 脉动阵列 Systolic Architecture.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 06 折叠 Folding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 05 展开 Unfolding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 04 重定时 Retiming.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 03 流水与并行 Pipelining and Parallel Processing.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 02 迭代界 Iteration Bound.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 01 导论 Introduction to Digital Signal Processing Systems.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(1/2).pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第5章 专用可测性设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第6章 扫描设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第7章 边界扫描.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第8、9章 内建自测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(2/2)IEEE P1500 嵌入式核可测性标准.pdf

- 《现代编码理论与技术》课程教学资源(学习资料)Turbo码启示录——从默默无闻到广泛应用.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第三章 线性分码组.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第五章 循环码(陆以勤).doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第四章 多项式环与有限域.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第六章 循环码的译码.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第一章 纠错码的基本概念.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第二章 代数初步(陆以勤).ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第三章 线性分码组.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第四章 多项式环与有限域.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第五章 循环码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第六章 循环码的译码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第七章 BCH码与Goppa码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第十章 卷积码基础.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第十三章 Turbo码.ppt