电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第4章 自动测试生成

第四章自动测试生成 包子种皮女学 /966 University of Electronic Science and Technology of China

第四章 自动测试生成

本章要点 掌握组合电路的测试生成 -代数法 >异或法 >布尔差分法 、 算法 >D算法 >PODEM算法 >FAN算法 >其他 时序电路的测试生成 -可测性方法(不具体要求) 2020/9/5 集成电路可测性设计 3

2020/9/5 集成电路可测性设计 3 本章要点 掌握组合电路的测试生成 代数法 异或法 布尔差分法 算法D算法 PODEM算法 FAN算法 其他 时序电路的测试生成 可测性方法(不具体要求)

常用的测试生成 Fault Combinational Sequential Models Circuits Circuits (seq.ckt.w/scan) No fault model PET Checking experiment Single Stuck-at D Extended D Fault Model PODEM 9-valued FAN Delay Fault Model Path delay Launch on capture Transition delay Launch on shift 2020/9/5 集成电路可测性设计 4

常用的测试生成 2020/9/5 集成电路可测性设计 4

4.1简介 子科战女学 1/966 University of Electronic Science and Technology of China

4.1 简介

简介 测试生成:被测电路的给定故障确定测试图形的过 程 必基本要求:(故障)源处再现, (效应)输出可观。 分为确定性测试生成和非确定性测试生成 研究最早始于1959年 2020/9/5 集成电路可测性设计 6

2020/9/5 集成电路可测性设计 6 简介 测试生成:被测电路的给定故障确定测试图形的过 程 基本要求:(故障)源处再现,(效应)输出可观。 分为确定性测试生成和非确定性测试生成 研究最早始于1959年

确定性测试生成方法 代数法 算法 ●异或运算 ●路径敏化法 D算法 ●布尔差分 ● PODEM算法 ●FAN算法 基本过程 故障激活(Excitation) 故障传播(Sensitization) ● 确认(Justification) 蕴涵(Implication) 一致性检查(Consistency) 2020/9/5 集成电路可测性设计 7

2020/9/5 集成电路可测性设计 7 确定性测试生成方法 代数法 异或运算 布尔差分 算法 路径敏化法 D算法 PODEM算法 FAN算法 基本过程 故障激活(Excitation) 故障传播(Sensitization) 确认(Justification) 蕴涵(Implication) 一致性检查(Consistency)

4.2代数法 包子件皮女学 1/966 University of Electronic Science and Technology of China

4.2 代数法

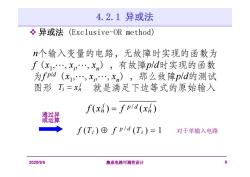

4.2.1异或法 冬异或法(Exclusive-OR method) n个输入变量的电路,无故障时实现的函数为 ∫(x1,…,x,…,xn),有故障p/d时实现的函数 为fpd(x1…,x2…,xn),那么故障pld的测试 图形T=x就是满足下边等式的原始输入 f(xh)=fpld(xH) 通过异 或运算 f(Ti)⊕fp1d(Ti)=1 对于单输入电路 2020/9/5 集成电路可测性设计 9

2020/9/5 集成电路可测性设计 9 4.2.1 异或法 异或法 (Exclusive-OR method) n个输入变量的电路,无故障时实现的函数为 f(x1,, xi ,, xn),有故障p/d时实现的函数 为f p/d(x1,, xi ,, xn),那么故障p/d的测试 图形 就是满足下边等式的原始输入 j T x i n / ( ) ( ) j j p d f x f x n n / ( ) ( ) 1 p d f T f T i i 通过异 或运算 对于单输入电路

异或法测试生成举例 2 X3 3 12g XI 5 6 6 8(x6)=(x1+x2+x3+x4)(x5+x6) g6/0(x6)=x1+x2+x3+x4 6/0 610 G =g(x)g (x6)=XXsX6+x2X5X6+x3XsX6+x4Xsx6 2020/9/5 集成电路可测性设计 10

2020/9/5 集成电路可测性设计 10 异或法测试生成举例 g x x x x x x x ( ) ( )( ) 6 1 2 3 4 6 5 43216 0/6 xxxx)x(g )()( 6 0/6 6 0/6 xgxgG 654653652651 xxxxxxxxxxxx

4.2.2布尔差分法 对开关函数(布尔函数)F(X)=F(x1,x2,,xn)定义 F(x)=F(x1,x2,…,X,…,Xn) F()=F(x1,x2,…,x,…,xn) 布尔函数对变量x的差分定义为 dF()=F(x)⊕F(,) (2.5) dx 式(2.5)的意义是:当x变化时,其对应的F)的异或结果为1时, 相应的电路输出能反映的变化,即是可测的,反之是不可测的。 2020/9/5 集成电路可测性设计 11

2020/9/5 集成电路可测性设计 11 对开关函数(布尔函数) , 定义 布尔函数对变量 的差分定义为 (2.5) 式(2.5)的意义是:当xi 变化时,其对应的F( )的异或结果为1时, 相应的电路输出能反映的变化,即是可测的,反之是不可测的。 ),,,()( 21 n xxxFXF ),,,,,()( 21 nii xxxxFxF ),,,,,()( 21 nii xxxxFxF i x )()( )( 1 ii xFxF dx xdF i x i x 4.2.2 布尔差分法

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第3章 验证、模拟和仿真.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第2章 电路测试基础.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——测试的基本知识.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——研究意义(王忆文).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 15 数字强度缩减 Numerical Strength Reduction.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 14 冗余运算 Redundant Arithmetic.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 13 位级运算 Bit-Level Arithmetic Architectures.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 11 缩放噪声 Scaling and Roundoff Noise.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 09 算法强度缩减 Algorithmic strength reduction in filters and transforms.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 08 快速卷积 Fast Convolution.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 10 递归滤波器 Pipelined and Parallel Recursive and Adaptive Filters.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 07 脉动阵列 Systolic Architecture.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 06 折叠 Folding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 05 展开 Unfolding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 04 重定时 Retiming.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 03 流水与并行 Pipelining and Parallel Processing.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 02 迭代界 Iteration Bound.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 01 导论 Introduction to Digital Signal Processing Systems.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 00 简介 Introduction to VLSI(凌翔).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(教学大纲,凌翔).pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第10章 电流测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第11章 存储器测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(1/2).pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第5章 专用可测性设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第6章 扫描设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第7章 边界扫描.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第8、9章 内建自测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(2/2)IEEE P1500 嵌入式核可测性标准.pdf

- 《现代编码理论与技术》课程教学资源(学习资料)Turbo码启示录——从默默无闻到广泛应用.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第三章 线性分码组.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第五章 循环码(陆以勤).doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第四章 多项式环与有限域.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第六章 循环码的译码.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第一章 纠错码的基本概念.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第二章 代数初步(陆以勤).ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第三章 线性分码组.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第四章 多项式环与有限域.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第五章 循环码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第六章 循环码的译码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第七章 BCH码与Goppa码.ppt