电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第8、9章 内建自测试

●● ●●●● ●● 第九章内建自测试(BST) 利用第八章“伪随机测试”的部分知识 2021/8/18 集成电路可测性设计 2

2021/8/18 集成电路可测性设计 2 第九章 内建自测试(BIST) 利用第八章“伪随机测试”的部分知识

●●● ●● ●●●● 本章要点 ●●●● ●●●● 。理解BIST的原理 。掌握LFSR的原理 ●掌握BIST的结构 2021/8/18 集成电路可测性设计 3

2021/8/18 集成电路可测性设计 3 本章要点 理解BIST的原理 掌握LFSR的原理 掌握BIST的结构

●●●● ●● ●●●● ●●●● ●●0● ●●o● ● 1、BST概述 2021/8/18 集成电路可测性设计 4

2021/8/18 集成电路可测性设计 4 1、BIST概述

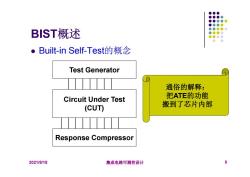

●●● ●● ● ●●0 BIST概述 ●●●● ●Built--in Self-.Test的概念 Test Generator 通俗的解释: Circuit Under Test 把ATE的功能 (CUT) 搬到了芯片内部 Response Compressor 2021/8/18 集成电路可测性设计 5

2021/8/18 集成电路可测性设计 5 BIST概述 Built-in Self-Test的概念 Test Generator Circuit Under Test (CUT) Response Compressor 通俗的解释: 把ATE的功能 搬到了芯片内部

●0 BIST的目标 ●● ●●@ Reduce input/output pin signal traffic. Permit easy circuit initialization and observation. Eliminate as much test pattern generation as possible. Achieve fair fault coverages on general class of failure mode. ●Reduce test time. Execute at-speed testing. Test circuit during burn-in. BIST Goal 2021/8/18 集成电路可测性设计 6

2021/8/18 集成电路可测性设计 6 BIST 的目标 Reduce input/output pin signal traffic. Permit easy circuit initialization and observation. Eliminate as much test pattern generation as possible. Achieve fair fault coverages on general class of failure mode. Reduce test time. Execute at-speed testing. Test circuit during burn-in. BIST Goal

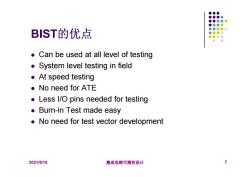

●● ●0 ● ●● BIST的优点 ●●●● ● Can be used at all level of testing System level testing in field ●At speed testing ●No need for ATE Less 1/O pins needed for testing Burn-in Test made easy No need for test vector development 2021/8/18 集成电路可测性设计 7

2021/8/18 集成电路可测性设计 7 BIST的优点 Can be used at all level of testing System level testing in field At speed testing No need for ATE Less I/O pins needed for testing Burn-in Test made easy No need for test vector development

●● ● ●● BIST的缺点 ●●●● ●●●● .Area overhead -more susceptibility to manufacturing defects Performance penalties Designing and verifying proper operation of BIST at design level. Additional risk in project 2021/8/18 集成电路可测性设计 8

2021/8/18 集成电路可测性设计 8 BIST的缺点 Area overhead -more susceptibility to manufacturing defects Performance penalties Designing and verifying proper operation of BIST at design level. Additional risk in project

●● ●0 ● ●●0 BIST分类 ●●●● ●●●● 。通常分为 。LBIST ·Logic BIST-研究很深入,但是应用很少 ●MBIST 。Memory BIST--极大的应用 ·Syntest公司 本章重点 ·SRAM BIST ●Mentor公司 ·MBIST ● Synopsys公司 ▣?? 2021/8/18 集成电路可测性设计 9

2021/8/18 集成电路可测性设计 9 BIST分类 通常分为 LBIST Logic BIST---研究很深入,但是应用很少 MBIST Memory BIST---极大的应用 Syntest公司 SRAM BIST Mentor公司 MBIST Synopsys公司 ?? 本章重点

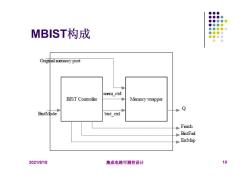

●● ●●● ●●●● ● ●●●●0 MBIST构成 ●●● ● ● Origihal memory port mem ctl BIST Controller Memory wrapper BistMbde bist ctrl Finish 渔 BistFail EnMap 2021/8/18 集成电路可测性设计 10

2021/8/18 集成电路可测性设计 10 MBIST构成

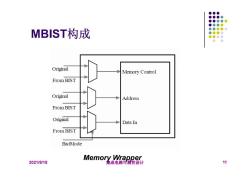

●● ●●● ●●●● ●● ●●●●0 MBIST构成 ●●●● ●●● ● Original Memory Control From BIST Original Address From BIST Original Data In From BIST BistMode Memory Wrapper 2021/8/18 集成电路可测性设计 11

2021/8/18 集成电路可测性设计 11 MBIST构成 Memory Wrapper

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第7章 边界扫描.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第6章 扫描设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第5章 专用可测性设计.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(1/2).pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第11章 存储器测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第10章 电流测试.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第4章 自动测试生成.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第3章 验证、模拟和仿真.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第2章 电路测试基础.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——测试的基本知识.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第1章 概述——研究意义(王忆文).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 15 数字强度缩减 Numerical Strength Reduction.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 14 冗余运算 Redundant Arithmetic.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 13 位级运算 Bit-Level Arithmetic Architectures.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 11 缩放噪声 Scaling and Roundoff Noise.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 09 算法强度缩减 Algorithmic strength reduction in filters and transforms.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 08 快速卷积 Fast Convolution.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 10 递归滤波器 Pipelined and Parallel Recursive and Adaptive Filters.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 07 脉动阵列 Systolic Architecture.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 06 折叠 Folding.pdf

- 电子科技大学:《集成电路可测性设计 VLSIDesign》课程教学资源(课件讲稿)第12章 Soc测试(2/2)IEEE P1500 嵌入式核可测性标准.pdf

- 《现代编码理论与技术》课程教学资源(学习资料)Turbo码启示录——从默默无闻到广泛应用.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第三章 线性分码组.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第五章 循环码(陆以勤).doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第四章 多项式环与有限域.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(讲义)第六章 循环码的译码.doc

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第一章 纠错码的基本概念.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第二章 代数初步(陆以勤).ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第三章 线性分码组.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第四章 多项式环与有限域.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第五章 循环码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第六章 循环码的译码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第七章 BCH码与Goppa码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第十章 卷积码基础.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第十三章 Turbo码.ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(PPT课件讲稿)第十四章 LDPC码(Low-Density Check-Parity Code).ppt

- 华南理工大学:《现代编码理论与技术》课程教学资源(习题)第二章 代数初步.pdf

- 华南理工大学:《现代编码理论与技术》课程教学资源(习题)第三章 线性分码组.pdf

- 华南理工大学:《现代编码理论与技术》课程教学资源(习题)第四章 多项式环与有限域.pdf

- 华南理工大学:《现代编码理论与技术》课程教学资源(习题)第五章 循环码.pdf