《数字电子技术》课程教学资源(实验指导)实验二 组合逻辑电路与集成器件

实验二:组合逻辑电路与集成器件一、实验目的:1、了解集成数据选择器74LS151、加法器74LS283、数值比较器74LS85的管脚排列和管脚功能;2、了解集成编码器74LS148、译码器74LS47和数码管(共阳极)的管脚排列和管脚功能:3、掌握集成数据选择器、加法器、数值比较器的性能及使用方法;4、掌握集成编码器、译码器和数码管的性能及使用方法;5、掌握用MSI中规模集成器件设计组合逻辑电路的方法,用实验验证所设计电路的功能二、实验内容1、某工厂有三个车间A、B,C,有一个自备电站,站内有二台发电机M和N,N的发电能力是M的两倍,如果一个车间开工,启动M就可以满足要求;如果两个车间开工,启动N就可以满足要求;如果三个车间同时开工,同时启动M、N才能满足要求。试用异或门(74LS86)和与非门(74LS00)设计一个控制电路,因车间的开工情况来控制M和N的启动。2、用译码器 74LS138和多路数据选择器74LS151设计一个信息的“并行一串行一并行”传送电路。3、利用4位集成全加器74LS283设计一个BCD码加法器。结构示意图见下图所示。注加6补偿电路甲修正信号产生电路图 BCD码加法器原理框图4、译码、显示电路的设计(74LS47、共阳极数码显示管)译码、显示原理电路框图如下图所示。A、A2、Ar、A。接逻辑开关,作为十进制数据输入,用数码管显示其数字

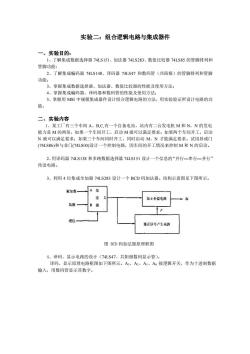

实验二:组合逻辑电路与集成器件 一、实验目的: 1、了解集成数据选择器 74LS151、加法器 74LS283、数值比较器 74LS85 的管脚排列和 管脚功能; 2、了解集成编码器 74LS148、译码器 74LS47 和数码管(共阳极)的管脚排列和管脚 功能; 3、掌握集成数据选择器、加法器、数值比较器的性能及使用方法; 4、掌握集成编码器、译码器和数码管的性能及使用方法; 5、掌握用 MSI 中规模集成器件设计组合逻辑电路的方法,用实验验证所设计电路的功 能。 二、实验内容 1、某工厂有三个车间 A、B,C,有一个自备电站,站内有二台发电机 M 和 N,N 的发电 能力是 M 的两倍,如果一个车间开工,启动 M 就可以满足要求;如果两个车间开工,启动 N 就可以满足要求;如果三个车间同时开工,同时启动 M、N 才能满足要求。试用异或门 (74LS86)和与非门(74LS00)设计一个控制电路,因车间的开工情况来控制 M 和 N 的启动。 2、用译码器 74LS138 和多路数据选择器 74LS151 设计一个信息的“并行—串行—并行” 传送电路。 3、利用 4 位集成全加器 74LS283 设计一个 BCD 码加法器。结构示意图见下图所示。 图 BCD 码加法器原理框图 4、译码、显示电路的设计(74LS47、共阳极数码显示管)。 译码、显示原理电路框图如下图所示。A3、A2、A1、A0 接逻辑开关,作为十进制数据 输入,用数码管显示其数字

74LS47TTTTASAIA图译码、显示原理电路框图

图 译码、显示原理电路框图

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电子技术》课程教学资源(实验指导)实验三 锁存器、触发器及其应用.doc

- 《数字电子技术》课程教学资源(实验指导)实验一 门电路参数和功能的测试.doc

- 《数字电子技术》课程教学资源(实验指导)实验四 时序逻辑电路.doc

- 《机械工程实训》课程PPT教学课件(金工实习)特种加工.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)数控铣削编程加工.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)数控编程与操作.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)钳工.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)铸造工艺特点.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)铣工(铣削加工工艺特点).ppt

- 《机械工程实训》课程PPT教学课件(金工实习)机械加工基础知识(金属切削加工基础知识).ppt

- 《机械工程实训》课程PPT教学课件(金工实习)车工(车削加工工艺特点).ppt

- 《机械工程实训》课程PPT教学课件(金工实习)磨工(磨削加工工艺特点).ppt

- 《机械工程实训》课程PPT教学课件(金工实习)实习概论.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)锻压实习.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)工程材料及热处理.ppt

- 《机械工程实训》课程PPT教学课件(金工实习)焊接实习.ppt

- 《机械工程实训》课程授课教案(讲义,共十单元).doc

- 《机械工程实训》课程教学大纲(金工实习).pdf

- 《发动机构造》课程授课教案(讲义)第八章 发动机点火系.doc

- 《发动机构造》课程教学课件(讲稿)第三章 配气机构.pdf

- 《数字电子技术》课程教学资源(实验指导)实验五 脉冲发生电路与555集成定时器的功能及应用.doc

- 《数字电子技术》课程教学资源(PPT课件)第一章 数制和码制.ppt

- 《数字电子技术》课程教学资源(PPT课件)第二章 逻辑代数基础.ppt

- 《数字电子技术》课程教学资源(PPT课件)第四章 组合逻辑电路.ppt

- 《数字电子技术》课程教学资源(PPT课件)第三章 门电路.ppt

- 《数字电子技术》课程教学资源(PPT课件)第五章 触发器.ppt

- 《数字电子技术》课程教学资源(PPT课件)第六章 时序逻辑电路.ppt

- 《数字电子技术》课程教学资源(PPT课件)第十一章 数-模和模-数转换.ppt

- 《数字电子技术》课程教学资源(PPT课件)第八章 可编程逻辑器件.ppt

- 《数字电子技术》课程教学资源(PPT课件)第十章 脉冲波形的产生和整形.ppt

- 《数字电子技术》课程教学资源(PPT课件)第七章 半导体存储器.ppt

- 《汽车底盘构造》课程教学大纲 Automotive Chassis Construction.pdf

- 《汽车底盘构造》课程实习指导书(共七个实习).pdf

- 《汽车底盘构造》课程教学课件(PPT讲稿)第一章 汽车传动系统 1.1 传动系统概述.ppt

- 《汽车底盘构造》课程教学课件(PPT讲稿)第一章 汽车传动系统 1.4 万向传动装置.ppt

- 《汽车底盘构造》课程教学课件(PPT讲稿)第一章 汽车传动系统 1.3 变速器与分动器.ppt

- 《汽车底盘构造》课程教学课件(PPT讲稿)第一章 汽车传动系统 1.5 驱动桥.ppt

- 《汽车底盘构造》课程教学课件(PPT讲稿)第二章 汽车行驶系统 2.1 汽车行驶系统概述.ppt

- 《汽车底盘构造》课程教学课件(PPT讲稿)第一章 汽车传动系统 1.2 离合器.ppt

- 《汽车底盘构造》课程教学课件(PPT讲稿)第二章 汽车行驶系统 2.2 车架和承载式车身.ppt