《数字逻辑电路》课程教学课件(PPT讲稿)第八章 可编辑逻辑器件

第八章可编程逻辑器件 。8.1概述 。8.2现场可编程逻辑阵列(FPLA) 。8.3可编程阵列逻辑(PAL)D ●8.4通用阵列逻辑(GAL)D 。8.5可擦除的可编程逻辑器件(EPLD) ● 8.6现场可编程门阵列(FPGA)D 8.7PLD的编程(无图)〉 ●8.8在系统可编程逻辑器件(ISP一PLD)D 返回 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 1 第八章 可编程逻辑器件 ⚫ 8.1 概述 ⚫ 8.2 现场可编程逻辑阵列(FPLA) ⚫ 8.3 可编程阵列逻辑(PAL) ⚫ 8.4 通用阵列逻辑(GAL) ⚫ 8.5 可擦除的可编程逻辑器件(EPLD) ⚫ 8.6 现场可编程门阵列(FPGA) ⚫ 8.7 PLD的编程(无图) ⚫ 8.8 在系统可编程逻辑器件(ISP-PLD) 返回

8.1概述 图8.1.1PLD电路中门电路的惯用画法) (a)与门 (b)输出恒等于0的与门 (c)或门 ● (d)互补输出的缓冲器 (e)三态输出的缓冲器 返 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 2 8.1 概 述 ⚫ 图8.1.1 PLD电路中门电路的惯用画法 (a)与门 ⚫ (b)输出恒等于0的与门 ⚫ (c)或门 ⚫ (d)互补输出的缓冲器 ⚫ (e)三态输出的缓冲器 返回

图8.1.1 PLD电路中门电路的惯用画法 (a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器 B C D D 4'B (a) g 4二 (d) e PR/OE' 8-1-1 返回 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 3 图8.1.1 PLD电路中门电路的惯用画法 (a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器 返回

*8.2 现场可编程逻辑阵列(FPLA) ●图8.2.1FPLA的基本电路结构 ●图8.2.2FPLA的异或输出结构D ●图8.2.3时序逻辑型FPLA的电路结构 返 2006年 新疆大学信息科学与工程学院 4 <数字电路课题组

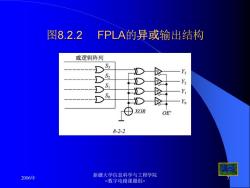

2006年 新疆大学信息科学与工程学院 4 *8.2 现场可编程逻辑阵列(FPLA) ⚫ 图8.2.1 FPLA的基本电路结构 ⚫ 图8.2.2 FPLA的异或输出结构 ⚫ 图8.2.3 时序逻辑型 FPLA的电路结构 返回

Y3三 ABCD +ABCD Y2=AC+BD YI-ADB Y0= C⊙D 返回 2006年 新疆大学信息科学与工程学院

2006 年 新疆大学信息科学与工程学院 5 返回

图8.2.1 FPLA的基本电路结构 A区 B D 与逻辑阵列 00000000 OE' 或逻辑阵列 8-2-1 2006年 新疆大学信息科学与工程学院 6

2006年 新疆大学信息科学与工程学院 6 图8.2.1 FPLA的基本电路结构

图8.2.2 FPLA的异或输出结构 或逻辑阵列 S3 D S2 Y D D D S Yo XOR OE' 8-2-2 返回 2006年 新疆大学信息科学与工程学院 7

2006年 新疆大学信息科学与工程学院 7 图8.2.2 FPLA的异或输出结构 返回

图8.2.3 时序逻辑型FPLA的电路结构 PR/OE A D 种种拉册种种 B D D Y D &2-3 返回 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 8 图8.2.3 时序逻辑型 FPLA的电路结构 返回

8.3可编程阵列逻辑PAL PAL的与阵列是可编程的而或阵列不可编程,类似 于一个己经写入信息的ROM,但它的与阵列是可编 程的。 输入 与阵列 (可编程》 或阵列 输出 不可编程 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 9 PAL的与阵列是可编程的而或阵列不可编程,类似 于一个已经写入信息的ROM,但它的与阵列是可编 程的。 不可编程 8.3可编程阵列逻辑PAL

8.3.1PAL的基本电路结构 PAL器件当中最简单一种电路结构形式,它仅包含一个可编程的与 逻辑阵列和一个固定的或逻辑阵列,没有附加其他的输出电路 与逻辑库列 或逻辑阵列 乘积项 Y I2 乘积项 Y 乘积项 I4- 乘积项 8-3-1 2006年 新疆大学信息科学与工程学院 10

2006年 新疆大学信息科学与工程学院 10 8.3.1 PAL的基本电路结构 PAL器件当中最简单一种电路结构形式,它仅包含一个可编程的与 逻辑阵列和一个固定的或逻辑阵列,没有附加其他的输出电路

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字逻辑电路》课程教学课件(PPT讲稿)第七章 半导体存储器.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第六章 时序逻辑电路.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第五章 触发器.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第十一章 数-模和模-数转换.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第十章 脉冲波形的产生和整形.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第二章 逻辑代数基础.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第三章 门电路.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第一章 数制与码制.pps

- 新疆大学:《数字逻辑电路》课程教学资源(PPT讲稿)数字电路课程小结及试题分析(2010).pps

- 《数字逻辑电路》课程教学资源(试卷习题)样卷四(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷四(试题).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷二(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷二(试题).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷三(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷三(试题).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷一(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷一(试题).doc

- 《数字逻辑电路》课程教学资源(实验指导)多路智力竞赛抢答器.doc

- 《数字逻辑电路》课程教学资源(实验指导)可控定时器实验.doc

- 《数字逻辑电路》课程教学资源(实验指导)多功能数字钟的设计.doc

- 《数字逻辑电路》课程教学课件(PPT讲稿)第四章 组合逻辑电路.pps

- 新疆大学:《数字信号处理》课程授课教案(讲义,共六章,含绪论).pdf

- 《数字信号处理》课程教学习题解答.pdf

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)绪论DSP.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)幂级数展开法(长除法).pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)用留数定理求逆Z变换.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第一章 离散时间信号与系统.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)部分分式.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第三章 离散傅里叶变换及其快速算法 3.1 离散傅立叶变换 3.2 利用DFT进行连续信号的频谱分析.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第三章 离散傅里叶变换及其快速算法 3.3 快速傅立叶变换 3.4 关于FFT应用中的几个问题.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第二章 信号的采样与重建.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第五章 有限长单位脉冲响应(FIR)滤波器的设计方法.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第六章 数字信号处理系统的实现 6.6 数字信号处理硬件(数字信号处理器).ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第六章 数字信号处理系统的实现 6.1 数字滤波器的结构 6.2 量化与量化误差 6.3 有限字长运算对数字滤波器的影响 6.4 极限环振荡 6.5 系数量化对系数滤波器的影响.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.1 滤波器的基本原理.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.2模拟低通滤波器设计.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.3 根据模拟滤波器设计IIR滤波器.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.4 从模拟滤波器低通原型到各种数字滤波器的频率变换(原型变换)4.5 从低通数字滤波器到各种数字滤波器的频率变换(Z平面变换法).ppt

- 榆林学院:《数字电子技术基础》课程授课教案(讲义,任课教师:高燕).pdf

- 石河子大学:《信号与系统》课程授课教案(任课教师:查志华).doc