《数字逻辑电路》课程教学课件(PPT讲稿)第六章 时序逻辑电路

第6章时序逻辑电路 06.1 概述 ○6.2时序逻辑电路的分析方法 ○63若干常用的时序逻辑电路 ○6.4时序逻辑电路的设计方法 06.5 时序逻辑电路中的竞争一冒险现象

1 第6章 时序逻辑电路 ⚫ 6.1 概述 ⚫ 6.2 时序逻辑电路的分析方法 ⚫ 6.3 若干常用的时序逻辑电路 ⚫ 6.4 时序逻辑电路的设计方法 ⚫ 6.5 时序逻辑电路中的竞争-冒险现象

6.1概述 一、时序逻辑电路的特点 定义:时序逻辑电路在任一时刻的输出不仅取决于当时的输 入信号,而且还取决于电路的原来状态(或者说,还与以 前的输入有关)。 电路构成: 存储电路(主要是触发器,必不可少) 组合逻辑电路(可选)。 时序逻辑电路的状态是由存储电路来记忆和表示的

2 一、时序逻辑电路的特点 定义:时序逻辑电路在任一时刻的输出不仅取决于当时的输 入信号,而且还取决于电路的原来状态(或者说,还与以 前的输入有关)。 电路构成: ⚫ 存储电路(主要是触发器,必不可少) ⚫ 组合逻辑电路(可选)。 ⚫ 时序逻辑电路的状态是由存储电路来记忆和表示的。 6.1 概述

时序电路举例: b 串行加法器电路 Ci-1 CI CO 串行加法: D CLK 是指在将两个多位数相加 时,采用从低位到高位逐位相 加的方式完成相加运算

3 时序电路举例: 串行加法器电路 串行加法: 是指在将两个多位数相加 时,采用从低位到高位逐位相 加的方式完成相加运算

二、时序电路的一般结构形式与功能描述方法 组合逻辑电路 91 存储电路 9 其中: X(X1X2,X)代表输入信号; Y(y1y2,y)代表输出信号; Z(z1z2,.Zk)代表存储电路的输入信号; Q(q1q2,q)代表存储电路的输出;

4 二、时序电路的一般结构形式与功能描述方法 其中: X(x1 ,x2 ,.,xi)代表输入信号; Y(y1 ,y2 , .yj)代表输出信号; Z(z1 ,z2 , .zk)代表存储电路的输入信号; Q(q1 ,q2 , .ql)代表存储电路的输出;

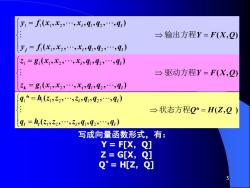

y1=f(x1,x2,.,x1,41,92,.,41) 三输出方程Y=F(X,2) y1=f(x1,x2,.,X,41,42,.,4) Z1=81(x1,x2,3Xi,41,92,.341) →驱动方程Y=F(X,2) 3k=81(X1,X2,.,X)41,92,.,41) 41*=h1(31,32,.,z1,41,42,.391) →状态方程Q*=H(Z,2) 41=h(31,z2,z41,92,.,41) 写成向量函数形式,有: Y=F[X,Q] Z=G[X,Q] Q*=H[Z, Q]

5 写成向量函数形式,有: Y = F[X ,Q] Z = G[X ,Q] Q* = H[Z ,Q] ( , ) ( , , , , , , , ) ( , , , , , , , ) Y F X Q y f x x x q q q y f x x x q q q j i l i l = == 输出方程 1 1 2 1 2 1 1 1 2 1 2 ( , ) ( , , , , , , , ) ( , , , , , , , ) Y F X Q z g x x x q q q z g x x x q q q k i l i l = == 驱动方程 1 1 2 1 2 1 1 1 2 1 2 * ( , ) ( , , , , , , , ) * ( , , , , , , , ) Q H Z Q q h z z z q q q q h z z z q q q l l i l i l = == 状态方程 1 2 1 2 1 1 1 2 1 2

三、时序电路的分类 1.同步时序电路与异步时序电路 同步:存储电路中所有触发器的时钟使用统一的CLK,状态变 化发生在同一时刻 异步:没有统一的CLK,触发器状态的变化有先有后 2. Meal y型和Moore型 Mealy:型: Y=F(X,2) 与X、O有关 Moore型: Y=F(2) 仅取决于电路状态

6 1. 同步时序电路与异步时序电路 同步:存储电路中所有触发器的时钟使用统一的CLK,状态变 化发生在同一时刻 异步:没有统一的CLK,触发器状态的变化有先有后 2. Mealy型和Moore型 Mealy型: Moore型: 三、时序电路的分类 仅取决于电路状态 与 、 有关 ( ) ( , ) Y F Q Y F X Q X Q = =

6.2时序逻辑电路的分析方法 时序逻辑电路可分为: 同步时序电路和异步时序电路。 6.2.1同步时序逻辑电路分析方法 ◆从给定的逻辑图中写出每个触发器的驱动方程。 ◆把得到的驱动方程代入相应触发器的特性方程, 得状态方程,从而得到整个电路的状态方程组。 ◆根据逻辑图写出电路的输出方程。 返回目录

7 时序逻辑电路可分为: 同步时序电路和异步时序电路。 6.2 时序逻辑电路的分析方法 6.2.1 同步时序逻辑电路分析方法 ◆从给定的逻辑图中写出每个触发器的驱动方程。 ◆把得到的驱动方程代入相应触发器的特性方程, 得状态方程,从而得到整个电路的状态方程组。 ◆根据逻辑图写出电路的输出方程

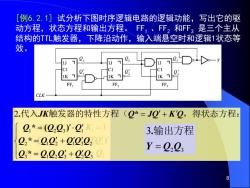

[例6.2.1]试分析下图时序逻辑电路的逻辑功能,写出它的驱 动方程,状态方程和输出方程。FF,、FF2和FF3是三个主从 结构的TTL触发器,下降沿动作,输入端悬空时和逻辑1状态等 效。 1K FF. FF 2.代入JK触发器的特性方程(Q*=JQ'+K'Q,得状态方程: 2*=(2223)'21K,= 3.输出方程 22*=22,+2222 Y=0223 2*=2222+25Q

8 [例6.2.1] 试分析下图时序逻辑电路的逻辑功能,写出它的驱 动方程,状态方程和输出方程。 FF1 、FF2 和FF3 是三个主从 结构的TTL触发器,下降沿动作,输入端悬空时和逻辑1状态等 效。 = = = = = = 3 1 2 3 2 2 1 2 1 3 1 2 3 1 1 1 J Q Q K Q J Q K Q Q J Q Q K , , ( ) ( ) , .写驱动方程: = + = + = = + 3 1 2 3 2 3 2 1 2 1 3 2 1 2 3 1 2 Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q JK Q JQ K Q * * * ( ) .代入 触发器的特性方程( * ,得状态方程: 2 3 3 Y = Q Q .输出方程

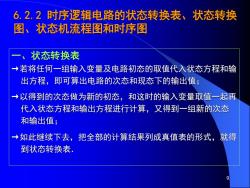

6.2.2时序逻辑电路的状态转换表、状态转换 图、状态机流程图和时序图 一、状态转换表 →若将任何一组输入变量及电路初态的取值代入状态方程和输 出方程,即可算出电路的次态和现态下的输出值; →以得到的次态做为新的初态,和这时的输入变量取值一起再 代入状态方程和输出方程进行计算,又得到一组新的次态 和输出值; →如此继续下去,把全部的计算结果列成真值表的形式,就得 到状态转换表

9 6.2.2 时序逻辑电路的状态转换表、状态转换 图、状态机流程图和时序图 一、状态转换表 →若将任何一组输入变量及电路初态的取值代入状态方程和输 出方程,即可算出电路的次态和现态下的输出值; →以得到的次态做为新的初态,和这时的输入变量取值一起再 代入状态方程和输出方程进行计算,又得到一组新的次态 和输出值; →如此继续下去,把全部的计算结果列成真值表的形式,就得 到状态转换表.

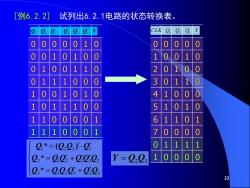

[例6.2.2】试列出6.2.1电路的状态转换表。 e,e,e CLK 00 0 0 010 0 0 0 0 0 00 100 100 1 0 010 01 10 2010 0 01 1 1000 30110 100 1010 4 100 0 10 1100 5 1 0 1100 1 6 1 1110001 7 0 2*=(0223)'·2 Q2*=222+2222 Y=2223 0 Q3*=2222+050 10

10 [例6.2.2] 试列出6.2.1电路的状态转换表。 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 1 0 0 1 1 1 0 0 0 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 1 0 0 0 0 0 1 0 0 1 0 2 0 1 0 0 3 0 1 1 0 4 1 0 0 0 5 1 0 1 0 6 1 1 0 1 7 0 0 0 0 0 1 1 1 1 1 0 0 0 0 CLK Q3 Q2 Q1 Y = + = + = 3 1 2 3 2 3 2 1 2 1 3 2 1 2 3 1 Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q * * * ( ) Y = Q2 Q3 Q Q Q Q Q Q Y * * * 3 2 1 3 2 1

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字逻辑电路》课程教学课件(PPT讲稿)第五章 触发器.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第十一章 数-模和模-数转换.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第十章 脉冲波形的产生和整形.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第二章 逻辑代数基础.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第三章 门电路.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第一章 数制与码制.pps

- 新疆大学:《数字逻辑电路》课程教学资源(PPT讲稿)数字电路课程小结及试题分析(2010).pps

- 《数字逻辑电路》课程教学资源(试卷习题)样卷四(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷四(试题).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷二(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷二(试题).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷三(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷三(试题).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷一(答案).doc

- 《数字逻辑电路》课程教学资源(试卷习题)样卷一(试题).doc

- 《数字逻辑电路》课程教学资源(实验指导)多路智力竞赛抢答器.doc

- 《数字逻辑电路》课程教学资源(实验指导)可控定时器实验.doc

- 《数字逻辑电路》课程教学资源(实验指导)多功能数字钟的设计.doc

- 《数字逻辑电路》课程教学资源(实验指导)数字存储示波器使用手册.doc

- 《数字逻辑电路》课程教学资源(实验指导)门电路参数测试.doc

- 《数字逻辑电路》课程教学课件(PPT讲稿)第七章 半导体存储器.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第八章 可编辑逻辑器件.pps

- 《数字逻辑电路》课程教学课件(PPT讲稿)第四章 组合逻辑电路.pps

- 新疆大学:《数字信号处理》课程授课教案(讲义,共六章,含绪论).pdf

- 《数字信号处理》课程教学习题解答.pdf

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)绪论DSP.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)幂级数展开法(长除法).pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)用留数定理求逆Z变换.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第一章 离散时间信号与系统.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)部分分式.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第三章 离散傅里叶变换及其快速算法 3.1 离散傅立叶变换 3.2 利用DFT进行连续信号的频谱分析.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第三章 离散傅里叶变换及其快速算法 3.3 快速傅立叶变换 3.4 关于FFT应用中的几个问题.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第二章 信号的采样与重建.pptx

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第五章 有限长单位脉冲响应(FIR)滤波器的设计方法.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第六章 数字信号处理系统的实现 6.6 数字信号处理硬件(数字信号处理器).ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第六章 数字信号处理系统的实现 6.1 数字滤波器的结构 6.2 量化与量化误差 6.3 有限字长运算对数字滤波器的影响 6.4 极限环振荡 6.5 系数量化对系数滤波器的影响.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.1 滤波器的基本原理.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.2模拟低通滤波器设计.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.3 根据模拟滤波器设计IIR滤波器.ppt

- 新疆大学:《数字信号处理》课程教学课件(PPT讲稿)第四章 无限长单位脉冲响应(IIR)滤波器设计 4.4 从模拟滤波器低通原型到各种数字滤波器的频率变换(原型变换)4.5 从低通数字滤波器到各种数字滤波器的频率变换(Z平面变换法).ppt