电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 2.2 FPGA Design with Verilog(Supplementary)

Topic2:FPGA Design with Verilog FPGA Design Method Design flow tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples 。RTL level design Components of Datapath Components of Controller Supplementary ·Synthesizable 。Some experiences 。Other syntax rules 2021/1/13 ASIC Design,by Yan Bo 3

ASIC Design, by Yan Bo Topic2: FPGA Design with Verilog FPGA Design Method Design flow & tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples • RTL level design • Components of Datapath • Components of Controller Supplementary • Synthesizable • Some experiences • Other syntax rules 2021/1/13 3

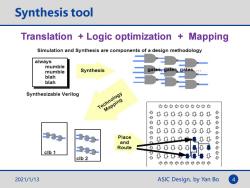

Synthesis tool Translation Logic optimization Mapping Simulation and Synthesis are components of a design methodology always mumble mumble Synthesis gates,gates,gates, blah blah Synthesizable Verilog Technology Mapping 白白白白白白白白白白 800000000 0中中中中中中中中 0 中中中中中中中中 Place and 00n是09 0 Route clb1 clb2 中中中中中中中单中中 2021/1/13 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo Synthesis tool 2021/1/13 4 Translation + Logic optimization + Mapping

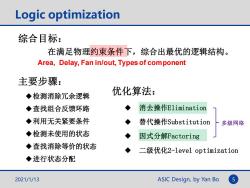

Logic optimization 综合目标: 在满足物理约束条件下,综合出最优的逻辑结构。 Area,Delay,Fan in/out,Types of component 主要步骤: 优化算法: ◆检测消除冗余逻辑 ◆查找组合反馈环路 消去操作Elimination ◆利用无关紧要条件 替代操作Substitution ,上多级网络 ◆检测未使用的状态 因式分解Factoring ◆查找消除等价的状态 二级优化2-level optimization ◆进行状态分配 2021/1/13 ASIC Design,by Yan Bo 5

ASIC Design, by Yan Bo Logic optimization 2021/1/13 5 主要步骤: ◆检测消除冗余逻辑 ◆查找组合反馈环路 ◆利用无关紧要条件 ◆检测未使用的状态 ◆查找消除等价的状态 ◆进行状态分配 综合目标: 在满足物理约束条件下,综合出最优的逻辑结构。 Area, Delay, Fan in/out, Types of component 优化算法: ◆ 消去操作Elimination ◆ 替代操作Substitution ◆ 因式分解Factoring ◆ 二级优化2-level optimization 多级网络

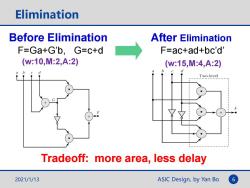

Elimination Before Elimination After Elimination F=Ga+G'b,G=c+d F=ac+ad+bc'd' w:10,M:2,A:2) (w:15,M:4,A:2) b c a Two-level Tradeoff:more area,less delay 2021/1/13 ASIC Design,by Yan Bo 6

ASIC Design, by Yan Bo Elimination 2021/1/13 6 After Elimination F=ac+ad+bc’d’ Before Elimination F=Ga+G’b, G=c+d (w:10,M:2,A:2) (w:15,M:4,A:2) Tradeoff: more area, less delay

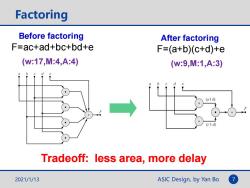

Factoring Before factoring After factoring F=ac+ad+bc+bd+e F=(a+b)(c+d)+e w:17,M:4,A:4) (W:9,M:1,A:3) b (a1b) (c1d) Tradeoff:less area,more delay 2021/1/13 ASIC Design,by Yan Bo 7

ASIC Design, by Yan Bo Factoring 2021/1/13 7 Tradeoff: less area, more delay After factoring F=(a+b)(c+d)+e Before factoring F=ac+ad+bc+bd+e (w:17,M:4,A:4) (w:9,M:1,A:3)

Topic2:FPGA Design with Verilog FPGA Design Method Design flow tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples 。RTL level design Components of Datapath Components of Controller Supplementary 。Synthesizable ·Some experiences 。Other syntax rules 2021/1/13 ASIC Design,by Yan Bo 8

ASIC Design, by Yan Bo Topic2: FPGA Design with Verilog FPGA Design Method Design flow & tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples • RTL level design • Components of Datapath • Components of Controller Supplementary • Synthesizable • Some experiences • Other syntax rules 2021/1/13 8

Some experiences >Balance architecture Share resources Gated signal >Assignment statement Accident Intentional Latch 2021/1/13 ASIC Design,by Yan Bo 9

ASIC Design, by Yan Bo Some experiences 2021/1/13 9 ➢ Balance architecture ➢ Share resources ➢ Gated signal ➢Assignment statement ➢ Accident / Intentional Latch

Some experiences Balance architecture Share resources Gated signal >Assignment statement Accident Intentional Latch 2021/1/13 ASIC Design,by Yan Bo 10

ASIC Design, by Yan Bo Some experiences 2021/1/13 10 ➢ Balance architecture ➢ Share resources ➢ Gated signal ➢Assignment statement ➢ Accident / Intentional Latch

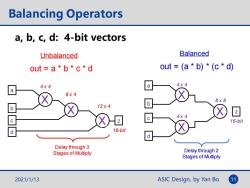

Balancing Operators a,b,c,d:4-bit vectors Unbalanced Balanced out a b c d out =(a b)*(c d) a 4X4 a 4X4 8X4 8X8 12x4 回 4X4 16-bit 16-bit Delay through 3 Stages of Multiply Delay through 2 Stages of Multiply 2021/1/13 ASIC Design,by Yan Bo 11

ASIC Design, by Yan Bo Balancing Operators a, b, c, d: 4-bit vectors out = a * b * c * d X a b X c X d z X a b out = (a * b) * (c * d) X c d X z Unbalanced Balanced 4 x 4 8 x 4 12 x 4 16-bit 4 x 4 4 x 4 8 x 8 16-bit Delay through 3 Stages of Multiply Delay through 2 Stages of Multiply 2021/1/13 11

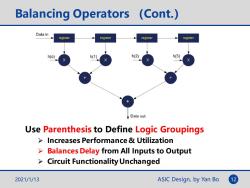

Balancing Operators (Cont.) Data in register register register register h(o) h(1) h(2) h(3) Data out Use Parenthesis to Define Logic Groupings Increases Performance Utilization >Balances Delay from All Inputs to Output Circuit Functionality Unchanged 2021/1/13 ASIC Design,by Yan Bo 12

ASIC Design, by Yan Bo Balancing Operators (Cont.) 2021/1/13 12 Use Parenthesis to Define Logic Groupings ➢ Increases Performance & Utilization ➢ Balances Delay from All Inputs to Output ➢ Circuit Functionality Unchanged

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 2.1 FPGA Design with Verilog(FPGA Design Method、Design Examples).pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 1.3 Introduction-Our Course.pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 1.2 Introduction-ASIC Design.pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 1.1 Introduction-IC technology.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第20讲 高阶有源滤波器.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第19讲 有源滤波器.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第9讲 信号流图分析法.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第6讲 网络函数拓扑法.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第5讲 不定导纳函数.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第4讲 图论与电路方程.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第3讲 图论.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第18讲 电抗网络综合(电抗梯形滤波器综合).pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第17讲 无源双口网络参数(电抗二端口综合).pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第13讲 无源网络综合基础.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第12讲 无源网络函数.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第16讲 贝塞尔函数和频率变换.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第15讲 滤波器逼近方法.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第14讲 滤波器理论基础.pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第11讲 灵敏度分析(2/2).pdf

- 电子科技大学:《现代网络理论与综合 Theory and Synthesize of Electric Network》课程教学资源(课件讲稿)第10讲 灵敏度分析(1/2).pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 3 Verification and Test.pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design》课程教学资源(课件讲稿)Topic 4 VLSI for DSP.pdf

- 电子科技大学:《半导体封装测试与可靠性 Packaging,Testing and Reliability of Semiconductor》课程教学资源(教学大纲,思政版).pdf

- 电子科技大学:《半导体封装测试与可靠性 Packaging,Testing and Reliability of Semiconductor》课程教学资源(课件讲稿,思政版).pdf

- 电子科技大学:《电子无源元件工艺实验》课程实验课件讲稿 Electronic Passive Components Process Experiment Course(主讲:戴丽萍).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(教学大纲,凌翔).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 00 简介 Introduction to VLSI(凌翔).pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 01 导论 Introduction to Digital Signal Processing Systems.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 02 迭代界 Iteration Bound.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 03 流水与并行 Pipelining and Parallel Processing.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 04 重定时 Retiming.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 05 展开 Unfolding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 06 折叠 Folding.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 07 脉动阵列 Systolic Architecture.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 10 递归滤波器 Pipelined and Parallel Recursive and Adaptive Filters.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 08 快速卷积 Fast Convolution.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 09 算法强度缩减 Algorithmic strength reduction in filters and transforms.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 11 缩放噪声 Scaling and Roundoff Noise.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 13 位级运算 Bit-Level Arithmetic Architectures.pdf

- 电子科技大学:《DSP算法实现技术与架构 VLSI Digital Signal Processing Systems Design and Implementation》课程教学资源(课件讲稿)Chapter 14 冗余运算 Redundant Arithmetic.pdf