《微型计算机技术及应用》课程授课教案(讲义)第2章 51系列单片机系统结构

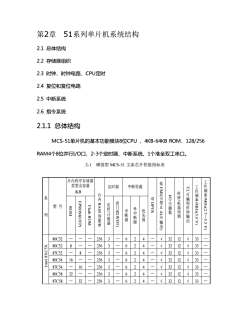

第2章51系列单片机系统结构2.1总体结构2.2 存储器组织2.3时钟、时钟电路、CPU定时2.4复位和复位电路2.5中断系统2.6指令系统2.1.1总体结构MCS-51单片机的基本功能模块8位CPU、4KB-64KBROM、128/256RAM4个8位并行I/O口、2-3个定时器、中断系统、1个准全双工串口。2-1增强型MCS-51主流芯片性能指标表片内程序存储器工作频率/MHz(2.7~5.5V)低类型及容量定时器中断资源工作频率/MHz(5.0V)T2可编程时钟输出EMI(可禁止)/KB时钟/机器周期片内I/O引脚数系双DPTR看EPROM(OTP)RAM定时/计数器型号Flash ROM门狗(WDT)ROM外中断源中断源优先级ALE输出)容量/BY624V3212V25633380C3232 33256361280C5224y8V32123336287C52256V843325636321280C54162V43387C54256363212162432256632123380C58313387C5832256322

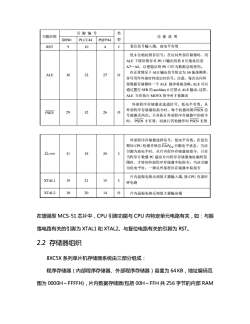

第2章 51系列单片机系统结构 2.1 总体结构 2.2 存储器组织 2.3 时钟、时钟电路、CPU定时 2.4 复位和复位电路 2.5 中断系统 2.6 指令系统 2.1.1 总体结构 MCS-51单片机的基本功能模块8位CPU 、4KB-64KB ROM、128/256 RAM4个8位并行I/O口、2-3个定时器、中断系统、1个准全双工串口。 2-1 增强型 MCS-51 主流芯片性能指标表 系 列 型 号 片内程序存储器 类型及容量 /KB 片 内RAM 容 量/B 定时器 中断资源 双DPTR 低EMI( 可 禁 止ALE 输 出) I/O 引 脚 数 时 钟/ 机 器 周 期 T2 可 编 程 时 钟 输 出 工 作 频 率/MHz(5.0 V) 工 作 频 率/MHz(2.7 ~5.5 V) ROM EPROM(OTP) Flash ROM 定 时/ 计 数 器 看 门 狗(WDT) 中 断 源 外 中 断 源 优 先 级 Intel 8XC5X 80C32 — — — 256 3 — 6 2 4 — √ 32 12 √ 33 — 80C52 8 — — 256 3 — 6 2 4 — √ 32 12 √ 33 — 87C52 — 8 — 256 3 — 6 2 4 — √ 32 12 √ 33 — 80C54 16 — — 256 3 — 6 2 4 — √ 32 12 √ 33 — 87C54 — 16 — 256 3 — 6 2 4 — √ 32 12 √ 33 — 80C58 32 — — 256 3 — 6 2 4 — √ 32 12 √ 33 — 87C58 — 32 — 256 3 — 6 2 4 — √ 32 12 √ 33 —

片内程序存储低工作频率/MHz(2.7 ~5.5 V)工作频率/MHz5.0V)器类型及容量EMI(可禁止)T2可编程时钟输出中断资源定时器片内RAM容量/E时/KBI/O钟系双DPT/机器周引脚EPROM(OTP)石型号定时/计数器Flash ROM外中优先级ROMALE)数狗(WDT)列期断断出源源VV1283624321233P80C316-732123316P80C322566241283212V3316P80C51440AV3316P80C52825632o4VV33P80C541632121625633P80C583212V16256323316P87C512842123316P87C522563213316P87C5412162564V32V333225624V3212V16P87C586331283212V一P89C51462V33P89C523212V8256364VV一3624NV3212V33P89C5416256一-624NV3212A33P89C58322563-XV128623212/633/3016P80C31X23V12V256643212/6V33/3016P80C32X23P80C51X21287624VV3212/6V33/30164243233/302566V12/6V16P80C52X28V624VVZXXSOXSP80C54X23212/633/30161625633241V3212/6V33/30P80C58X2256362161283212/6V33/3016P87C51X2.462413004P87C52X225662V3212/633/308V161232P87C54X225664VV12/6V33/30161643212/633/30P87C58X2322566216V624128V3212/6V33/20P89C51X2x16243212/633/20P89C52X282563VP89C54X21625663212/6V33/203241P89C58X233/203212/6250

Philips P8XC5XX2 P80C31X2 — — — 128 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P80C32X2 — — — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P80C51X2 4 — — 128 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P80C52X2 8 — — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P80C54X2 16 — — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P80C58X2 32 — — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P87C51X2 — 4 — 128 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P87C52X2 — 8 — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P87C54X2 — 16 — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P87C58X2 — 32 — 256 3 — 6 2 4 √ √ 32 12/6 √ 33/30 16 P89C51X2 — — 4 128 3 — 6 2 4 √ √ 32 12/6 √ 33/20 — P89C52X2 — — 8 256 3 — 6 2 4 √ √ 32 12/6 √ 33/20 — P89C54X2 — — 16 256 3 — 6 2 4 √ √ 32 12/6 √ 33/20 — P89C58X2 — — 32 256 3 — 6 2 4 √ √ 32 12/6 √ 33/20 — 系 列 型 号 片内程序存储 器类型及容量 /KB 片 内RAM 容 量/B 定时器 中断资源 双DPTR 低EMI( 可 禁 止ALE 输 出) I/O 引 脚 数 时 钟/ 机 器 周 期 T2 可 编 程 时 钟 输 出 工 作 频 率/MHz(5.0 V) 工 作 频 率/MHz(2.7 ~5.5 V) ROM EPROM(OTP) Flash ROM 定 时/ 计 数 器 看 门 狗(WDT) 中 断 源 外 中 断 源 优 先 级 Philips P8XC5X P80C31 — — — 128 3 — 6 2 4 √ √ 32 12 √ 33 6 P80C32 — — — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P80C51 4 — — 128 3 — 6 2 4 √ √ 32 12 √ 33 16 P80C52 8 — — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P80C54 16 — — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P80C58 32 — — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P87C51 — 4 — 128 3 — 6 2 4 √ √ 32 12 √ 33 16 P87C52 — 8 — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P87C54 — 16 — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P87C58 — 32 — 256 3 — 6 2 4 √ √ 32 12 √ 33 16 P89C51 — — 4 128 3 — 6 2 4 √ √ 32 12 √ 33 — P89C52 — — 8 256 3 — 6 2 4 √ √ 32 12 √ 33 — P89C54 — — 16 256 3 — 6 2 4 √ √ 32 12 √ 33 — P89C58 — — 32 256 3 — 6 2 4 √ √ 32 12 √ 33 —

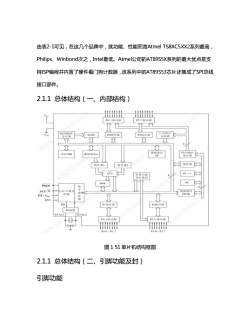

由表2-1可见,在这几个品牌中,就功能、性能而言AtmelTS8XC5XX2系列最高,Philips、Winbond次之,Intel最低。Atmel公司的AT89S5X系列的最大优点是支持ISP编程并内置了硬件看门狗计数器,该系列中的AT89S53芯片还集成了SPI总线接口部件。2.1.1 总体结构(一、内部结构)0O口动器大内捍PO锁在器P2锁存器T介介1介堆栈指计程序地加A等存器冷存器暂存器2智存器ALU特味功寄在器组PSWPSEN推优ALE/P时/针数及控EA/Vm存器RSTPI锁存器P3锁存器PD报高器P动p动zHh图151单片机结构框图2.1.1总体结构(二、引脚功能及封)引脚功能

由表2-1可见,在这几个品牌中,就功能、性能而言Atmel TS8XC5XX2系列最高, Philips、Winbond次之,Intel最低。Atmel公司的AT89S5X系列的最大优点是支 持ISP编程并内置了硬件看门狗计数器,该系列中的AT89S53芯片还集成了SPI总线 接口部件。 2.1.1 总体结构(一、内部结构) 图 1 51 单片机结构框图 2.1.1 总体结构(二、引脚功能及封) 引脚功能

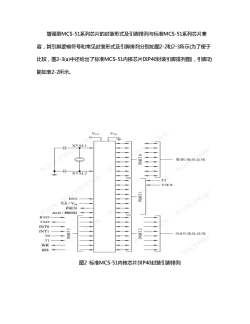

增强型MCS-51系列芯片的封装形式及引脚排列与标准MCS-51系列芯片兼容,其引脚逻辑符号和常见封装形式及引脚排列分别如图2-2和2-3所示(为了便于比较,图2-3(a)中还给出了标准MCS-51内核芯片DIP40封装引脚排列图),引脚功能如表2-2所示。数据/地址总线XTALT2T2EXO西安电子科技RSTEA/VppPSENALE/PROGRXDTXDINTOINTI高8位地址总线TOT1WRRD图2标准MCS-51内核芯片DIP40封装引脚排列

增强型MCS-51系列芯片的封装形式及引脚排列与标准MCS-51系列芯片兼 容,其引脚逻辑符号和常见封装形式及引脚排列分别如图2-2和2-3所示(为了便于 比较,图2-3(a)中还给出了标准MCS-51内核芯片DIP40封装引脚排列图),引脚功 能如表2-2所示。 图2 标准MCS-51内核芯片DIP40封装引脚排列

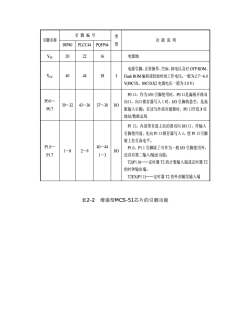

引脚编号类引脚名称功能说明型DIP40PLCC44PQFP4422Vss2016电源地电源引脚。正常操作、空闲、掉电以及对OTPROM、Vcc404438FlashROM编程或校验时的工作电压。一般为2.7~6.0V(89C5X、89C5XX2电源电压一般为5.0V)PO口:作为I/O引脚使用时,PO口是漏极开路双PO.0~:向口,向口锁存器写入1时,/O引脚将悬空,是高39~3243~3637~30I/OPO.7阻输入引脚;在读写外部存储器时,PO口作低8位地址/数据总线P1口:内部带有弱上拉的准双向I/O口,作输入引脚使用前,先向P1口锁存器写入1,使P1口引脚被上拉至高电平。PI.0~40~44P1.0、P1.1引脚除了可作为一般IVO引脚使用外,1~82~9IOP1.71~3还具有第二输入/输出功能:T2(P1.0)——定时器T2的计数输入端或定时器T2的时钟输出端。T2EX(P1.1)——定时器T2的外部触发输入端表2-2增强型MCS-51芯片的引脚功能

表2-2 增强型MCS-51芯片的引脚功能 引脚名称 引 脚 编 号 类 型 功 能 说 明 DIP40 PLCC44 PQFP44 VSS 20 22 16 电源地 VCC 40 44 38 I 电源引脚。正常操作、空闲、掉电以及对 OTP ROM、 Flash ROM编程或校验时的工作电压。一般为2.7~6.0 V(89C5X、89C5XX2 电源电压一般为 5.0 V) P0.0~ P0.7 39~32 43~36 37~30 I/O P0 口:作为 I/O 引脚使用时,P0 口是漏极开路双 向口,向口锁存器写入 1 时,I/O 引脚将悬空,是高 阻输入引脚;在读写外部存储器时,P0 口作低 8 位 地址/数据总线 P1.0~ P1.7 1~8 2~9 40~44 1~3 I/O P1 口:内部带有弱上拉的准双向 I/O 口,作输入 引脚使用前,先向 P1 口锁存器写入 1,使 P1 口引脚 被上拉至高电平。 P1.0、P1.1 引脚除了可作为一般 I/O 引脚使用外, 还具有第二输入/输出功能: T2(P1.0)——定时器 T2 的计数输入端或定时器 T2 的时钟输出端。 T2EX(P1.1)——定时器 T2 的外部触发输入端

引脚编号类引脚名称功能说明型DIP40PLCC44PQFP44复位信号输入端,高电平有效RST104低8位地址锁存信号。在访问外部存储器时,用ALE下降沿锁存从PO口输出的低8位地址信息A7~A0,以便随后将PO口作为数据总线使用。在正常情况下ALE输出信号恒定为1/6振荡频率,27ALE3033并可用作外部时钟或定时信号。注意:每次访问外部数据存储器时一个ALE脉冲将被忽略,ALE可以通过置位SFR的auxlilary.0位禁止ALE输出,这样,ALE只在执行MOVX指令时才被激活外部程序存储器读选通信号,低电平有效。从外部程序存储器取指令时,每个机器周期PSEN信293226PSEN号被激活两次。只有执行外部程序存储器中的指令时,PSEN才有效,而执行其他操作时PSEN无效外部程序存储器选择信号,低电平有效。在复位期间CPU检测并锁存EA/Vep引脚电平状态,当该引脚为高电平时,从片内程序存储器取指令,只有3529EAIVPP31当程序计数器PC超出片内程序存储器地址编码范围时,才转到外部程序存储器中取指令:当该引脚为低电平时,一律从外部程序存储器中取指令片内晶振电路反相放大器输入端,接CPU内部时192115XTALI钟电路XTAL2182014o片内晶振电路反相放大器输出端在增强型MCS-51芯片中,CPU引脚功能与CPU内特定单元电路有关,如:与振荡电路有关的引脚为XTAL1和XTAL2。与复位电路有关的引脚为RST。2.2存储器组织8XC5X系列单片机存储器系统由三部分组成:程序存储器(内部程序存储器、外部程序存储器)容量为64KB,地址编码范围为0000H~FFFFH),片内数据存储器(包括00H~FFH共256字节的内部RAM

在增强型 MCS-51 芯片中,CPU 引脚功能与 CPU 内特定单元电路有关,如:与振 荡电路有关的引脚为 XTAL1 和 XTAL2。与复位电路有关的引脚为 RST。 2.2 存储器组织 8XC5X 系列单片机存储器系统由三部分组成: 程序存储器(内部程序存储器、外部程序存储器)容量为 64 KB,地址编码范 围为 0000H~FFFFH),片内数据存储器(包括 00H~FFH 共 256 字节的内部 RAM EA/VPP 31 35 29 I 外部程序存储器选择信号,低电平有效。在复位 期间 CPU 检测并锁存 PP EA/V 引脚电平状态,当该 引脚为高电平时,从片内程序存储器取指令,只有 当程序计数器 PC 超出片内程序存储器地址编码范 围时,才转到外部程序存储器中取指令;当该引脚 为低电平时,一律从外部程序存储器中取指令 XTAL1 19 21 15 I 片内晶振电路反相放大器输入端,接 CPU 内部时 钟电路 XTAL2 18 20 14 O 片内晶振电路反相放大器输出端 引脚名称 引 脚 编 号 类 型 功 能 说 明 DIP40 PLCC44 PQFP44 RST 9 10 4 I 复位信号输入端,高电平有效 ALE 30 33 27 O 低 8 位地址锁存信号。在访问外部存储器时,用 ALE 下降沿锁存从 P0 口输出的低 8 位地址信息 A7~A0,以便随后将 P0 口作为数据总线使用。 在正常情况下ALE 输出信号恒定为1/6 振荡频率, 并可用作外部时钟或定时信号。注意:每次访问外 部数据存储器时一个 ALE 脉冲将被忽略,ALE 可以 通过置位 SFR 的 auxlilary.0 位禁止 ALE 输出,这样, ALE 只在执行 MOVX 指令时才被激活 PSEN 29 32 26 O 外部程序存储器读选通信号,低电平有效。从 外部程序存储器取指令时,每个机器周期 PSEN 信 号被激活两次。只有执行外部程序存储器中的指令 时, PSEN 才有效,而执行其他操作时 PSEN 无效

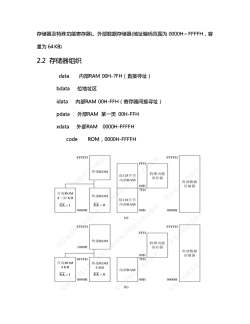

存储器及特殊功能寄存器)。外部数据存储器(地址编码范围为0000H~FFFFH,容量为64KB)2.2 存储器组织data内部RAMOOH-7FH(直接寻址)bdata位地址区idata内部RAMOOH-FFH(寄存器间接寻址)pdata外部RAM某一页OOH-FFHxdata外部RAM(OOOOH-FFFFHcodeROM, O00OH-FFFFHFFFFHFFFFHFFH外部ROM特殊功能高128字节寄存器内部RAM外部数据80H存储器7FH片内ROM外部ROM4~32KB低128字节内部RAMEA=1EA=00000H0000HOOH(a)安电子科技大FFFFHFFFFHFFH西安电子外部ROM特殊功能1000H寄存器外部数据80H存储器OFFFH7FH片内ROM外部ROM4KB4KB内部RAMEA=0EA=10000H00H0000H(b)

存储器及特殊功能寄存器)。外部数据存储器(地址编码范围为 0000H~FFFFH,容 量为 64 KB) 2.2 存储器组织 data 内部RAM 00H-7FH(直接寻址) bdata 位地址区 idata 内部RAM 00H-FFH(寄存器间接寻址) pdata 外部RAM 某一页 00H-FFH xdata 外部RAM 0000H-FFFFH code ROM,0000H-FFFFH

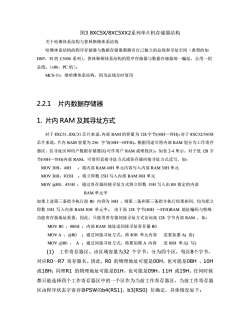

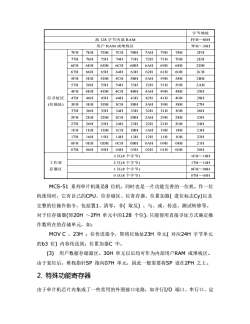

图38XC5X/8XC5XX2系列单片机存储器结构关于哈佛体系结构与普林斯顿体系结构哈佛体系结构的程序存储器与数据存储器都拥有自已独立的总线和寻址空间(典型的如DSP,TI的C5000系列),普林斯顿体系结构的程序存储器与数据存储器统一编址,公用一组总线:(x86,PC机)。MCS-51:准哈佛体系结构,因为总线分时复用2.2.1片内数据存储器1.片内RAM及其寻址方式对于8XC51、8XC31芯片来说,内部RAM的容量为128字节(00H~7FH):对于8XC52/54/58芯片来说,片内RAM容量为256字节(00H~0FFH)。根据用途可将内部RAM划分为工作寄存器区、位寻址区和用户数据存储器区(可作用户RAM或堆栈区),如表2-4所示。对于低128字节(O0H~7FH)内部RAM,可使用直接寻址方式或寄存器间接寻址方式读写,如:MOV30H,40H;将内部RAM40H单元内容写入内部RAM30H单元MOV30H,#35H;将立即数35H写入内部RAM30H单元MOV@R0,#35H:通过寄存器间接寻址方式将立即数35H写入由R0指定的内部RAM单元中如果上述第三条指令执行前R0内容为30H,则第二条和第三条指令执行结果相同,均为把立即数35H写入内部RAM30H单元中。由于高128字节(80HFFH)RAM地址编码与特殊功能寄存器地址重叠,因此,只能用寄存器间接寻址方式访问高128字节内部RAM,如:MOVRO,#8OH:内部RAM地址送间接寻址寄存器ROMOVA,@RO;通过间接寻址方式,将80H单元内容送累加器A(读)MOV@RO,A;通过间接寻址方式,将累加器A内容送80H单元(写)(1)工作寄存器区。该区域容量为32个字节,分为四个区,每区8个字节,对应R0~R7寄存器名。因此,R0的物理地址可能是00H,也可能是08H、10H或18H;同理R1的物理地址可能是01H,也可能是09H、11H或19H。任何时候都只能选择四个工作寄存器区中的一个区作为当前工作寄存器区,当前工作寄存器区由程序状态字寄存器PSW的b4(RS1)、b3(RSO)位确定,具体情况如下:

图3 8XC5X/8XC5XX2系列单片机存储器结构 关于哈佛体系结构与普林斯顿体系结构 哈佛体系结构的程序存储器与数据存储器都拥有自己独立的总线和寻址空间(典型的如 DSP,TI 的 C5000 系列),普林斯顿体系结构的程序存储器与数据存储器统一编址,公用一组 总线;(x86,PC 机)。 MCS-51:准哈佛体系结构,因为总线分时复用 2.2.1 片内数据存储器 1. 片内 RAM 及其寻址方式 对于 8XC51、8XC31 芯片来说,内部 RAM 的容量为 128 字节(00H~7FH);对于 8XC52/54/58 芯片来说,片内 RAM 容量为 256 字节(00H~0FFH)。根据用途可将内部 RAM 划分为工作寄存 器区、位寻址区和用户数据存储器区(可作用户 RAM 或堆栈区),如表 2-4 所示。对于低 128 字 节(00H~7FH)内部 RAM,可使用直接寻址方式或寄存器间接寻址方式读写,如: MOV 30H,40H ;将内部 RAM 40H 单元内容写入内部 RAM 30H 单元 MOV 30H,#35H ;将立即数 35H 写入内部 RAM 30H 单元 MOV @R0,#35H ;通过寄存器间接寻址方式将立即数 35H 写入由 R0 指定的内部 RAM 单元中 如果上述第三条指令执行前 R0 内容为 30H ,则第二条和第三条指令执行结果相同,均为把立 即数 35H 写入内部 RAM 30H 单元中。 由于高 128 字节(80H ~FFH)RAM 地址编码与特殊 功能寄存器地址重叠,因此,只能用寄存器间接寻址方式访问高 128 字节内部 RAM ,如: MOV R0 ,#80H ;内部 RAM 地址送间接寻址寄存器 R0 MOV A ,@R0 ;通过间接寻址方式,将 80H 单元内容 送累加器 A( 读) MOV @R0 , A ;通过间接寻址方式,将累加器 A 内容 送 80H 单元( 写) (1) 工作寄存器区。该区域容量为32 个字节,分为四个区,每区8个字节, 对应R0~R7 寄存器名。因此,R0 的物理地址可能是00H,也可能是08H 、10H 或18H;同理R1 的物理地址可能是01H,也可能是09H、11H 或19H。任何时候 都只能选择四个工作寄存器区中的一个区作为当前工作寄存器区,当前工作寄存器 区由程序状态字寄存器PSW的b4(RS1)、b3(RS0) 位确定,具体情况如下:

PSW寄存器b4、b3位当前工作寄存器区寄存器R7~RO地址000区07H~00H011区OFH08H102 区17H~10H113区1FH ~~18H由于复位后PSW的b4、b3位为00,因此复位后将选择0区作为当前工作寄存器区。修改PSW的b4、b3位即可选择不同的工作寄存器区,这有利于快速保护现场,提高程序执行效率和中断的响应速度。(2)位寻址区。20H~2FH单元属位寻址区,共16字节。该区域可按字节读/写,也可按位读/写。位地址从20H单元开始,20H单元b0位的位地址为00H,20H单元b1位的位地址为01H,20H单元b2位的位地址为02H。依此类推,21H单元b0位的位地址为08H,2FH单元b7位的位地址为7FH如表2-4所如果系统中需要位操作,则最好保留20H~2FH单元的部分或全部作位存储区以方便位寻址操作。内部RAM地址空间的区域划分

PSW寄存器b4、b3位 当前工作寄存器区 寄存器R7~R0地址 00 0 区 07H~00H 01 1 区 0FH ~08H 10 2 区 17H ~10H 11 3 区 1FH ~18H 由于复位后PSW 的b4 、b3 位为00 ,因此复位后将选择0 区作为当前工 作寄存器区。修改PSW 的b4 、b3 位即可选择不同的工作寄存器区,这有利于快 速保护现场,提高程序执行效率和中断的响应速度。 (2) 位寻址区。20H~2FH 单元属位寻址区,共16 字节。该区域可按字节读 /写,也可按位读/写。位地址从20H 单元开始,20H 单元b0 位的位地址为00H , 20H 单元b1 位的位地址为01H,20H单元b2位的位地址为02H。依此类推,21H 单元b0 位的位地址为08H,2FH 单元b7 位的位地址为7FH 如表2-4 所如果系 统中需要位操作,则最好保留20H ~2FH 单元的部分或全部作位存储区以方便位 寻址操作。内部RAM地址空间的区域划分

字节地址高128字节内部RAMFFH~80H用户RAM或堆栈区7FH~30H7DH7FH7EH7CH7BH7AH79H78H2FH76H74H72H71H70H77H75H73H2EH6FH6EH6DH6CH6BH6AH69H68H2DH66H62H60H2CH67H65H64H63H61H5AH59H2BH5FH5EH5DH5CH5BH58H57H56H55H54H53H52H51H50H2AH4FH4EH4DH4CH4BH4AH49H48H29H位寻址区47H46H45H44H43H42H41H40H28H27H(位地址)3FH3EH3DH3CH3BH3AH39H38H37H36H35H34H33H32H31H30H26H2FH25H2EH2DH2CH2BH2AH29H28H27H26H24H23H22H24H25H21H20H1FH1EH1DH1CH1BH1AH19H18H23H22H17H16H15H14H13H12H11H10HOFHOEHODHOCHOBHOAH09H08H21H20H07H06H05H04H03H02H01H00H3区(8个字节)1FH~18H工作寄2区(8个字节)17H~10H存器区1区(8个字节)0FH~08H0区(8个字节)07H~00HMCS-51系列单片机既是8位机,同时也是一片功能完善的一位机。作一位机使用时,它有自己的CPU、位存储区、位寄存器、位累加器(进位标志Cy)以及完整的位操作指令,包括置1、清零,非(取反)、与、或、传送、测试转移等对于位存储器(即20H~2FH单元中的1283个位),只能使用直接寻址方式确定操作数所在的存储单元,如:MOVC,23H:位传送指令,即将位地址23H单元(对应24H字节单元的b3位)内容传送到:位累加器C中。(3)用户数据存储器区。30H单元以后均可作为内部用户RAM或堆栈区。由于复位后,堆栈指针SP指向O7H单元,因此一般需要将SP设在2FH之上。2.特殊功能寄存器由于单片机芯片内集成了一些常用的外围接口电路,如并行I/O端口、串行口、定

MCS-51 系列单片机既是8 位机,同时也是一片功能完善的一位机。作一位 机使用时,它有自己的CPU、位存储区、位寄存器、位累加器( 进位标志Cy)以及 完整的位操作指令,包括置1、清零,非( 取反) 、与、或、传送、测试转移等。 对于位存储器(即20H ~2FH 单元中的128 个位),只能使用直接寻址方式确定操 作数所在的存储单元,如: MOV C ,23H ;位传送指令,即将位地址23H 单元( 对应24H 字节单元 的b3 位) 内容传送到;位累加器C 中。 (3) 用户数据存储器区。30H 单元以后均可作为内部用户RAM 或堆栈区。 由于复位后,堆栈指针SP 指向07H 单元,因此一般需要将SP 设在2FH 之上。 2. 特殊功能寄存器 由于单片机芯片内集成了一些常用的外围接口电路,如并行I/O 端口、串行口、定 字节地址 高 128 字节内部 RAM FFH~80H 用户 RAM 或堆栈区 7FH~30H 位寻址区 (位地址) 7FH 7EH 7DH 7CH 7BH 7AH 79H 78H 2FH 77H 76H 75H 74H 73H 72H 71H 70H 2EH 6FH 6EH 6DH 6CH 6BH 6AH 69H 68H 2DH 67H 66H 65H 64H 63H 62H 61H 60H 2CH 5FH 5EH 5DH 5CH 5BH 5AH 59H 58H 2BH 57H 56H 55H 54H 53H 52H 51H 50H 2AH 4FH 4EH 4DH 4CH 4BH 4AH 49H 48H 29H 47H 46H 45H 44H 43H 42H 41H 40H 28H 3FH 3EH 3DH 3CH 3BH 3AH 39H 38H 27H 37H 36H 35H 34H 33H 32H 31H 30H 26H 2FH 2EH 2DH 2CH 2BH 2AH 29H 28H 25H 27H 26H 25H 24H 23H 22H 21H 20H 24H 1FH 1EH 1DH 1CH 1BH 1AH 19H 18H 23H 17H 16H 15H 14H 13H 12H 11H 10H 22H 0FH 0EH 0DH 0CH 0BH 0AH 09H 08H 21H 07H 06H 05H 04H 03H 02H 01H 00H 20H 工作寄 存器区 3 区(8 个字节) 1FH~18H 2 区(8 个字节) 17H~10H 1 区(8 个字节) 0FH~08H 0 区(8 个字节) 07H~00H

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《微型计算机技术及应用》课程授课教案(讲义)第5章 51单片机的外围模块及应用 5.1 并口.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第3章 C51基本语法.doc

- 《微型计算机技术及应用》课程教学大纲 Microcomputer Principle and Its Applications.pdf

- 《数据结构》课程作业习题(无答案).pdf

- 《数据结构》课程实验指导.pdf

- 《力学》课程教学资源(PPT课件)实验力学——静态测量.ppt

- 《力学》课程教学资源(PPT课件)工程力学——杆件的内力.ppt

- 《力学》课程教学资源(PPT课件)材料力学——扭转.ppt

- 《力学》课程教学资源(作业习题)工程力学试题(样卷,含参考答案).doc

- 《力学》课程教学资源(作业习题)材料力学试题(样卷,含答案).doc

- 《力学》课程教学资源(作业习题)材料力学习题解.doc

- 《力学》课程教学资源(作业习题)动力学试题(无答案).pdf

- 《力学》课程教学资源(作业习题)运动学模拟试题(无答案).pdf

- 《力学》课程教学资源(作业习题)静力学测验(无答案).pdf

- 《C语言程序设计》课程教学课件(PPT讲稿)第十章 指针.ppt

- 《C语言程序设计》课程教学课件(PPT讲稿)第八章 函数.ppt

- 《C语言程序设计》课程教学课件(PPT讲稿)第九章 预处理命令.ppt

- 《C语言程序设计》课程教学课件(PPT讲稿)第五章 选择结构程序设计.ppt

- 《C语言程序设计》课程教学课件(PPT讲稿)第七章 数组.ppt

- 《C语言程序设计》课程教学课件(PPT讲稿)第六章 循环控制.ppt

- 《微型计算机技术及应用》课程授课教案(讲义)第5章 51单片机的外围模块及应用 5.2 定时器及其应用.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第1章 单片微型计算机基础知识.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第5章 51单片机的外围模块及应用 5.3 串口UART.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第7章 C51应用程序设计.doc

- 《微型计算机技术及应用》课程教学实验指导书(内蒙古科技大学:李琦,共十七个实验).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷A(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷A(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷B(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷B(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2010-2011单片机原理及应用试卷(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2011-2012微型计算机原理及应用试卷A(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2011-2012微型计算机原理及应用试卷A(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)67106309A卷(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)67106309A卷(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2010-2011单片机原理及应用试卷(试题).doc

- 《微型计算机技术及应用》课程授课教案(讲义)第6章 单片机接口技术.doc

- 《微型计算机技术及应用》课程教学资源(书籍文献)Keil与proteus完美结合教程.pdf

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第3章 C51基本语法.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第5章 MCS-51单片机的外围模块及应用 5.1 并口.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第5章 MCS-51单片机的外围模块及应用 5.2 定时器及其应用.ppt