《微型计算机技术及应用》课程授课教案(讲义)第6章 单片机接口技术

第6章单片机接口技术PO口、P2口可以作为并行扩展总线口使用,可扩展64KB的程序存储器和64KB的数据存储器(RAM或I/O口)本章将系统扩展原理、扩展器件、设备接口技术结合在一起,综合介绍单片机的接口技术和程序设计方法。重点是O口扩展和设备的接口与编程。6.151系列单片机并行扩展原理6.1.1大系统的扩展总线和扩展原理一、大系统(large)对于硬件需求量大,外部存储器空间被充分利用的应用系统,其系统结构规模大,我们之为大系统。在大系统中,PO口和P2口都作为总线口使用,不能作为第一功能的I/O接口连接外部设备。DPTR、RO、R1都可以作为访问外部数据存储器的地址指针,外部变量用xdata定义。二、大系统总线时序大系统中PO口、P2口作为扩展总线口。P2口输出高8位地址A8~A15,P0口输出低8位地址A0~A7,同时作为双向数据总线D0~D7。控制总线PSEN,RD(P3.7)、WR(P3.6),以及ALE。图6-1-1给出了大系统中CPU访问外部存储器的时序波形

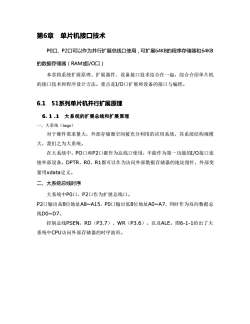

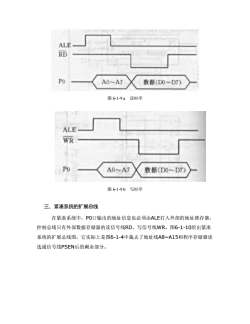

第6章 单片机接口技术 P0口、P2口可以作为并行扩展总线口使用,可扩展64KB的程序存储器和64KB 的数据存储器(RAM或I/O口) 本章将系统扩展原理、扩展器件、设备接口技术结合在一起,综合介绍单片机 的接口技术和程序设计方法。重点是I/O口扩展和设备的接口与编程。 6.1 51系列单片机并行扩展原理 6. 1 .1 大系统的扩展总线和扩展原理 一、大系统(large) 对于硬件需求量大,外部存储器空间被充分利用的应用系统,其系统结构规模 大,我们之为大系统。 在大系统中,PO口和P2口都作为总线口使用,不能作为第一功能的I/O接口连 接外部设备。DPTR、R0、R1都可以作为访问外部数据存储器的地址指针,外部变 量用xdata定义。 二、大系统总线时序 大系统中P0口、P2口作为扩展总线口。 P2口输出高8位地址A8~A15,P0口输出低8位地址A0~A7,同时作为双向数据总 线D0~D7。 控制总线PSEN,RD(P3.7)、WR(P3.6),以及ALE。图6-1-1给出了大 系统中CPU访问外部存储器的时序波形

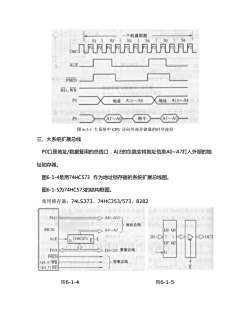

机器摄S5SPile2TPPPllP2oscTALEPSENRD.WRP2地址A15~A8地址A15-A8指全PO图6-1-1大系统中CPU访问外部存储器的时序波形三、大系统扩展总线PO口是地址/数据复用的总线口,ALE的负跳变将地址信息AO~A7打入外部的地址锁存器。图6-1-4是用74HC573作为地址锁存器的系统扩展总线图。图6-1-5为74HC573的结构框图。常用锁存器:74LS373、74HC353/573、8282P20>A8~A15地址总线89C52A0~A7DOO7INSOUIALEG74HC573EQD7ADO~D7数据总线PO口PSEN控制总线(p3.6)WR(p3.7)RD图6-1-5图6-1-4

图 6-1-1 大系统中 CPU 访问外部存储器的时序波形 三、大系统扩展总线 P0口是地址/数据复用的总线口,ALE的负跳变将地址信息A0~A7打入外部的地 址锁存器。 图6-1-4是用74HC573 作为地址锁存器的系统扩展总线图。 图6-1-5为74HC573的结构框图。 常用锁存器:74LS373、74HC353/573、8282 图6-1-4 图6-1-5

四、大系统地址译码方法单片机中CPU是根据地址访问外部存储器的,即由地址总线上地址信息选中某一芯片的某个单元进行读或写。在逻辑上,芯片选择信号线一般是由高位地址线译码产生的,而芯片中的单元选择是由低位地址确定。地址译码方法有线选法和全地址译码法两种。1、线选法所谓线选法就是用某一位地址线作为片选线,一般芯片的选片信号为低电平有效(如:CS、CE),只要这一位地址线为低电平,就选中该芯片进行读写。若外部扩展的芯片中最多的单元地址线为AO~Ai,则可以作为选片的地址线为A15~Ai+1。例如:i=12,则只有A15、A14、A13可以作为选片线。图6-1-6中A15作为CS0、A14作为CS1、A13作为CS2,分别接到0、1#、2#芯片的选片端。不管芯片中有多少个单元,所占的地址空间一样大,可以用如下方法确定芯片中单元地址:芯片中未用到的地址线为1,用到的地址线由所访问的芯片和单元确定

四、大系统地址译码方法 单片机中CPU是根据地址访问外部存储器的,即由地址总线上地址信息选中某 一芯片的某个单元进行读或写。 在逻辑上,芯片选择信号线一般是由高位地址线译码产生的,而芯片中的单元选 择是由低位地址确定。 地址译码方法有线选法和全地址译码法两种。 1、线选法 所谓线选法就是用某一位地址线作为片选线,一般芯片的选片信号为低电平有 效(如:CS、CE),只要这一位地址线为低电平,就选中该芯片进行读写。 若外部扩展的芯片中最多的单元地址线为A0~Ai,则可以作为选片的地址线为 A15~Ai+1。例如:i=12,则只有A15、A14、A13可以作为选片线。 图6-1-6中A15作为CS0、A14作为CS1、A13作为CS2,分别接到0 #、1 #、2 # 芯片的选片端。不管芯片中有多少个单元,所占的地址空间一样大,可以用如下方 法确定芯片中单元地址:芯片中未用到的地址线为1,用到的地址线由所访问的芯 片和单元确定

ACA00#芯片CSA15AlA1CSO)A2(6000H~7FFFH)A2A9AI1芯片aCSA14(CSD)CA000H~BEFFHDA12A12ACAo2芯片CSA13AA(CS2)(COOOH~DFFFH)1图 6-1-62.地址译码法线选法的优点是接线简单,缺点是外部存储器的地址空间没有被充分利用,可以接的芯片少。如在图6-1-6中,3个芯片总共有(8192+4+8)个单元,却占用了64K空间。可以用对高位地址译码方法克服这个缺点。常用地址译码器为:2--4译码器74HC139对A15、A14译码产生4个选片信号线,接4个芯片,每个芯片占16K字节空间;3--8译码器74HC138对A15、A14、A13译码产生8个选片信号,可接8个芯片,每个芯片占8K字节空间(见图6-1-8)。实际使用中常常将线选法和译码法结合起来使用

图 6-1-6 2.地址译码法 线选法的优点是接线简单,缺点是外部存储器的地址空间没有被充分利用,可 以接的芯片少。 如在图6-1-6中,3个芯片总共有(8192+4+8)个单元,却占用了64K空间。 可以用对高位地址译码方法克服这个缺点。常用地址译码器为: 2-4译码器74HC139对A15、A14译码产生4个选片信号线,接4个芯片,每个 芯片占16K字节空间; 3-8译码器74HC138对A15、A14、A13译码产生8个选片信号,可接8个芯片, 每个芯片占8K字节空间(见图6-1-8 )。 实际使用中常常将线选法和译码法结合起来使用

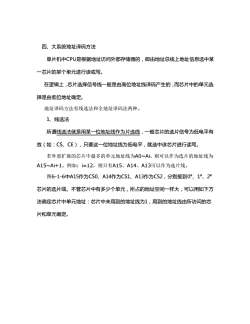

AoAc0芯片MA2Y.CS(1FF8H-IFPFH)AA13AYAOACCS1芯片A1A15B(2000H~3FFFH)主Y.A12A12cA15Y.地1GY.2GY.+5VGY.AC--AO2芯片YIA1AI(FFFCH~FFFFH)74LS138图6-1-86.1.2紧凑系统的扩展总线和扩展原理、紧凑系统(compact)和小系统(small)由于单片机内部资源种类和数量的增加,目前大多数的单片机应用系统不需要大规模地扩展外部存储器,尤其是不需要扩展程序存储器,对于只扩展少量数据存储器(RAM/IO口)的系统,我们称之为紧凑系统(compact)。在紧凑系统中,只用PO口作为扩展总线口,P2口可以作为第一功能的准双向口使用,连接/O设备,也可以将部分口线作为地址线。这种系统中,为了不影P2口所连的设备,CPU访问外部数据存储器时,不能用DPTR作地址指针,只能用RO、R1作为地址指针,外部变量用pdata定义,把P2、PO口不作为总线口使用的系统称为小系统(small).二、紧凑系统总线时序在紧凑系统中,PO中作为地址A0~A7和数据D0~D7复用的总线口,WR(P3.6)、RD(P3.7)作为外部数据存储器的写信号线和读信号线,ALE作为地址A0~A7的锁存信号。图6-1-9给出了紧凑系统中CPU访问外部数据存储器的时序波形

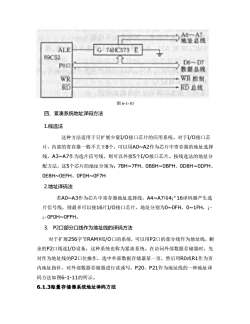

图 6-1-8 6.1.2 紧凑系统的扩展总线和扩展原理 一、紧凑系统(compact)和小系统(small) 由于单片机内部资源种类和数量的增加,目前大多数的单片机应用系统不需 要大规模地扩展外部存储器,尤其是不需要扩展程序存储器,对于只扩展少量数据 存储器(RAM/IO 口)的系统,我们称之为紧凑系统(compact)。 在紧凑系统中,只用P0口作为扩展总线口,P2口可以作为第一功能的准双向口 使用,连接I/O设备,也可以将部分口线作为地址线。 这种系统中,为了不影P2口所连的设备,CPU访问外部数据存储器时,不能用 DPTR作地址指针,只能用R0、R1作为地址指针,外部变量用pdata定义。 把P2、P0口不作为总线口使用的系统称为小系统(small). 二、紧凑系统总线时序 在紧凑系统中,P0中作为地址A0~A7和数据D0~D7复用的总线口,WR (P3.6)、RD(P3.7)作为外部数据存储器的写信号线和读信号线,ALE作为地 址A0~A7的锁存信号。 图6-1-9给出了紧凑系统中CPU访问外部数据存储器的时序波形

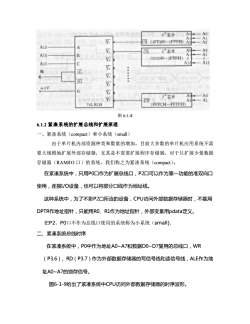

ALERDPoA0~A7数据(DO~D7)图6-1-9a读时序ALEWRPOA0~A7数据(DO~D7)图 6-1-9b写时序三、紧凑系统的扩展总线在紧凑系统中,PO口输出的地址信息也必须由ALE打入外部的地址锁存器,控制总线只有外部数据存储器的读信号线RD、写信号线WR。图6-1-10给出紧凑系统的扩展总线图,它实际上是图6-1-4中裁去了地址线A8~A15和程序存储器读选通信号线PSEN后的剩余部分

图 6-1-9 a 读时序 图 6-1-9 b 写时序 三、紧凑系统的扩展总线 在紧凑系统中,P0口输出的地址信息也必须由ALE打入外部的地址锁存器, 控制总线只有外部数据存储器的读信号线RD、写信号线WR。图6-1-10给出紧凑 系统的扩展总线图,它实际上是图6-1-4中裁去了地址线A8~A15和程序存储器读 选通信号线PSEN后的剩余部分

A0~A7地址总线ALEDG74HC573EB9C52介DO~D7POD数据总线WR控制WRRDRD总线图6-1-10四、紧凑系统地址译码方法1.线选法这种方法适用于只扩展少量I/O接口芯片的应用系统。对于I/O接口芯片,内部的寄存器一般不大于8个,可以用A0~A2作为芯片中寄存器的地址选择线,A3~A7作为选片信号线,则可以外接5个I/O接口芯片。按线选法的地址分配方法,这5个芯片的地址分别为:78H~7FH、0B8H~0BFH、0D8H~0DFH、OE8H~OEFH、OFOH~OF7H2.地址译码法若A0~A3作为芯片中寄存器地址选择线,A4~A7用416译码器产生选片信号线,则最多可以接16片I/O接口芯片,地址分别为0~0FH,0~1FH,i-i-OFOH~OFFH。3.P2口部分口线作为地址线的译码方法对于扩展256字节RAM和I/O口的系统,可以用P2口的部分线作为地址线,剩余的P2口线连I/O设备,这种系统也称为紧凑系统。在访问外部数据存储器时,先对作为地址线的P2口位操作,选中外部数据存储器某一页,然后用RO或R1作为页内地址指针,对外部数据存储器进行读或写,P20、P21作为地址线的一种地址译码方法如图6-1-11的所示。6.1.3海量存储器系统地址译码方法

图 6-1-10 四、紧凑系统地址译码方法 1.线选法 这种方法适用于只扩展少量I/O接口芯片的应用系统。对于I/O接口芯 片,内部的寄存器一般不大于8个,可以用A0~A2作为芯片中寄存器的地址选择 线,A3~A7作为选片信号线,则可以外接5个I/O接口芯片。按线选法的地址分 配方法,这5个芯片的地址分别为:78H~7FH、0B8H~0BFH、0D8H~0DFH、 0E8H~0EFH、0F0H~0F7H 2.地址译码法 若A0~A3作为芯片中寄存器地址选择线,A4~A7用4¡ª16译码器产生选 片信号线,则最多可以接16片I/O接口芯片,地址分别为0~0FH,0~1FH,¡ ¡0F0H~0FFH。 3. P2口部分口线作为地址线的译码方法 对于扩展256字节RAM和I/O口的系统,可以用P2口的部分线作为地址线,剩 余的P2口线连I/O设备,这种系统也称为紧凑系统。在访问外部数据存储器时,先 对作为地址线的P2口位操作,选中外部数据存储器某一页,然后用R0或R1作为页 内地址指针,对外部数据存储器进行读或写,P20、P21作为地址线的一种地址译 码方法如图6-1-11的所示。 6.1.3海量存储器系统地址译码方法

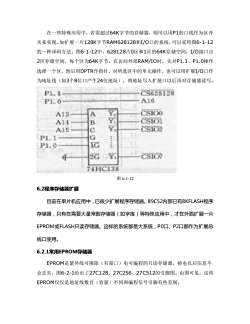

在一些特殊应用中,若需超过64K字节的存储器,则可以用P1的口线作为区开关来实现。如扩展一片128K字节RAM628128和I/0口的系统,可以采用图6-1-12的一种译码方法。图6-1-12中,628128占0区和1区的64K存储空间,I/O接口点2区存储空间,每个区为64K字节。在访问外部RAM/1O时,先对P1.1、P1.0操作选择一个区,然后用DPTR作指针,对所选区中的单元操作。也可以用扩展I/O口作为地址线(如3个8位口产生24位地址),将地址写入扩展口以后再对存储器读写。P1.1CS628128A16PL.0YoCSIODAA13YBCSIOIA14YeCSIO2A15GPL.1心at生1GP1.0Y2GCSIOT中74HC138图 6-1-126.2程序存储器扩展目前在单片机应用中,已很少扩展程序存储器。89C52内部已有8KFLASH程序存储器,只有在需要大量常数存储器(如字库)等特殊应用中,才在外面扩展一片EPROM或FLASH只读存储器。这样的系统都是大系统,PO口、P2口都作为扩展总线口使用。6.2.1常用EPROM存储器EPROM是紫外线可擦除(有窗口)电可编程的只读存储器,掉电以后信息不会丢失。图6-2-1给出了27C128、27C256、27C512的引脚图。由图可见,这些EPROM仅仅是地址线数目(容量)不同和编程信号引脚有些差别

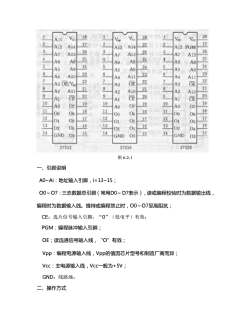

在一些特殊应用中,若需超过64K字节的存储器,则可以用P1的口线作为区开 关来实现。如扩展一片128K字节RAM628128和I/O口的系统,可以采用图6-1-12 的一种译码方法。图6-1-12中,628128占0区和1区的64K存储空间,I/O接口点 2区存储空间,每个区为64K字节。在访问外部RAM/IO时,先对P1.1、P1.0操作 选择一个区,然后用DPTR作指针,对所选区中的单元操作。也可以用扩展I/O口作 为地址线(如3个8位口产生24位地址),将地址写入扩展口以后再对存储器读写。 图 6-1-12 6.2程序存储器扩展 目前在单片机应用中,已很少扩展程序存储器。89C52内部已有8KFLASH程序 存储器,只有在需要大量常数存储器(如字库)等特殊应用中,才在外面扩展一片 EPROM或FLASH只读存储器。这样的系统都是大系统,P0口、P2口都作为扩展总 线口使用。 6.2.1常用EPROM存储器 EPROM是紫外线可擦除(有窗口)电可编程的只读存储器,掉电以后信息不 会丢失。图6-2-1给出了27C128、27C256、27C512的引脚图。由图可见,这些 EPROM仅仅是地址线数目(容量)不同和编程信号引脚有些差别

28128工1格Voe28MVmVrVocA15272227227A12A14A14A12PGMA12263326326A7A13A13A7A7A132542525A6A8A8A6A6A8245524245A5A9A9A5A5A9236623623A4A10A4AllA4All722772222OEA3OE/NmOEA3A38&2121821A2AllA10A2A10920992020CECEA1CEAAl101910191019O7AOO7AOOAO11111818181100O60606O0O0171212171217O5O1O5O1OS011316131316160204O4O20402151414151415GNDGND0303GND03275122712827256图 6-2-1一、引脚说明A0~Ai:地址输入引脚,i=13~15;O0~O7:三态数据总引脚(常用D0~D7表示),读或编程校验时为数据输出线,编程时为数据输入线。维持或编程禁止时,00~07呈高阻抗;CE:选片信号输入引脚,“O”(低电平)有效PGM:编程脉冲输入引脚;OE;读选通信号输入线,“O”有效;Vpp:编程电源输入线,Vpp的值因芯片型号和制造厂商而异;Vcc:主电源输入线,Vcc一般为+5V;GND:线路地。二、操作方式

图 6-2-1 一、引脚说明 A0~Ai:地址输入引脚,i=13~15; O0~O7:三态数据总引脚(常用D0~D7表示),读或编程校验时为数据输出线, 编程时为数据输入线。维持或编程禁止时,O0~O7呈高阻抗; CE:选片信号输入引脚,“0”(低电平)有效; PGM:编程脉冲输入引脚; OE;读选通信号输入线,“O”有效; Vpp:编程电源输入线,Vpp的值因芯片型号和制造厂商而异; Vcc:主电源输入线,Vcc一般为+5V; GND:线路地。 二、操作方式

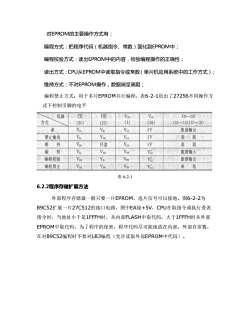

对EPROM的主要操作方式有:编程方式:把程序代码(机器指令、常数)固化到EPROM中;编程校验方式:读出EPROM中的内容,检验编程操作的正确性;读出方式:CPU从EPROM中读取指令或常数(单片机应用系统中的工作方式);维持方式:不对EPROM操作,数据端呈高阻;编程禁止方式:用于多片EPROM并行编程。表6-2-1给出了27256不同操作方式下控制引脚的电平CEOEVaVec引脚00~07方式(20)(22)(1)(28)(11~13)(1519)读VeVaVee5V数据输出Ve5V禁止输出VuVe高阳维持Va任意Voc5V高阻Vuve编程VVr数据输入VaVaVmVee程校验数据输出VaVuVrpVee高阳编程禁止表 6-2-16.2.2程序存储扩展方法外部程序存储器一般只要一片EPROM,选片信号可以接地。图6-2-2为89C52扩展一片27C512的接口电路,图中EA接+5V,CPU在取指令或执行查表指令时,当地址小于是1FFFH时,从内部FLASH中取代码,大于1FFFH时从外部EPROM中取代码。为了程序的保密,程序代码尽可能地放在内部,外部存常数,在对89C52编程时不要对LB3编程(允许读取外部EPROM中代码)

对EPROM的主要操作方式有: 编程方式:把程序代码(机器指令、常数)固化到EPROM中; 编程校验方式:读出EPROM中的内容,检验编程操作的正确性; 读出方式:CPU从EPROM中读取指令或常数(单片机应用系统中的工作方式); 维持方式:不对EPROM操作,数据端呈高阻; 编程禁止方式:用于多片EPROM并行编程。表6-2-1给出了27256不同操作方 式下控制引脚的电平 表 6-2-1 6.2.2程序存储扩展方法 外部程序存储器一般只要一片EPROM,选片信号可以接地。图6-2-2为 89C52扩展一片27C512的接口电路,图中EA接+5V,CPU在取指令或执行查表 指令时,当地址小于是1FFFH时,从内部FLASH中取代码,大于1FFFH时从外部 EPROM中取代码。为了程序的保密,程序代码尽可能地放在内部,外部存常数, 在对89C52编程时不要对LB3编程(允许读取外部EPROM中代码)

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《微型计算机技术及应用》课程教学资源(试卷习题)2010-2011单片机原理及应用试卷(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)67106309A卷(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)67106309A卷(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2011-2012微型计算机原理及应用试卷A(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2011-2012微型计算机原理及应用试卷A(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2010-2011单片机原理及应用试卷(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷B(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷B(答案).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷A(试题).doc

- 《微型计算机技术及应用》课程教学资源(试卷习题)2007试卷A(答案).doc

- 《微型计算机技术及应用》课程教学实验指导书(内蒙古科技大学:李琦,共十七个实验).doc

- 《微型计算机技术及应用》课程授课教案(讲义)第7章 C51应用程序设计.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第5章 51单片机的外围模块及应用 5.3 串口UART.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第1章 单片微型计算机基础知识.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第5章 51单片机的外围模块及应用 5.2 定时器及其应用.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第2章 51系列单片机系统结构.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第5章 51单片机的外围模块及应用 5.1 并口.doc

- 《微型计算机技术及应用》课程授课教案(讲义)第3章 C51基本语法.doc

- 《微型计算机技术及应用》课程教学大纲 Microcomputer Principle and Its Applications.pdf

- 《数据结构》课程作业习题(无答案).pdf

- 《微型计算机技术及应用》课程教学资源(书籍文献)Keil与proteus完美结合教程.pdf

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第3章 C51基本语法.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第5章 MCS-51单片机的外围模块及应用 5.1 并口.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第5章 MCS-51单片机的外围模块及应用 5.2 定时器及其应用.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第5章 MCS-51单片机的外围模块及应用 5.3 串口.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第2章 51系列单片机系统结构.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第1章 单片微型计算机基础知识.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第7章 C51应用程序设计.ppt

- 《微型计算机技术及应用》课程教学课件(PPT讲稿)第6章 MCS-51单片机接口技术.ppt

- 《分子生物学》课程授课教案(教学方案).doc

- 《计算机文化基础》课程教学大纲 computer culture base.pdf

- 《电子商务概论》课程教学大纲 Electronic Commerce conspectus.pdf

- 《电子商务概论》课程实验大纲 Electronic Commerce conspectus.pdf

- 《电子商务概论》课程教学资源(教案讲义)第六章 网络营销.pdf

- 《电子商务概论》课程教学资源(教案讲义)第七章 电子商务与物流.pdf

- 《电子商务概论》课程教学资源(教案讲义)第八章 商务网站概述.pdf

- 《电子商务概论》课程教学资源(教案讲义)第五章 网上支付与安全交易.pdf

- 《电子商务概论》课程教学资源(教案讲义)第三章 EDI商务.pdf

- 《电子商务概论》课程教学资源(教案讲义)第四章 企业电子商务应用.pdf

- 《电子商务概论》课程教学资源(教案讲义)第二章 电子商务交易模式.pdf