西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计C卷(试题)

共5页第1页 西安邮电学院课程考试试题(C卷) 2009 -一2010学年第一学期试题卷 课程名称:数字电路与逻辑设计 试卷类型:(AB0)0卷 专业、年级:通工/电子/计科/光值息07级 题号 三四五六 七八九总分 得分 阅卷人 一、填空(10分) 1、F=AB+C+A,则F的反函数(用反演规则)F= F的对偶式F 2、(13.25)=( )=( )a1码 =( 3、基本逻辑运算有 和 三种。 4、 对159个符号进行二进制编码,则至少需要 位二进制数 二、选择(20分) 注意:题中涉及到的中规模器件的功能表,附在试题的最后一页, 将正确答案填入下面答题栏中,所选的答案用横线划过,例如:士 2 345678910 选AAAA AA AAAA 择BBBBBBBBBB cccccccccc 案D DD DDDDDDD 说明:1。拟题请用碳塑最水钢笔书写。不要出框。除填空体、图解及特要求外一般不留答题空间

共 5 页 第 1 页 说明:1。 拟 题请用 碳塑 墨水钢 笔书写 。 不 要 出 框。 除 填 空体、 图解 及特要 求外 一般不 留答题 空间 。 - - 上- 装- 订- 线- 专业班级 姓名 学号(8 位) 西安邮电学院试题卷专用纸 - - 密- 封- 装- 订- 线- 西安邮电学院课程考试试题(C 卷) 2009-2010 学年第 一 学期试题卷 课程名称:数字电路与逻辑设计 试卷类型:(A B C)C 卷 专业、年级:通工/电子/计科/光信息 07 级 题号 一 二 三 四 五 六 七 八 九 总分 得分 阅 卷 人 一、填空(10 分) 1、 F = AB + C + A ,则 F 的反函数(用反演规则) F =_ _, F 的对偶式 * F = 。 2、 (13.25)10 = ( )16 = ( )8 = ( )8421BCD 码 = ( )余 3BCD 码 3、基本逻辑运算 有 、 和 三 种 。 4、对 159 个符号进行二进制编码,则至少需要 位二进制数。 二、选择(20 分) 注意:题中涉及到的中规模器件的功能表,附在试题的最后一页。 将正确答案填入下面答题栏中,所选的答案用横线划过,例如: 题 号 1 2 3 4 5 6 7 8 9 10 选 择 答 案 A A A A A A A A A A B B B B B B B B B B C C C C C C C C C C D D D D D D D D D D 2.( )要构成容量为 4K×8 的 RAM,需要 16 片容量为 256×8 的 RAM。 3.( )F = ,则 F 的反函数 4.( )N 个逻辑变量共有 2N 个最小项。 5. ( )时序逻辑电路在任意时刻输出信号仅取决于当时的输入信号

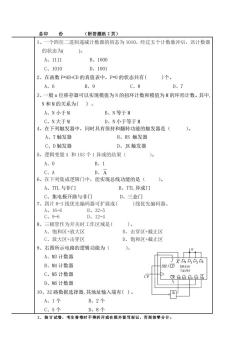

总印份 (附答题纸2页) 1、一个四位二进制递减计数器的初态为1010,经过五个计数脉冲后,该计数器 的状态为( 。 A、1111 B、1000 C、1010 D、1001 2、在函数F=AB+CD的真值表中,F=0的状态共有( )个。 A、6 B、9 C、8 D、7 3、一般位移存器可以实现模值为N的扭环计数和模值为M的环形计数。其中 N和M的关系为()。 A、N小于M B、N等于M CN大千M D、N小于等于M 4、在下列触发器中,同时具有保持和翻转功能的触发器是( )。 A、T触发器 B、RS触发器 C、D触发器 D、JK触发器 5、逻辑变量A和103个1异或的结果( )。 A、0 B、1 D、A 6、在下列集成逻辑门中,能实现总线功能的是( )。 A、TTL与非门 B、TTL异或 C、集电极开路与非门 D、三态门 7、四片8-3线优先编码器可扩展成( )线优先编码器。 A、16-6 B、32-5 C、9-6 D、12-4 8、三极管作为开关时工作区域是( )。 A、饱和区+放大区 B、击穿区+截止区 C、放大区+击穿区 D、饱和区+截止区 9、右图所示电路的逻辑功能为( A、M3计数器 B、4计数器 C、M5计数器 D、M6计数器 10、32路数据选择器,其地址输入端有()。 A、1个 B、2个 C、5个 D、8个 2.装订试卷, 考生答卷时不得拆开或在框外留写标记,否则按零分计

总印 份 (附答题纸 2 页) 1、一个四位二进制递减计数器的初态为 1010,经过五个计数脉冲后,该计数器 的状态为( )。 A、1111 B、1000 C、1010 D、1001 2、在函数 F=AB+CD 的真值表中,F=0 的状态共有( )个。 A、6 B、9 C、8 D、7 3、一般 n 位移存器可以实现模值为 N 的扭环计数和模值为 M 的环形计数。其中, N 和 M 的关系为( ) 。 A、N 小于 M B、N 等于 M C、N 大于 M D、N 小于等于 M 4、在下列触发器中,同时具有保持和翻转功能的触发器是( )。 A、T 触发器 B、RS 触发器 C、D 触发器 D、JK 触发器 5、逻辑变量 A 和 103 个 1 异或的结果( )。 A、0 B、1 C、A D、A 6、在下列集成逻辑门中,能实现总线功能的是( )。 A、TTL 与非门 B、TTL 异或门 C、集电极开路与非门 D、三态门 7、四片 8-3 线优先编码器可扩展成( )线优先编码器。 A、16-6 B、32-5 C、9-6 D、12-4 8、三极管作为开关时工作区域是( )。 A、饱和区+放大区 B、击穿区+截止区 C、放大区+击穿区 D、饱和区+截止区 9、右图所示电路的逻辑功能为( )。 A、M3 计数器 B、M4 计数器 C、M5 计数器 D、M6 计数器 10、32 路数据选择器,其地址输入端有( )。 A、1 个 B、2 个 C、5 个 D、8 个 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零 分 计

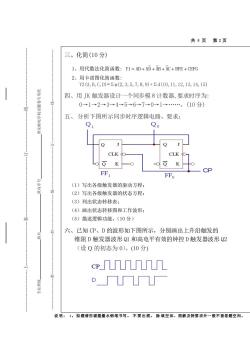

共5页第2页 三、化简(10分)》 1、用代数法化简函数:Y1=AD+AD+AB+AC+BFE+CEFG 2、用卡诺图化简函数: Y2(A,B,C,D)=Σm(2,3,5,7,8,9)+Σd(10,11,12,13,14,15) 四、用JK触发器设计一个同步模8计数器,要求时序为: 0→1→2→3一4→5→6→7→0→1→.。(10分) 五、分析下图所示同步时序逻辑电路。要求: Q Qo FF, FF (1)写出各级触发器的驱动方程: (2)写出各级触发器的状态方程 (3)列出状态转移表: (4)画出状态转移图和工作波形: (5)描述逻辑功能。(10分) 六、已知CP、D的波形如下图所示,分别画出上升沿触发的 维阻D触发器波形Q1和高电平有效的钟控D触发器波形Q2 (设Q的初态为0)。(10分) cp几几几几几几 1。拟题请用碳塑墨水钢笔书写,不要出框。除填空体、图解及特要求外一般不留答愿空间

共 5 页 第 2 页 说 明 : 1。 拟 题请用 碳塑墨 水钢 笔书写 。 不 要 出 框。 除 填 空 体、 图解 及特要 求外一 般不 留答题空 间。 - 上- 装- 订- 线- 专业班级 姓名 班内序号 西安邮电学院试题卷专用纸 - 密- 封- 装- 订- 线- 三、化简(10 分) 1、用代数法化简函数: Y1 = AD + AD + AB + AC + BFE + CEFG 2、用卡诺图化简函数: Y2(A,B,C,D)=Σm(2,3,5,7,8,9)+Σd(10,11,12,13,14,15) 四、用 JK 触发器设计一个同步模 8 计数器,要求时序为: 0→1→2→3→4→5→6→7→0→1→.。(10 分) 五、 分析下图所示同步时序逻辑电路。要求: (1)写出各级触发器的驱动方程; (2)写出各级触发器的状态方程; (3)列出状态转移表; (4)画出状态转移图和工作波形; (5)描述逻辑功能。(10 分) 六、已知 CP、D 的波形如下图所示,分别画出上升沿触发的 维阻 D 触发器波形 Q1 和高电平有效的钟控 D 触发器波形 Q2 (设 Q 的初态为 0)。(10 分)

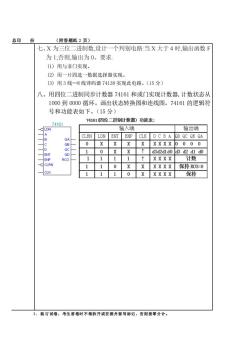

总印份 (附答趣纸2页) 七、X为三位二进制数,设计一个判别电路:当X大于4时,输出函数F 为1:否则,输出为0。要求 (1)用与非门实现。 (2)用一片四选一数据选择器实现。 (3)用3线一8线译码器74138实现此电路。(15分 八、用四位二进制同步计数器74161和或门实现计数器,计数状态从 1000到0000循环。画出状态转换图和连线图。74161的逻辑符 号和功能表如下。(15分) 74161四位二进计数器)功能表: 74161 输入端 输出端 CLRN I LDNI ENT I ENPI CLK I D C B A DD OC OB QA 0 X X X XXXX 0000 个d3d2dd0d3d2d1d0 XXXX 计数 1 1 0 XXXXX保持RC00 CLK 0 X XXXX 保持 2。骏订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计

总印 份 (附答题纸 2 页) 七、X 为三位二进制数,设计一个判别电路:当 X 大于 4 时,输出函数 F 为 1;否则,输出为 0。要求: (1) 用与非门实现。 (2) 用一片四选一数据选择器实现。 (3) 用 3 线—8 线译码器 74138 实现此电路。(15 分) 八、用四位二进制同步计数器 74161 和或门实现计数器,计数状态从 1000 到 0000 循环。画出状态转换图和连线图。74161 的逻辑符 号和功能表如下。(15 分) 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零 分 计

共5页第3页 3线一8线译码器74138真值表 STA STST A:AA万万万 X X X X 1 X X 0 X00 1 0 0 0 0 1 0 0 0 01111 0 74195功能表 入 输 出 CR SH/LD CP J K Do D1D2 D3 Qo Q1 Q2 Q3 Q 0 00001 ××d0d1d2d的 do dl d2 d3 d3 1 Q哈哈QQ贴Q贴 1 1 ↑00 0Q8QQ贴Q呀 1 ↑10×××× QQ贴Q赠Q贴Q贴 1↑11××XX 1Q阳QQ贴Q贴 Q片Q1Q3Q片Q片 4选1数据选择器真值表 A1 A Y 1 0 1 D 说明:1。拟题请用碳塑墨水钢笔书写,不要出框。除填空体、图解及特要求外一般不留答题空间

共 5 页 第 3 页 说 明 : 1。 拟 题请用 碳塑墨 水钢 笔书写 。 不 要 出 框。 除 填 空 体、 图解 及特要 求外一 般不 留答题空 间。 - 上- 装- 订- 线- 专业班级 姓名 班内序号 西安邮电学院试题卷专用纸 - 密- 封- 装- 订- 线- 11.分析下图的电路,设 Q1 端和 Q2 端的初态为零,Q1 端和 Q2 端的波形为: E. 以上答案都不对 12. 下图中 Q 端的状态方程为: A. Q D n = +1 B. n n n Q = Q J + K Q +1 C. n n Q = Q +1 D. n n Q = Q +1 E. 以上答案都不对 - 上- 装- 订- 线- 专业班级 姓名 班内序号 西安邮电学院试题卷专用纸 - 密- 封- 装- 订- 线- 3 线—8 线译码器 74138 真值表 STA STB STC A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 X 1 X X X X 1 1 1 1 1 1 1 1 X X 1 X X X 1 1 1 1 1 1 1 1 0 X X X X X 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 0 0 1 1 1 1 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 0 1 1 1 0 0 1 1 0 1 1 1 1 1 1 0 1 1 0 0 1 1 1 1 1 1 1 1 1 1 0 74195 功能表 4 选 1 数据选择器真值表

总印份 (附答趣纸2页) 2。装订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计

总印 份 (附答题纸 2 页) 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零 分 计

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计C卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计A卷(答案).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第九章 脉冲单元电路(2/2).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第九章 脉冲单元电路(1/2).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第八章 可编程逻辑器件及其应用.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第七章 半导体存储器.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第六章 时序逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第五章 集成触发器.doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)C卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计C卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计C卷(答案).doc

- 《电路》课程教学资源(A)动态电路试题及解答.pdf

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第12章 三相电路.ppt

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第5章 含有运算放大器的电阻电路.ppt

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第4章 电路定理.ppt

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第11章 电路的频率响应.ppt

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第10章 含有耦合电感的电路.ppt

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第9章 正弦稳态电路的分析.ppt